# AlphaServer 4000/4100

**Service Manual**

Order Number: EK-4100A-SV. B01

This manual is for anyone who services an AlphaServer 4000/4100 pedestal or cabinet system. It includes troubleshooting information, configuration rules, and instructions for removal and replacement of field-replaceable units (FRUs).

#### First Printing, June 1997

Digital Equipment Corporation makes no representations that the use of its products in the manner described in this publication will not infringe on existing or future patent rights, nor do the descriptions contained in this publication imply the granting of licenses to make, use, or sell equipment or software in accordance with the description.

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation.

Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software, if any, described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license. No responsibility is assumed for the use or reliability of software or equipment that is not supplied by Digital Equipment Corporation or its affiliated companies.

Copyright © 1997 by Digital Equipment Corporation. All rights reserved.

The following are trademarks of Digital Equipment Corporation: AlphaGeneration, AlphaServer, OpenVMS, StorageWorks, VAX, the AlphaGeneration logo, and the DIGITAL logo.

The following are third-party trademarks: Lifestyle 28.8 DATA/FAX Modem is a trademark of Motorola, Inc. UNIX is a registered trademark in the U.S. and other countries, licensed exclusively through X/Open Company Ltd. U.S. Robotics and Sportster are registered trademarks of U.S. Robotics. Windows NT is a trademark of Microsoft, Inc. All other trademarks and registered trademarks are the property of their respective holders.

**FCC Notice:** The equipment described in this manual generates, uses, and may emit radio frequency energy. The equipment has been type tested and found to comply with the limits for a Class A digital device pursuant to Part 15 of FCC Rules, which are designed to provide reasonable protection against such radio frequency interference. Operation of this equipment in a residential area may cause interference, in which case the user at his own expense will be required to take whatever measures are required to correct the interference.

**Shielded Cables:** If shielded cables have been supplied or specified, they must be used on the system in order to maintain international regulatory compliance.

**Warning!** This is a Class A product. In a domestic environment this product may cause radio interference, in which case the user may be required to take adequate measures.

Achtung! Dieses ist ein Gerät der Funkstörgrenzwertklasse A. In Wohnbereichen können bei Betrieb dieses Gerätes Rundfunkstörungen auftreten, in welchen Fällen der Benutzer für entsprechende Gegenmaßnahmen verantwortlich ist.

**Avertissement!** Cet appareil est un appareil de Classe A. Dans un environnement résidentiel, cet appareil peut provoquer des brouillages radioélectriques. Dans ce cas, il peut être demandé à l'utilisateur de prendre les mesures appropriées.

# **Contents**

| Prefa | ace                                    | xi   |

|-------|----------------------------------------|------|

| Cha   | pter 1 System Overview                 |      |

| 1.1   | AlphaServer 4100 System Drawer (BA30A) | 1-2  |

| 1.2   | AlphaServer 4000 System Drawer (BA30C) |      |

| 1.3   | AlphaServer 4100 System Drawer (BA30B) | 1-6  |

| 1.4   | Cabinet System                         | 1-8  |

| 1.5   | Pedestal System                        | 1-10 |

| 1.6   | Control Panel and Drives               | 1-12 |

| 1.7   | System Consoles                        | 1-14 |

| 1.8   | System Architecture                    | 1-16 |

| 1.9   | System Motherboard                     | 1-18 |

| 1.10  | CPU Types                              | 1-20 |

| 1.11  | Memory Modules                         | 1-22 |

| 1.12  | Memory Addressing                      | 1-24 |

| 1.13  | System Bus                             |      |

| 1.14  | System Bus to PCI Bus Bridge Module    | 1-28 |

| 1.15  | PCI I/O Subsystem                      | 1-30 |

| 1.16  | Server Control Module                  | 1-32 |

| 1.17  | Power Control Module                   | 1-34 |

| 1.18  | Power Supply                           | 1-36 |

| Cha   | pter 2 Power-Up                        |      |

| 2.1   | Control Panel                          | 2-2  |

| 2.2   | Power-Up Sequence                      | 2-4  |

| 2.3   | SROM Power-Up Test Flow                | 2-8  |

| 2.4   | SROM Errors Reported                   | 2-11 |

| 2.5   | XSROM Power-Up Test Flow               |      |

| 2.6   | XSROM Errors Reported                  | 2-15 |

| 2.7   | Console Power-Up Tests                 | 2-16 |

| 2.8   | Console Device Determination2-                               |                                        |      |  |

|-------|--------------------------------------------------------------|----------------------------------------|------|--|

| 2.9   | Console Power-Up Display                                     |                                        |      |  |

| 2.10  | Fail-Safe Loader                                             |                                        |      |  |

| Chap  | oter 3                                                       | Troubleshooting                        |      |  |

| 3.1   | Troubles                                                     | hooting with LEDs                      | 3-2  |  |

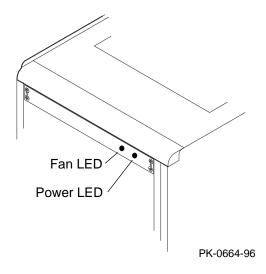

| 3.1.1 |                                                              | inet Power and Fan LEDs                |      |  |

| 3.2   |                                                              | hooting Power Problems                 |      |  |

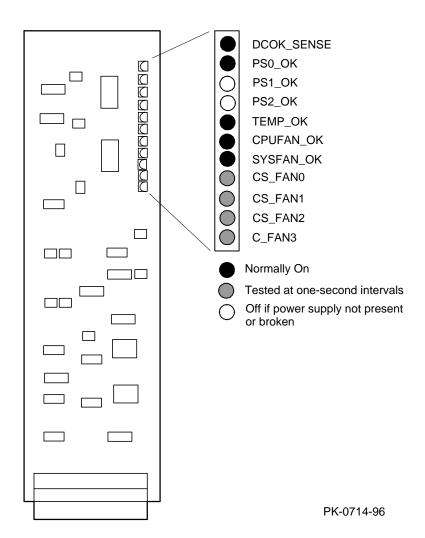

| 3.2.1 |                                                              | er Control Module LEDs                 |      |  |

| 3.3   |                                                              | ance Bus (I <sup>2</sup> C Bus)        |      |  |

| 3.4   |                                                              | Diagnostics —Test Command              |      |  |

| 3.5   | _                                                            | ın Entire System                       |      |  |

| 3.5.1 |                                                              | ing Memory                             |      |  |

| 3.5.2 |                                                              | ing PCI                                |      |  |

| Chap  | oter 4                                                       | Power System                           |      |  |

| 4.1   |                                                              | 1pply                                  | 4.2  |  |

| 4.1   |                                                              |                                        |      |  |

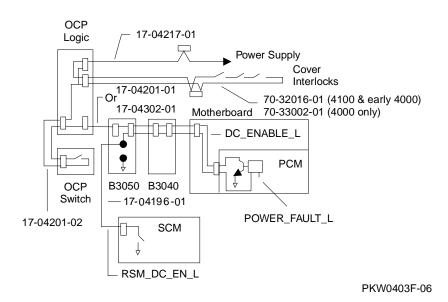

| 4.3   | Power Control Module Features                                |                                        |      |  |

| 4.4   | Power-Up/Down Sequence                                       |                                        |      |  |

| 4.5   | Cabinet Power Configuration Rules 4                          |                                        |      |  |

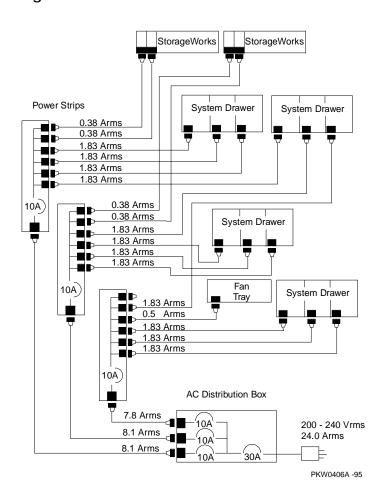

| 4.6   |                                                              |                                        |      |  |

| 4.7   | Pedestal Power Configuration Rules (North America and Japan) |                                        |      |  |

|       |                                                              | <i>S</i> ( r                           |      |  |

| Chap  | oter 5                                                       | Error Logs                             |      |  |

| 5.1   | Using Er                                                     | ror Logs                               | 5-2  |  |

| 5.1.1 | Hard                                                         | l Errors                               | 5-4  |  |

| 5.1.2 |                                                              | Errors                                 |      |  |

| 5.1.3 |                                                              | r Log Events                           |      |  |

| 5.2   |                                                              | ECevent                                |      |  |

| 5.2.1 |                                                              | slating Event Files                    |      |  |

| 5.2.2 |                                                              | ring Events                            |      |  |

| 5.2.3 |                                                              | cting Alternative Reports              |      |  |

| 5.3   |                                                              | g Examples and Analysis                |      |  |

| 5.3.1 |                                                              | HK 670 CPU-Detected Failure            |      |  |

| 5.3.2 |                                                              | HK 670 CPU and IOD Detected Failure    |      |  |

| 5.3.3 |                                                              | HK 670 Read Dirty CPU Detected Failure |      |  |

| 5.3.4 | MCl                                                          | HK 660 IOD-Detected Failure            | 5-28 |  |

| 5.3.5 | _                                                            | HK 630 Correctable CPU Error           |      |  |

| 5.3.6 |                                                              | HK 620 Correctable Error               |      |  |

| 5.4   | Troubles                                                     | hooting IOD-Detected Errors            | 5-38 |  |

| 5.4.2       System Bus Nonexistent Address Error       5.40         5.4.3       System Bus Address Parity Error       5.41         5.4.5       Page Table Entry Invalid Error       5.42         5.4.5       Page Table Entry Invalid Error       5.43         5.4.6       PCI Master Abort       5.43         5.4.7       PCI System Error       5.43         5.4.8       PCI Parity Error       5.43         5.4.9       Broken Memory       5.44         5.4.10       Command Codes       5.46         5.4.11       Node IDs       5.47         5.41       Node IDs       5.47         5.41       Node IDs       5.44         5.4.11       Node IDs       5.44         5.4.11       Node IDs       5.48         5.5.1       PALcode Overview       5.48         5.5.2       Double Error Halt       5.49         5.5.3       Machine Checks While in PAL       5.49         Chapter 6       Error Register         6.1       External Interface Status Register - EL_STAT       6-2         6.1.1       External Interface Address Register - EL_ADDR       6-6         6.1.2       MC Error Information Register 0       6-8                                                                             | 5.4.1 | System Bus ECC Error |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------|--|

| 5.4.4         PIO Buffer Overflow Error (PIO_OVFL)         5.42           5.4.5         Page Table Entry Invalid Error         5.43           5.4.6         PCI Master Abort         5.43           5.4.7         PCI System Error         5.43           5.4.8         PCI Parity Error         5.43           5.4.9         Broken Memory         5.44           5.4.11         Node IDs         5.47           5.4.11         Node IDs         5.47           5.5         Double Error Halts and Machine Checks While in PAL Mode         5.48           5.5.1         PALcode Overview         5.48           5.5.2         Double Error Halt         5.49           5.5.3         Machine Checks While in PAL         5.49           Chapter 6         Error Registers           6.1         External Interface Status Register - EL_STAT         6-2           6.1.1         External Interface Status Register - EL_STAT         6-6           6.1.2         MC Error Information Register 0         6-8           6.1.3         MC Error Information Register 1         6-9           6.1.4         CAP Error Register         6-11           6.1.5         PCI Error Status Register 1         6-14 |       |                      |  |

| 7.16        | PCI Motherboard (B3051) Removal and Replacement                 | 7-36          |  |

|-------------|-----------------------------------------------------------------|---------------|--|

| 7.17        | Server Control Module Removal and Replacement7-38               |               |  |

| 7.18        | PCI/EISA Option Removal and Replacement7-40                     |               |  |

| 7.19        | Power Supply Removal and Replacement7-42                        |               |  |

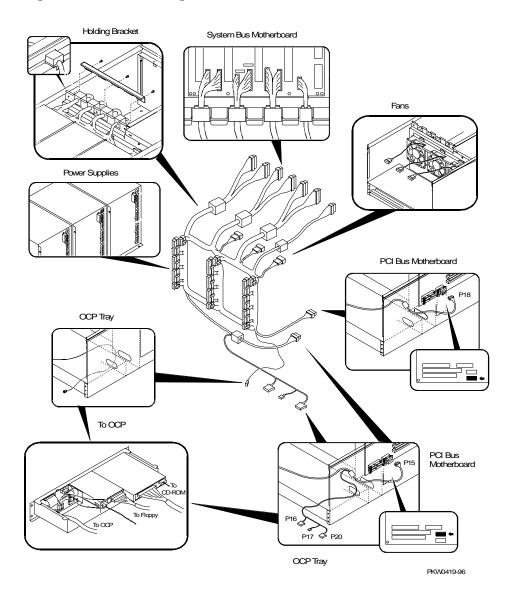

| 7.20        | Power Harness (4100 & early 4000) Removal and Replacement       |               |  |

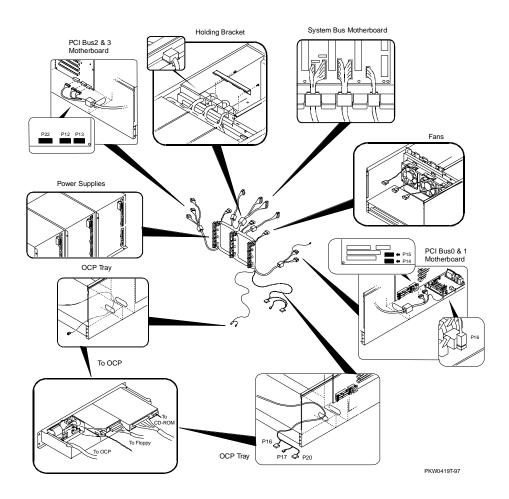

| 7.21        | Power Harness (Later 4000) Removal and Replacement              |               |  |

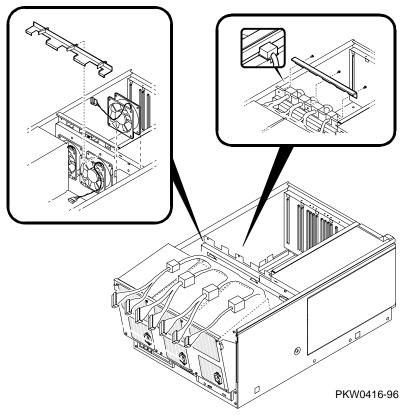

| 7.22        | System Drawer Fan Removal and Replacement                       | 7-48          |  |

| 7.23        | Cover Interlock (4100 & early 4000) Removal and Replacement     | 7-50          |  |

| 7.24        | Cover Interlock (Later 4000) Removal and Replacement            | 7-52          |  |

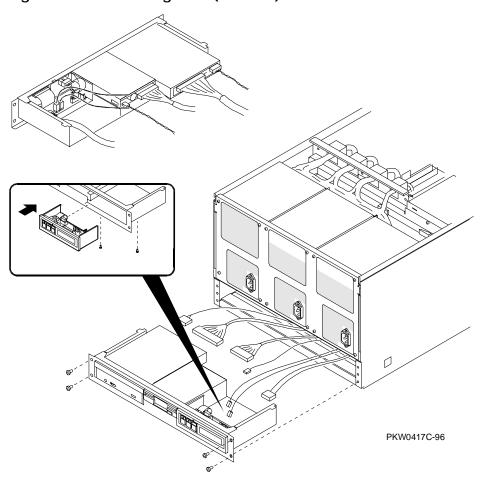

| 7.25        | Operator Control Panel Removal and Replacement (Cabinet)        | 7-54          |  |

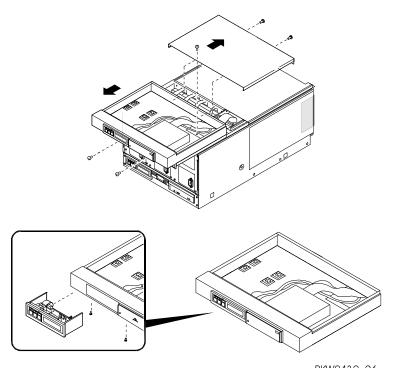

| 7.26        | Operator Control Panel Removal and Replacement (Pedestal)       | 7-56          |  |

| 7.27        | Floppy Removal and Replacement                                  | 7-58          |  |

| 7.28        | CD-ROM Removal and Replacement                                  | 7-60          |  |

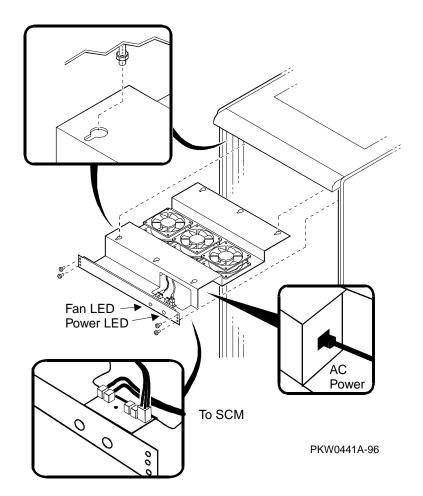

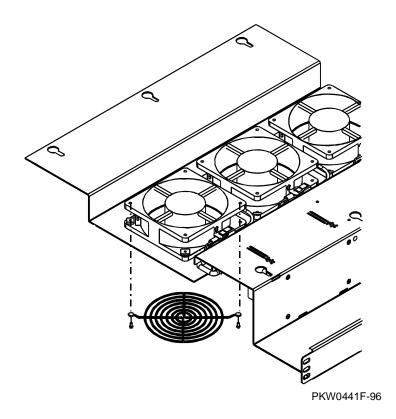

| 7.29        | Cabinet Fan Tray Removal and Replacement                        | 7-62          |  |

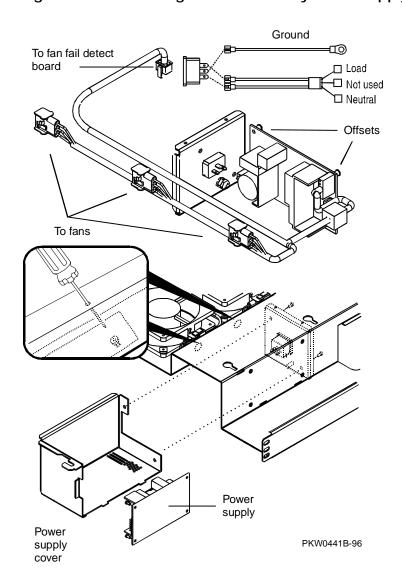

| 7.30        | Cabinet Fan Tray Power Supply Removal and Replacement           | 7-64          |  |

| 7.31        | Cabinet Fan Tray Fan Removal and Replacement                    | 7-66          |  |

| 7.32        | Cabinet Fan Tray Fan Fail Detect Module Removal and Replacement | 7-68          |  |

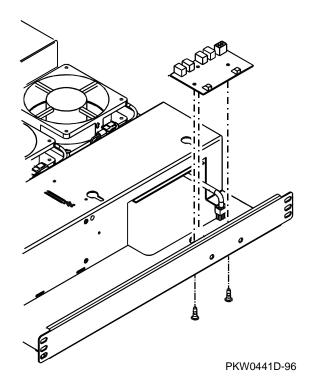

| 7.33        | StorageWorks Shelf Removal and Replacement                      | 7-70          |  |

|             |                                                                 |               |  |

| Appe        | ndix A Running Utilities                                        |               |  |

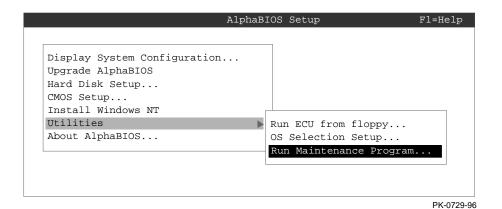

| A.1         | Running Utilities from a Graphics Monitor                       | . A-2         |  |

| A.2         | Running Utilities from a Serial Terminal                        |               |  |

| A.3         | Running ECU                                                     |               |  |

| A.4         | Running RAID Standalone Configuration Utility                   |               |  |

| A.5         | Updating Firmware with LFU                                      |               |  |

| A.5.1       | Updating Firmware from the Internal CD-ROM                      |               |  |

| A.5.2       | Updating Firmware from the Internal Floppy Disk — Creating the  |               |  |

|             | Diskettes                                                       | A-12          |  |

| A.5.3       | Updating Firmware from the Internal Floppy Disk — Performing    |               |  |

|             | the Update                                                      | A-14          |  |

| A.5.4       | Updating Firmware from a Network Device                         | A-18          |  |

| A.5.5       | LFU Commands                                                    | A-22          |  |

| A.6         | Updating Firmware from AlphaBIOS                                | A-25          |  |

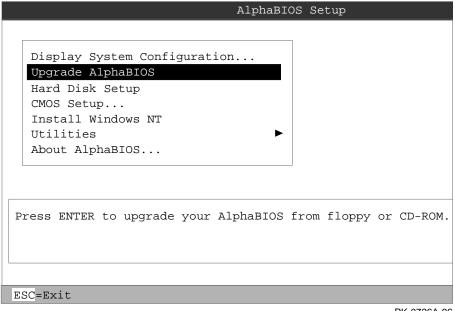

| A.7         | Upgrading AlphaBIOS                                             | A-26          |  |

|             |                                                                 |               |  |

| <b>Appe</b> | ndix B SRM Console Commands and Environmen                      | t             |  |

|             | Variables                                                       |               |  |

| B.1         | Summary of SRM Console Commands                                 | рγ            |  |

| B.2         | Summary of SRM Environment Variables                            | . <b>D</b> -Z |  |

| B.3         |                                                                 |               |  |

|             | Recording Environment Variables                                 | R 6           |  |

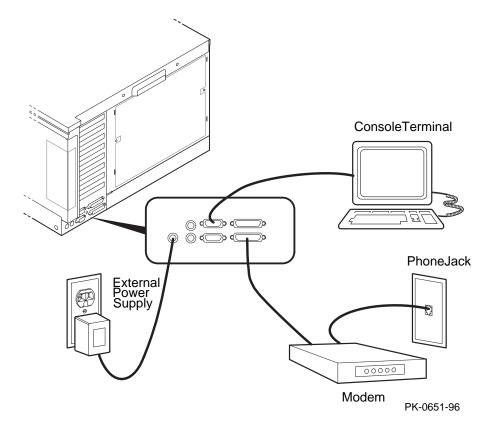

#### Appendix C Operating the System Remotely C.1 C.1.1 C.1.2C.1.3C.1.4 C.1.5 C.1.6C.1.7Index **Examples** SROM Errors Reported at Power-Up......2-11 2-1 2-2 XSROM Errors Reported at Power-Up......2-15 2-3 Power-Up Display.....2-20 3-1 Test Command Syntax .......3-12 3-2 3-3 Sample Test Memory Command .......3-15 3-4 5-1 MCHK 670 .......5-12 5-2 MCHK 670 CPU and IOD-Detected Failure ......5-17 5-3 MCHK 670 Read Dirty Failure......5-23 5-4 MCHK 660 IOD Detected Failure ......5-29 MCHK 630 Correctable CPU Error ......5-34 5-5 MCHK 620 Correctable Error ......5-36 5-6 5-7 INFO 3 Command.......5-50 5-8 5-9 A-1 A-2 A-3 A-4 Selecting AS4X00FW to Update Firmware from the Internal A-5 A-6 C-1 C-2 C-3 C-4

# Figures

| 1-1  | Components of the BA30A System Drawer1-2                |

|------|---------------------------------------------------------|

| 1-2  | Cover Interlock Circuit (BA30A)1-3                      |

| 1-3  | Components of the BA30C System Drawer1-4                |

| 1-4  | Cover Interlock Circuit (BA30C)1-5                      |

| 1-5  | Components of the BA30B System Drawer1-6                |

| 1-6  | Cover Interlock Circuit (BA30B)1-7                      |

| 1-7  | AlphaServer 4100 Cabinet System1-8                      |

| 1-8  | Cabinet Fan Tray1-9                                     |

| 1-9  | Pedestal System Front1-10                               |

| 1-10 | Pedestal System Rear1-11                                |

| 1-11 | Control Panel Assembly1-12                              |

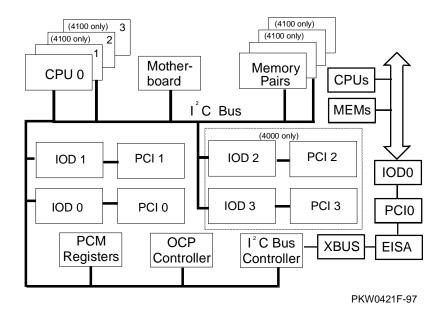

| 1-12 | Architecture Diagram1-16                                |

| 1-13 | System Motherboard Module Locations1-18                 |

| 1-14 | CPU Module Layout and Placement                         |

| 1-15 | Memory Module Layout and Placement1-22                  |

| 1-16 | How Memory Addressing Is Calculated1-24                 |

| 1-17 | System Bus Block Diagram and Slot Designation1-26       |

| 1-18 | Bridge Module1-28                                       |

| 1-19 | PCI Block Diagram1-30                                   |

| 1-20 | Server Control Module                                   |

| 1-21 | Power Control Module1-34                                |

| 1-22 | Location of Power Supply1-36                            |

| 2-1  | Control Panel and LCD Display2-2                        |

| 2-2  | Power-Up Flow2-4                                        |

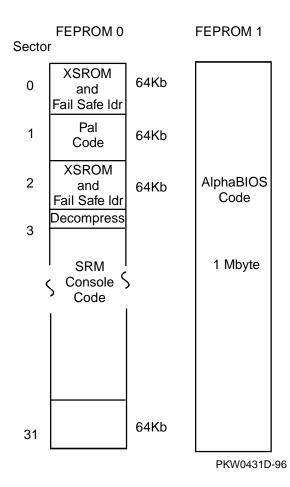

| 2-3  | Contents of FEPROMs2-5                                  |

| 2-4  | Console Code Critical Path2-6                           |

| 2-5  | SROM Power-Up Test Flow2-8                              |

| 2-6  | XSROM Power-Up Flowchart2-12                            |

| 2-7  | Console Device Determination Flowchart2-18              |

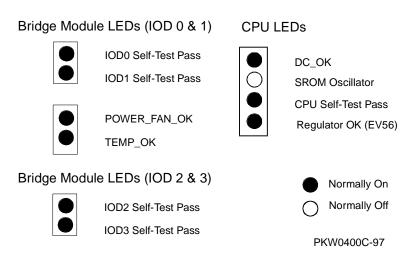

| 3-1  | CPU and Bridge Module LEDs3-2                           |

| 3-2  | Cabinet Power and Fan LEDs3-4                           |

| 3-4  | PCM LEDs3-8                                             |

| 3-5  | I <sup>2</sup> C Bus Block Diagram3-10                  |

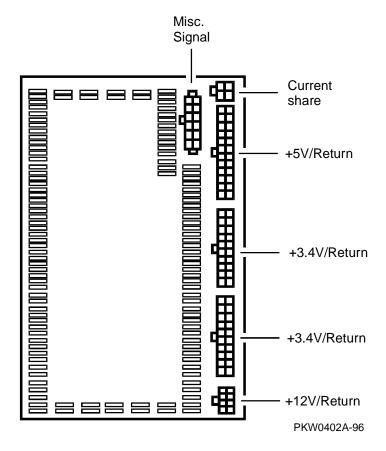

| 4-1  | Power Supply Outputs4-2                                 |

| 4-2  | Power Control Module4-4                                 |

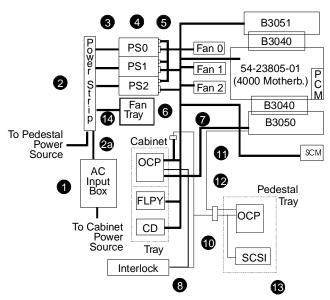

| 4-3  | Power Circuit Diagram4-6                                |

| 4-4  | Power Up/Down Sequence Flowchart4-8                     |

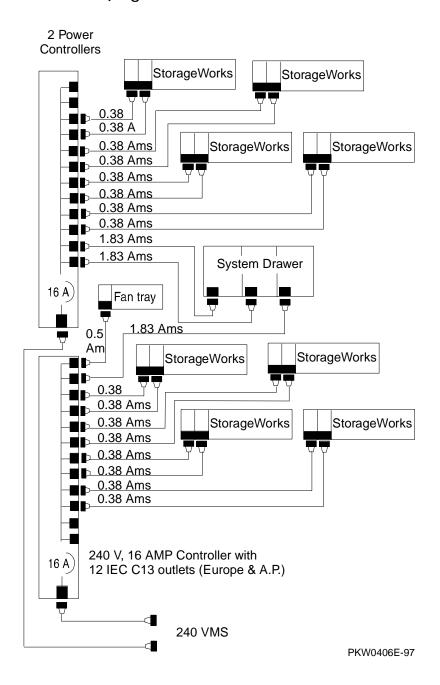

| 4-5  | Simple -EB & -EC Cabinet Power Configuration4-10        |

| 4-6  | Worst-Case -EB & -EC Cabinet Power Configuration4-11    |

| 4-7  | -EL & -EM Single Drawer Cabinet Power Configuration4-12 |

| 4-8  | -EL & -EM Three Drawer Cabinet Power Configuration4-13  |

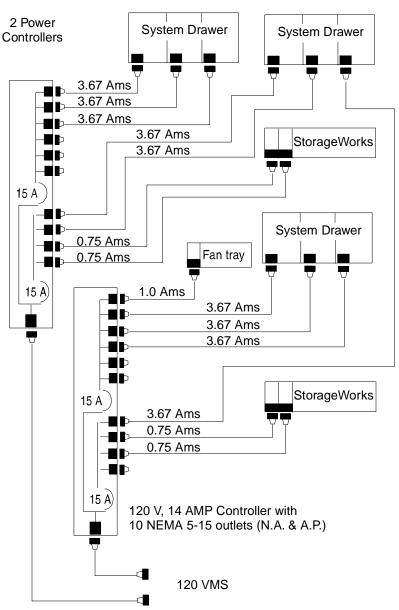

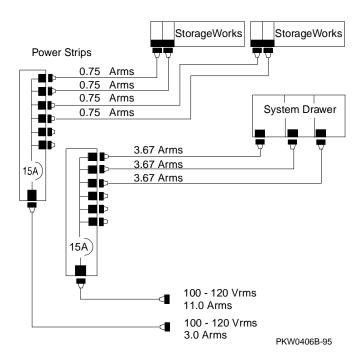

| 4-7  | Pedestal Power Distribution (N.A. and Japan)4-14        |

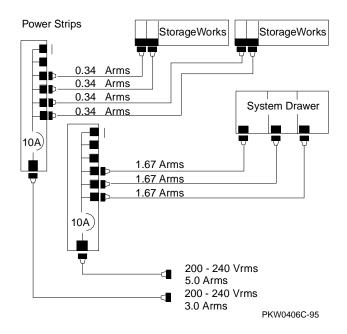

| 4-8   | Pedestal Power Distribution (Europe and AP)                   | 4-15 |

|-------|---------------------------------------------------------------|------|

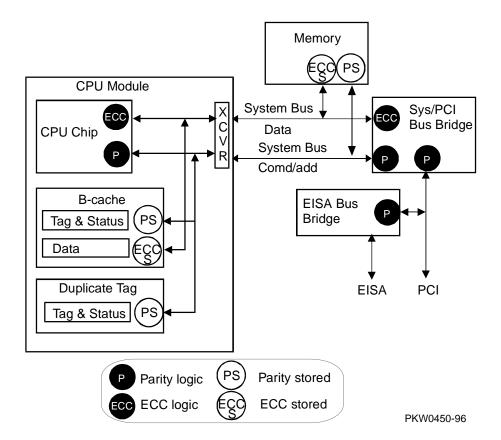

| 5-1   | Error Detector Placement                                      |      |

| 7-1   | System Drawer FRU Locations                                   | 7-2  |

| 7-2   | Location of 4100 Power System FRUs                            | 7-8  |

| 7-3   | Location of 4000 Power System FRUs                            | 7-10 |

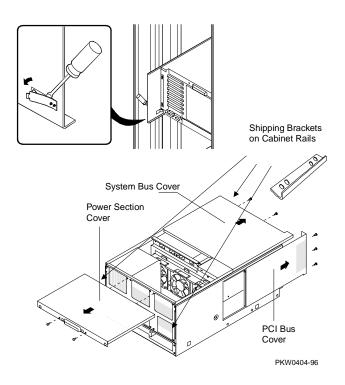

| 7-4   | Exposing System Drawer (H9A10-EB & -EC Cabinet)               | 7-12 |

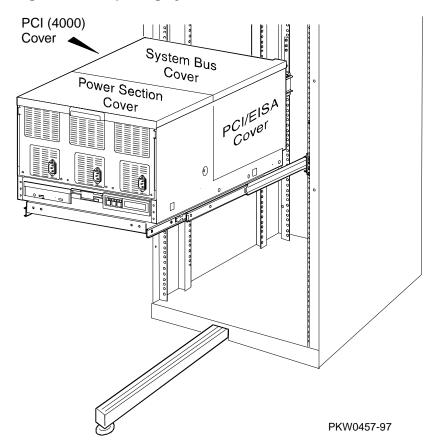

| 7-5   | Exposing System Drawer (H9A10-EL & -EM Cabinet)               | 7-14 |

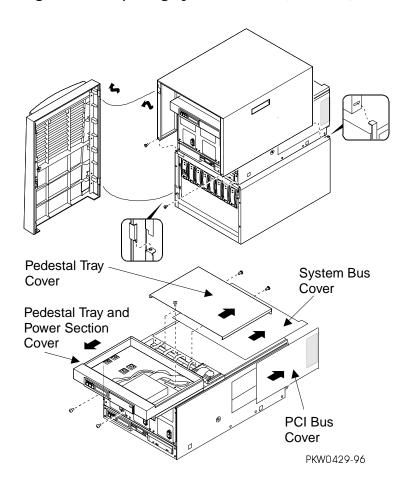

| 7-6   | Exposing System Drawer (Pedestal)                             | 7-16 |

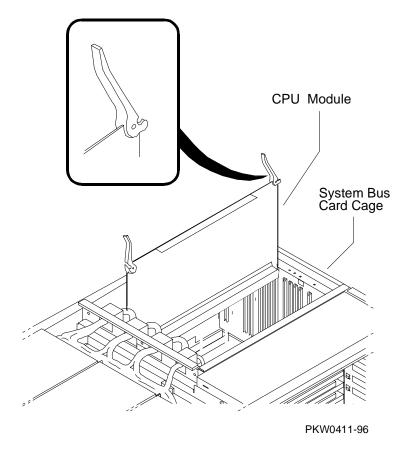

| 7-7   | Removing CPU Module                                           | 7-18 |

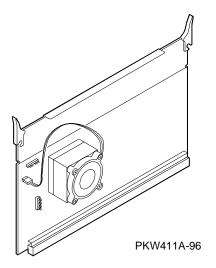

| 7-8   | Removing CPU Fan                                              | 7-20 |

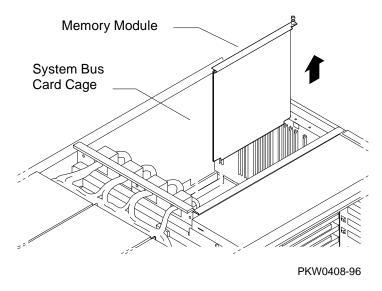

| 7-9   | Removing Memory Module                                        | 7-22 |

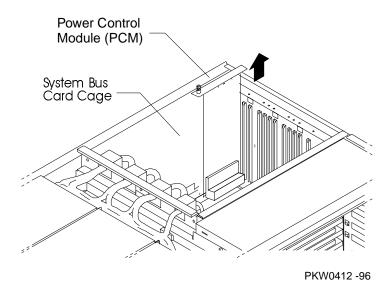

| 7-10  | Removing Power Control Module                                 | 7-24 |

| 7-11  | Removing System Bus to PCI/EISA Bus Bridge Module (B3040-AA). | 7-26 |

| 7-12  | Removing System Bus to PCI Bus Bridge Module (B3040-AB)       | 7-28 |

| 7-13  | Removing System Motherboard (4000 & early 4000)               |      |

| 7-14  | Removing System Motherboard (Later 4000)                      | 7-32 |

| 7-15  | Replacing PCI/EISA Motherboard                                | 7-34 |

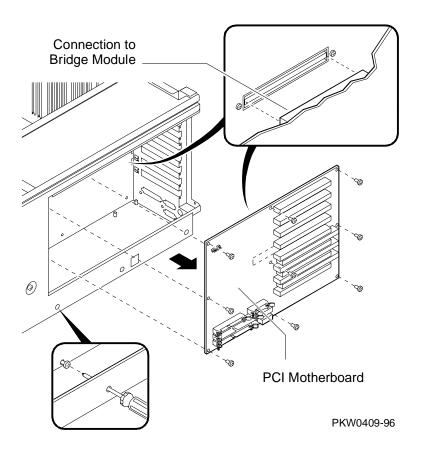

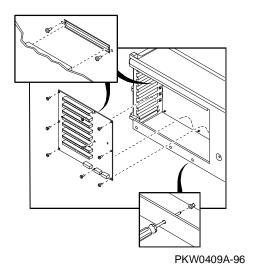

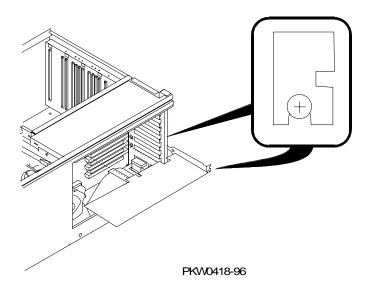

| 7-16  | Replacing PCI Motherboard                                     |      |

| 7-17  | Removing Server Control Module                                | 7-38 |

| 7-18  | Removing PCI/EISA Option                                      | 7-40 |

| 7-19  | Removing Power Supply                                         | 7-42 |

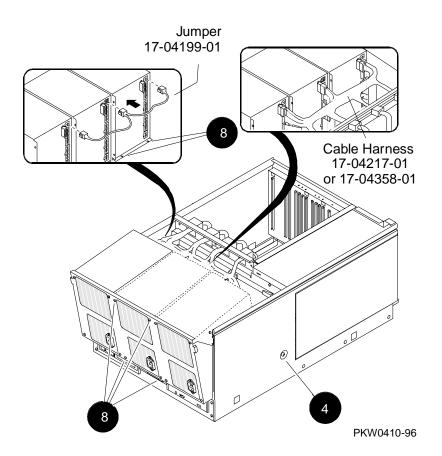

| 7-20  | Removing Power Harness (4100 & early 4000)                    |      |

| 7-21  | Removing Power Harness (Later 4000)                           | 7-46 |

| 7-22  | Removing System Drawer Fan                                    |      |

| 7-23  | Removing Cover Interlocks (4100 & early 4000)                 |      |

| 7-24  | Removing Cover Interlocks (Later 4000)                        | 7-52 |

| 7-25  | Removing OCP (Cabinet)                                        | 7-54 |

| 7-26  | Removing OCP (Pedestal)                                       | 7-56 |

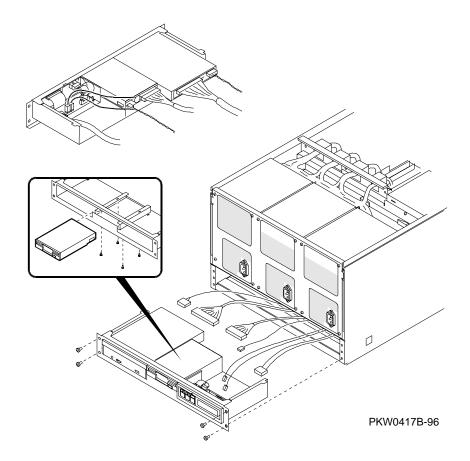

| 7-27  | Removing Floppy Drive                                         | 7-58 |

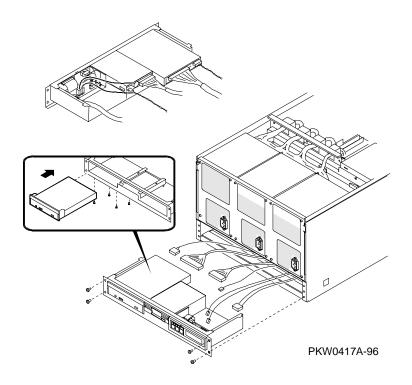

| 7-28  | Removing CD-ROM                                               | 7-60 |

| 7-29  | Removing Cabinet Fan Tray                                     | 7-62 |

| 7-30  | Removing Cabinet Fan Tray Power Supply                        | 7-64 |

| 7-31  | Removing Cabinet Fan Tray Fan                                 | 7-66 |

| 7-32  | Removing Fan Tray Fan Fail Detect Module                      | 7-68 |

| 7-33  | Removing StorageWorks Shelf                                   | 7-70 |

| A-1   | Running a Utility from a Graphics Monitor                     | A-2  |

| A-2   | Starting LFU from the AlphaBIOS Console                       |      |

| A-3   | AlphaBIOS Setup Screen                                        |      |

| C-1   | RCM Connections                                               | C-2  |

| Table | es                                                            |      |

| 1–1   | PCI Motherboard Slot Numbering                                | 1-31 |

| 2_1   | 5                                                             | 2-3  |

| 2-2  | SROM Tests                                                 | 2-10 |

|------|------------------------------------------------------------|------|

| 2-3  | XSROM Tests                                                | 2-13 |

| 2-4  | Memory Tests                                               | 2-14 |

| 2-5  | IOD Tests                                                  | 2-16 |

| 2-6  | PCI Motherboard Tests                                      | 2-17 |

| 3-1  | Power Control Module LED States                            | 3-9  |

| 5-1  | Types of Error Log Events                                  | 5-5  |

| 5-2  | DECevent Report Formats                                    | 5-10 |

| 5-3  | CAP Error Register Data Pattern                            | 5-38 |

| 5-4  | System Bus ECC Error Data Pattern                          | 5-39 |

| 5-5  | System Bus Nonexistent Address Error Troubleshooting       | 5-40 |

| 5-6  | Address Parity Error Troubleshooting                       | 5-41 |

| 5-7  | Cause of PIO_OVFL Error                                    | 5-42 |

| 5-8  | ECC Syndrome Bits Table                                    | 5-45 |

| 5-9  | Decoding Commands                                          | 5-46 |

| 5-10 | Node IDs                                                   | 5-47 |

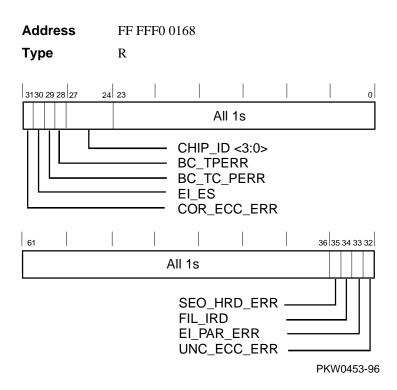

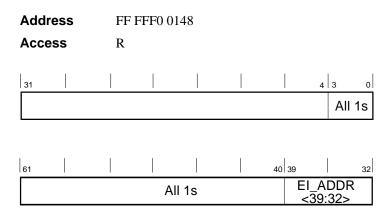

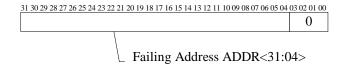

| 6-1  | External Interface Status Register                         | 6-4  |

| 6-2  | Loading and Locking Rules for External Interface Registers |      |

| 6-3  | MC Error Information Register 0                            | 6-8  |

| 6-4  | MC Error Information Register 1                            | 6-10 |

| 6-5  | CAP Error Register                                         | 6-12 |

| 6-6  | PCI Error Status Register 1                                | 6-14 |

| 7-1  | Field-Replaceable Unit Part Numbers                        | 7-3  |

| A-1  | AlphaBIOS Option Key Mapping                               | A-3  |

| A-2  | File Locations for Creating Update Diskettes on a PC       | A-12 |

| A-3  | LFU Command Summary                                        |      |

| B-1  | Summary of SRM Console Commands                            | B-2  |

| B-2  | Environment Variable Summary                               | B-4  |

| B-3  | Environment Variables Worksheet                            | B-6  |

| C-1  | RCM Command Summary                                        | C-6  |

| C-2  | RCM Status Command Fields                                  | C-14 |

| C-3  | RCM Troubleshooting                                        | C-19 |

| C-4  | RCM/Modem Interchange Summary                              | C-24 |

|      |                                                            |      |

# **Preface**

#### **Intended Audience**

This manual is written for the customer service engineer.

#### **Document Structure**

This manual uses a structured documentation design. Topics are organized into small sections for efficient online and printed reference. Each topic begins with an abastract, followed by an illustration or example, and ends with descriptive text.

This manual has seven chapters and three appendixes, as follows:

- Chapter 1, System Overview, introduces the DIGITAL AlphaServer 4000/4100 pedestal and cabinet systems and gives an overview of the system bus modules.

- Chapter 2, Power-Up, provides information on how to interpret the power-up

display on the operator control panel, the console screen, and system LEDs. It

also describes how hardware diagnostics execute when the system is initialized.

- **Chapter 3, Troubleshooting,** describes troubleshooting during power-up and booting, as well as the **test** command.

- Chapter 4, Power System, describes the AlphaServer 4000/4100 power system.

- Chapter 5, Error Logs, explains how to interpret error logs and how to use DECevent.

- Chapter 6, Error Registers, describes the error registers used to hold error information.

- Chapter 7, Removal and Replacement, describes removal and replacement procedures for field-replaceable units (FRUs).

- Appendix A, Running Utilities, explains how to run utilities such as the EISA Configuration Utility and RAID Standalone Configuration Utility.

- Appendix B, SRM Console Commands and Environment Variables, summarizes the commands used to examine and alter the system configuration.

- Appendix C, Operating the System Remotely, describes how to use the remote console monitor (RCM) to monitor and control the system remotely.

## **Documentation Titles**

Table 1 lists titles related to AlphaServer 4000/4100 systems.

Table 1 AlphaServer 4000/4100 Documentation

| Title                                                        | Order Number |

|--------------------------------------------------------------|--------------|

| ApphaServer 4100 User and Configuration<br>Documentation Kit | QZ-00VAA-GZ  |

| System Drawer User's Guide                                   | EK-4100A-UG  |

| Configuration and Installation Guide                         | EK-4100A-CG  |

| ApphaServer 4000 User and Configuration Documentation Kit    | QZ-00VAB-GZ  |

| System Drawer User's Guide                                   | EK-4000A-UG  |

| Configuration and Installation Guide                         | EK-4100A-CG  |

| Service Manual (hard copy)                                   | EK-4100A-SV  |

| Service Manual (diskette)                                    | AK-QXBJB-CA  |

| System Drawer Upgrades                                       | EK-4041A-UI  |

| PCI Upgrade                                                  | EK-4000A-UI  |

| KN30n CPU Installation Card                                  | EK-KN300-IN  |

| MS3n0 Memory Installation Card                               | EK-MS300-IN  |

| H7291 Power Supply Installation Card                         | EK-H7291-IN  |

| ServerWORKS Manager Administrator User's Guide               | ER-4QXAA-UA  |

## Information on the Internet

Using a Web browser you can access the AlphaServer InfoCenter at:

http://www.digital.com/info/alphaserver/products.html

Access the latest system firmware either with a Web browser or via FTP as follows:

ftp://ftp.digital.com/pub/Digital/Alpha/firmware/

Interim firmware released since the last firmware CD is located at:

ftp://ftp.digital.com/pub/Digital/Alpha/firmware/interim/

# Chapter 1

# **System Overview**

This chapter introduces the DIGITAL AlphaServer 4000 and the DIGITAL AlphaServer 4100 systems. These systems are available in cabinets or pedestals.

There are three system drawers; two, the BA30B and the BA30C, are used in the AlphaServer 4000, and the third, the BA30A, is used in the AlphaServer 4100.

The pedestal system has one system drawer and up to three StorageWorks shelves. The cabinet system can have a combination of system drawers and StorageWorks shelves that occupy the five sections of the cabinet.

Topics in this chapter include the following:

- AlphaServer 4100 System Drawer (BA30A)

- AlphaServer 4000 System Drawer (BA30C)

- AlphaServer 4000 System Drawer (BA30B)

- Cabinet System

- Pedestal System

- Control Panel and Drives

- System Consoles

- System Architecture

- System Motherboard

- **CPU Types**

- Memory Modules

- Memory Addressing

- System Bus

- System Bus to PCI Bus Bridge Module

- PCI I/O Subsystem

- Server Control Module

- Power Control Module

- Power Supply

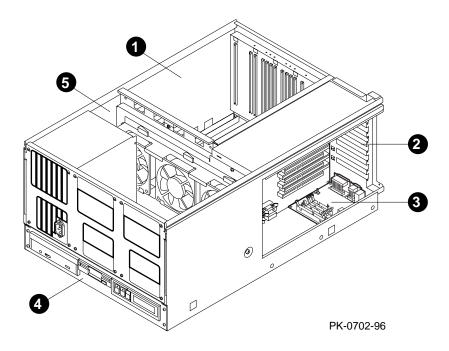

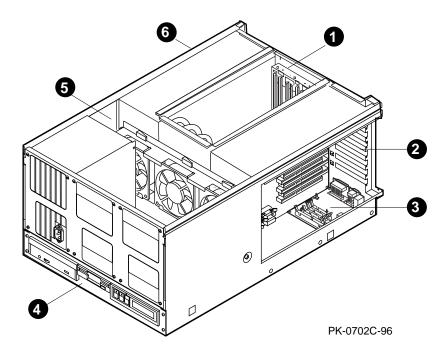

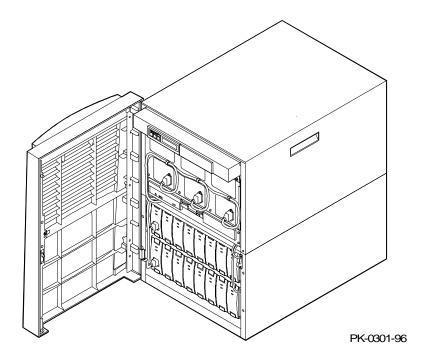

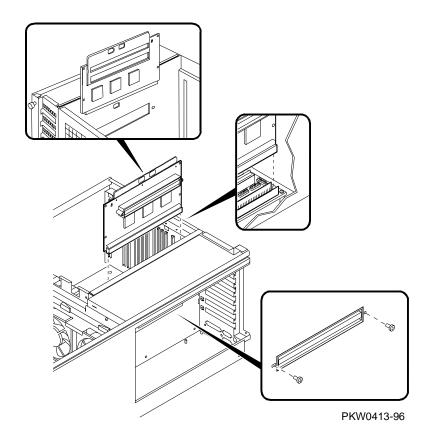

## 1.1 AlphaServer 4100 System Drawer (BA30A)

Components in the BA30A system drawer are located in the system bus card cage, the PCI card cage, the control panel assembly, and the power and cooling section. The drawer measures 30 cm x 45 cm (11.8 in. x 17.7 in.) and fully configured weighs approximately 45.5 kg (~100 lbs).

Figure 1-1 Components of the BA30A System Drawer

When the system drawer is in a pedestal, the control panel assembly is mounted in a tray at the top of the drawer.

The numbered callouts in Figure 1-1 refer to components of the system drawer.

- System card cage, which holds the system motherboard and the CPU, memory, bridge, and power control modules. (The difference between the BA30A and the BA30C is the system motherboard.)

- **2** PCI/EISA card cage, which holds the PCI motherboard, option cards, and server control module.

- **3** Server control module, which holds the I/O connectors and remote console monitor.

- Control panel assembly, which includes the control panel, a floppy drive, and a CD-ROM drive.

- **6** Power and cooling section, which contains one to three power supplies and fans.

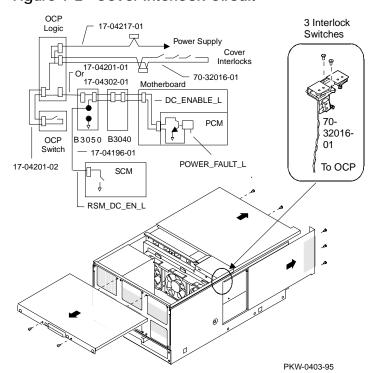

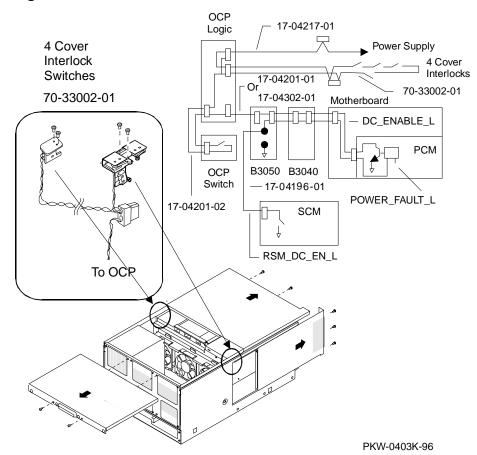

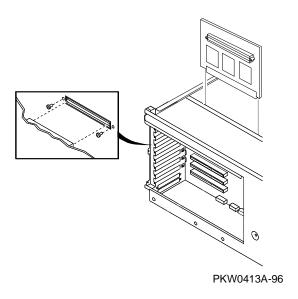

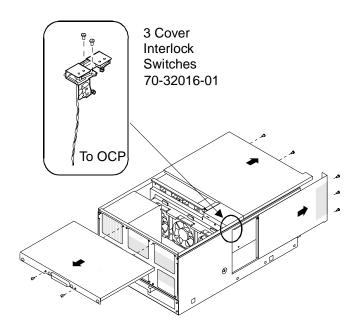

## **Cover Interlocks**

The system drawer has three cover interlocks: one for the system bus card cage, one for the PCI card cage, and one for the power and system fan area.

Figure 1-2 Cover Interlock Circuit

*NOTE:* The cover interlocks must be engaged to enable power-up.

To override the cover interlocks, find a suitable object to close the interlock circuit.

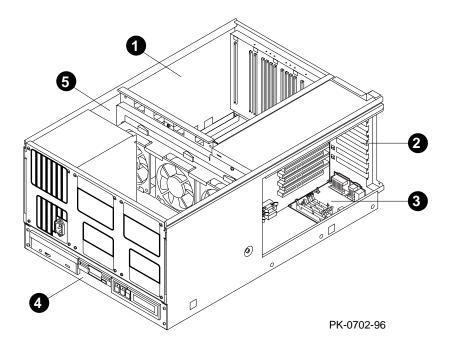

## 1.2 AlphaServer 4000 System Drawer (BA30C)

Components in the BA30C system drawer are located in the system bus card cage, PCI card cage, control panel assembly, and power and cooling section. The drawer measures 30 cm x 45 cm (11.8 in. x 17.7 in.) and fully configured weighs approximately 45.5 kg (~100 lbs).

Figure 1-3 Components of the BA30C System Drawer

When the system drawer is in a pedestal, the control panel assembly is mounted in a tray at the top of the drawer.

The numbered callouts in Figure 1-3 refer to components of the system drawer.

- System card cage, which holds the system motherboard and the CPU, memory, bridge, and power control modules. (The difference between the BA30A and the BA30C is the system motherboard.)

- **2** PCI/EISA card cage, which holds the PCI motherboard, option cards, and server control module.

- **3** Server control module, which holds the I/O connectors and remote console monitor.

- Control panel assembly, which includes the control panel, a floppy drive, and a CD-ROM drive.

- **6** Power and cooling section, which contains one to three power supplies and fans.

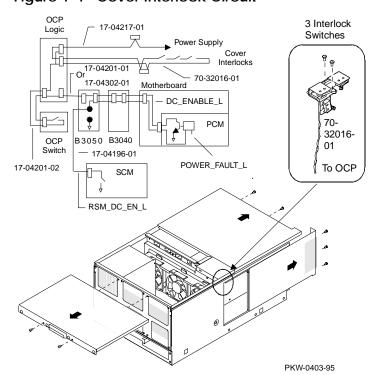

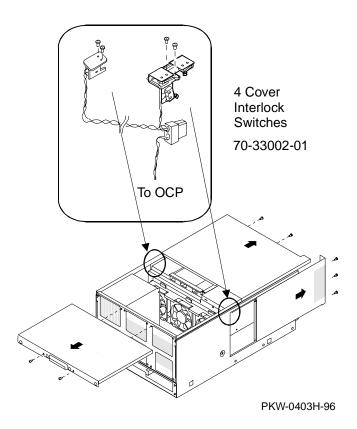

## **Cover Interlocks**

The system drawer has three cover interlocks: one for the system bus card cage, one for the PCI card cage, and one for the power and system fan area.

Figure 1-4 Cover Interlock Circuit

*NOTE:* The cover interlocks must be engaged to enable power-up.

To override the cover interlocks, find a suitable object to close the interlock circuit.

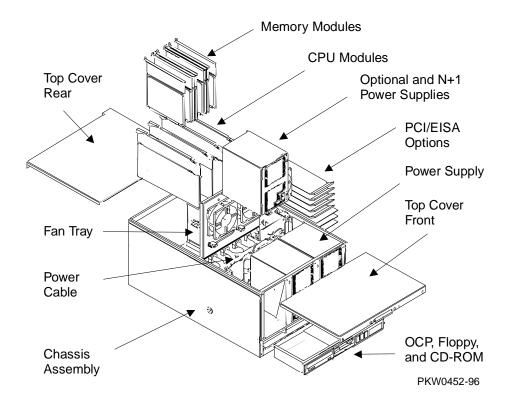

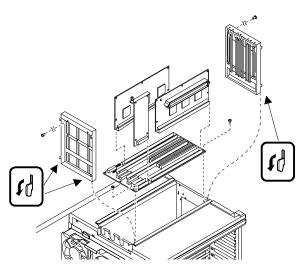

## 1.3 AlphaServer 4000 System Drawer (BA30B)

Components in the BA30B system drawer are located in the system bus card cage, two PCI card cages, the control panel assembly, and the power and cooling section. The drawer measures 30 cm x 45 cm (11.8 in. x 17.7 in.) and fully configured weighs approximately 45.5 kg (~100 lbs).

Figure 1-5 Components of the BA30B System Drawer

When the system drawer is in a pedestal, the control panel assembly is mounted in a tray at the top of the drawer.

The numbered callouts in Figure 1-5 refer to components of the system drawer.

- System card cage holds the system motherboard, the CPU, memory, bridge, and power control modules.

- **2** PCI/EISA card cage holds the PCI/EISA motherboard for PCI/EISA 0 and PCI 1, option cards, and server control module.

- **3** Server control module holds the I/O connectors and remote console.

- Control panel assembly holds the control panel, a floppy, and a CD-ROM.

- **6** Power and cooling section contains one to three power supplies and three fans.

- **6** PCI card cage holds the PCI motherboard for PCI 2 and PCI 3.

#### **Cover Interlocks**

The system drawer has four cover interlocks: one for each section of the drawer.

Figure 1-6 Cover Interlock Circuit

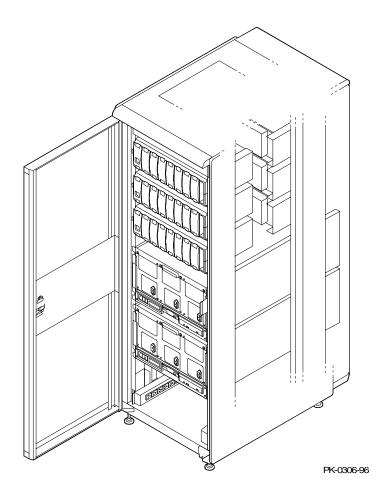

# 1.4 Cabinet System

The AlphaServer 4000/4100 cabinet system can accommodate multiple systems in a single cabinet. There are four cabinet variations that can hold different system configurations. Diferences are in power distribution and drawer mounting; from the outside the cabinets look almost identical.

Figure 1-7 AlphaServer 4000/4100 Cabinet System

## **Cabinet Differences**

| Cabinet  | Power                                         | Mounting                       | Destination                   |

|----------|-----------------------------------------------|--------------------------------|-------------------------------|

| H9A10-EB | AC input box power strips                     | C channel (max drawers: 4)     | North America<br>Asia Pacific |

| H9A10-EC | AC input box power strips                     | C channel (max drawers: 4)     | Europe                        |

| H9A10-EL | Two 120 volt<br>H7600-AA power<br>controllers | Pull-out tray (max drawers: 3) | North America<br>Asia Pacific |

| H9A10-EM | Two 240 volt<br>H7600-DB power<br>controllers | Pull-out tray (max drawers: 3) | Europe                        |

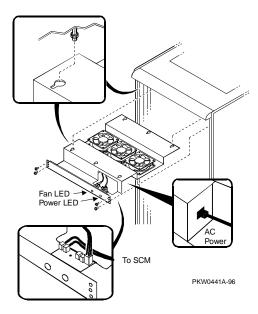

## **Cabinet System Fan Tray**

At the top of cabinet systems is a fan tray containing three exhaust fans, a small 12volt power supply, and a module that distributes power to the server control module in each drawer.

Figure 1-8 Cabinet Fan Tray

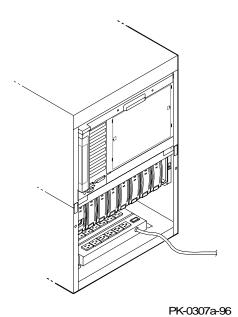

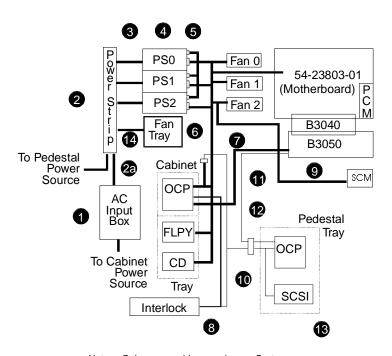

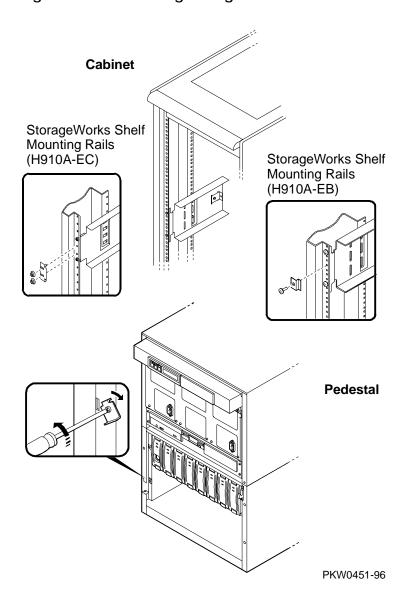

## 1.5 Pedestal System

The pedestal system contains one system drawer with a control panel, a CD-ROM drive, and a floppy drive. In the pedestal control panel area there is space for an optional tape or disk drive. Three StorageWorks shelves provide up to 90 Gbytes of in-cabinet storage.

Figure 1-9 Pedestal System Front

In the pedestal system, the control panel is located at the top left in a tray. See Figure 1-11. There is space for an optional device beside it.

Figure 1-10 Pedestal System Rear

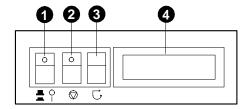

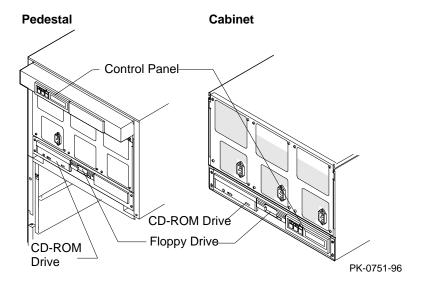

## 1.6 Control Panel and Drives

The control panel includes the On/Off, Halt, and Reset buttons and a display. In a pedestal system the control panel is located in a tray at the top of the system drawer. In a cabinet system it is at the bottom of the system drawer with the CD-ROM drive and the floppy drive.

Figure 1-11 Control Panel Assembly

On/Off button. Powers the system drawer on or off. When the LED at the top of the button is lit, the power is on. The On/Off button is connected to the power supplies and the system interlocks.

*NOTE:* The LEDs on some modules are on when the line cord is plugged in, regardless of the position of the On/Off button.

Halt button. Pressing this button in (so the LED at the top of the button is on) does the following:

If DIGITAL UNIX or OpenVMS is running, halts the operating system and returns to the SRM console. The Halt button has no effect on Windows NT.

If the Halt button is in when the system is reset or powered up, the system halts in the SRM console, regardless of the operating system. DIGITAL UNIX and OpenVMS systems that are configured for autoboot will not boot if the Halt button is in. Windows NT systems halt in the SRM console; AlphaBIOS is not loaded and started.

If you press the Halt button in (LED on) and do not issue commands that disturb the system state, entering the **continue** command returns the system to the operating system it was running. To return to console mode again, press the Halt button (LED off) and then press it again (LED on).

If the system is hung, pressing the Halt button (LED on) usually brings up the SRM console. Enter the crash command to do a crash dump. If pressing the Halt button does not bring up the SRM console, there is probably a hardware fault that is not allowing the halt signal to pass from the XBUS to the CPU.

- Reset button. Initializes the system drawer. If the Halt button is pressed (LED on) when the system is reset, the SRM console is loaded and remains in the system regardless of any other conditions.

- Control panel display. Indicates status during power-up and self-test. The OCP display is a 16-character LCD. Its controller is on the XBUS on the PCI motherboard.

While the operating system is running, displays the system type as a default. This message can be changed by the user.

CD-ROM drive. The CD-ROM drive is used to load software, firmware, and updates. Its controller is on PCI1 on the PCI motherboard.

Floppy disk drive. The floppy drive is used to load software and firmware updates. The floppy controller is on the XBUS on the PCI motherboard.

## 1.7 System Consoles

There are two console programs: the SRM console and the AlphaBIOS console.

#### **SRM Console Prompt**

On systems running the DIGITAL UNIX or OpenVMS operating system, the following console prompt is displayed after system startup messages are displayed, or whenever the SRM console is invoked:

P00>>>

NOTE: The console prompt displays only after the entire power-up sequence is complete. This can take up to several minutes if the memory is very large.

#### **AlphaBIOS Boot Menu**

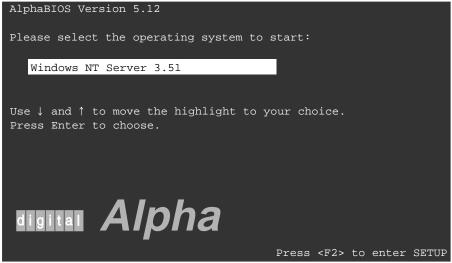

On systems running the Windows NT operating system, the Boot menu is displayed when the AlphaBIOS console is invoked:

PK-0728-96

#### **SRM Console**

The SRM console is a command-line interface that is used to boot the DIGITAL UNIX and OpenVMS operating systems. It also provides support for examining and modifying the system state and configuring and testing the system. The SRM console can be run from a serial terminal or a graphics monitor.

#### **AlphaBIOS Console**

The AlphaBIOS console is a menu-based interface that supports the Microsoft Windows NT operating system. AlphaBIOS is used to set up operating system selections, boot Windows NT, and display information about the system configuration. The EISA Configuration Utility and the RAID Standalone Configuration Utility are run from the AlphaBIOS console. AlphaBIOS runs on either a serial or graphics terminal, but Windows NT requires a graphics monitor.

#### **Environment Variables**

Environment variables are software parameters that define, among other things, the system configuration. They are used to pass information to different pieces of software running in the system at various times. The os\_type environment variable, which can be set to VMS, UNIX, or NT, determines which of the two consoles is to be used. The SRM console is always brought into memory, but AlphaBIOS is loaded if **os\_type** is set to **NT** and the Halt button is out (not lit).

Refer to Appendix B of this guide for a list of the environment variables used to configure AlphaServer 4000 and 4100 systems.

Refer to the AlphaServer 4x00 System Drawer User's Guide for information on setting environment variables.

It is recommended that you keep a record of the environment variables for each system that you service. Some environment variable settings are lost when a module is swapped and must be restored after the new module is installed. Refer to Appendix B for a convenient worksheet for recording environment variable settings.

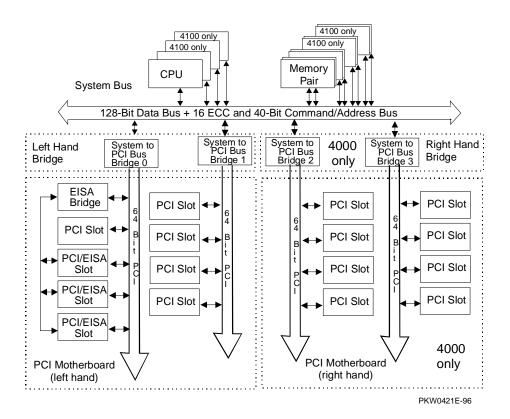

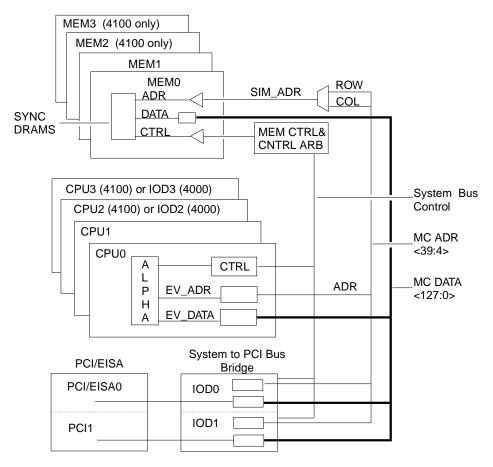

# 1.8 System Architecture

Alpha microprocessor chips are used in these systems. The CPU, memory, and the I/O bridge module(s) are connected to the system bus motherboard.

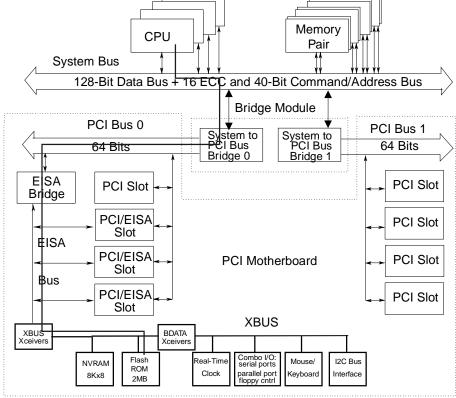

Figure 1-12 Architecture Diagram

AlphaServer 4000/4100 systems use the Alpha chip for the CPU. The CPU, memory, and I/O bridge modules, one to PCI/EISA I/O buses and another (4000 only) to another pair of PCIs, are connected to the system bus motherboard. A fourth type of module, the power control module, also plugs into the system motherboard. A fully configured 4100 system drawer can have up to four CPUs, four memory pairs, and a total of eight I/O options. The I/O options can be all PCI options or a combination of PCI options and EISA options, but there can be no more than three EISA options. A fully configured 4000 system drawer can have up to two CPUs, two memory pairs, and a total of sixteen I/O options. The I/O options can be all PCI options or a combination of PCI options and EISA options, but there can be no more than three EISA options.

The system bus has a 144-bit data bus protected by 16 bits of ECC and a 40-bit command/address bus protected by parity. The bus speed depends on the speed of the CPU in slot 0 which provides the clock for the buses. The 40-bit address bus can create one terabyte of addresses (that's a million billion). The bus connects CPUs, memory, and the system bus to PCI bus bridge(s).

The CPU modules are available with and without an external cache. The Alpha chip has an 8-Kbyte instruction cache (I-cache), an 8-Kbyte write-through data cache (Dcache), and a 96-Kbyte, write-back secondary data cache (S-cache). Some variants of the CPU module include an onboard cache. The cache system is write-back. The system drawer supports up to four CPUs.

The memory modules are placed on the system motherboard in pairs. Each module drives half of the system bus, along with the associated ECC bits. Memory pairs consist of two modules that are the same size and type. Two types are available: synchronous and asynchronous (EDO) memory.

The system bus to PCI bus bridge module translates system bus commands and data addressed to I/O space to PCI commands and data. It also translates PCI bus commands and data addressed to system memory or CPUs to system bus commands and data. The PCI bus is a 64-bit wide bus used for I/O. Both the 4100 and the 4000 have one PCI/EISA card cage, and the 4000 may contain a second PCI card cage.

The power control module, which is on the system motherboard, monitors power and the system environment.

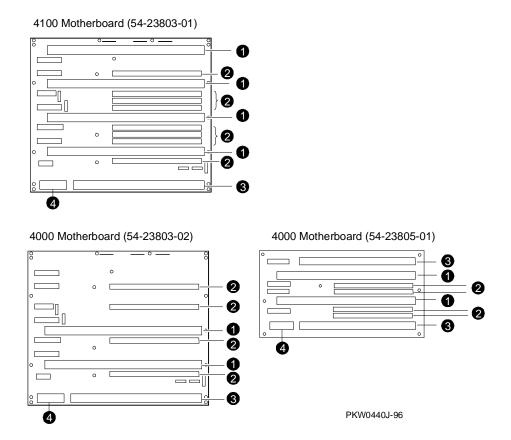

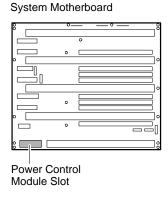

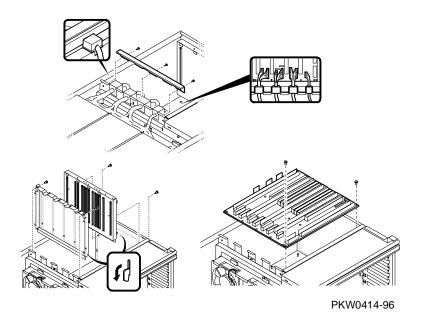

# 1.9 System Motherboard

The system motherboard is on the floor of the system card cage. It has slots for the CPU, memory, power control, and bridge modules.

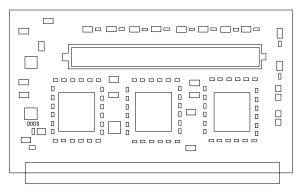

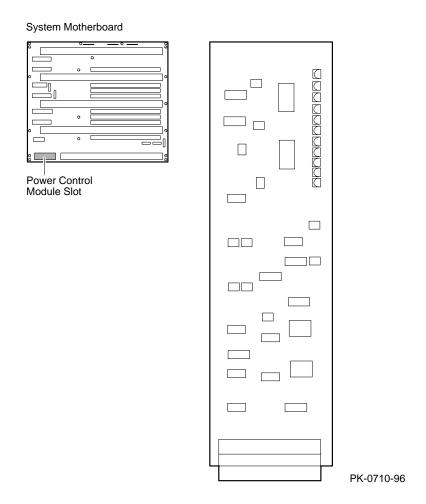

Figure 1-13 System Motherboard Module Locations

The system motherboard has the logic for the system bus. It is the backplane that holds the CPU, memory, bridge, and power control modules. Figure 1-13 shows diagrams of the three motherboards used in AlphaServer 4000/4100 systems. The module locations are designated by the callouts.

- 0 CPU module

- 0 Memory module

- 8 Bridge module

- 4 Power control module

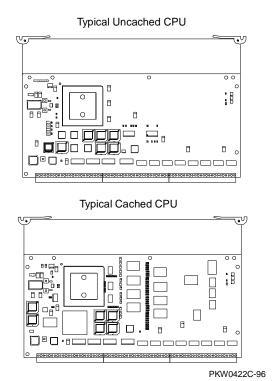

## 1.10 CPU Types

AlphaServer 4000 and 4100 systems can be configured with one of several CPU variants. Variants are differentiated by CPU speeds and the presence or absence of a backup data cache external to the Alpha microprocessor chip.

Figure 1-14 CPU Module Layout

### **Alpha Chip Composition**

The Alpha chip is made using state-of-the-art chip technology, has a transistor count of 9.3 million, consumes 50 watts of power, and is air cooled (a fan is on the chip). The default cache system is write-back and when the module has an external cache, it is write-back.

## **Chip Description**

| Unit                                                     | Description                                               |  |

|----------------------------------------------------------|-----------------------------------------------------------|--|

| Instruction                                              | 8-byte cache, 4-way issue                                 |  |

| Execution                                                | 4-way execution; 2 integer units, 1 floating-point adder, |  |

|                                                          | 1 floating-point multiplier                               |  |

| Memory Merge logic, 8-Kbyte write-through first-level da |                                                           |  |

| 96-Kbyte write-back second-level data cache, bus         |                                                           |  |

|                                                          | interface unit                                            |  |

#### **CPU Variants**

| Module Variant | Clock Frequency | Onboard Cache |

|----------------|-----------------|---------------|

| B3001-CA       | 300 MHz         | None          |

| B3002-AB       | 300 MHz         | 2 Mbytes      |

| B3004-BA       | 300 MHz         | 2 Mbytes      |

| B3004-AA       | 400 MHz         | 4 Mbytes      |

| B3004-DA       | 466 MHz         | 4 Mbytes      |

## **CPU Configuration Rules**

- The first CPU must be in CPU slot 0 to provide the system clock.

- Additional CPU modules should be installed in ascending order by slot number.

- All CPUs must have the same Alpha chip clock speed. The system bus will hang without an error message if the oscillators clocking the CPUs are different.

- Mixing of cached and uncached CPUs is not supported.

#### **Color Codes**

The top edge of the CPU module variant is color coded for easy identification.

| Color     | Option<br>Number | Description         |  |

|-----------|------------------|---------------------|--|

| Dark Blue | B3001-CA         | 300 MHz, uncached   |  |

| Green     | B3002-AB         | 300 MHz, 2MB cached |  |

| Green     | B3004-BA         | 300 MHz, 2MB cached |  |

| Orange    | B3004-AA         | 400 MHz, 4MB cached |  |

| Red       | B3004-DA         | 466 MHz, 4MB cached |  |

## 1.11 Memory Modules

Memory modules are used only in pairs — two modules of the same size and type. Each module provides either the low half or the high half of the memory space. The 4100 system drawer can hold up to four memory module pairs. The 4000 system drawer can hold up to two memory module pairs.

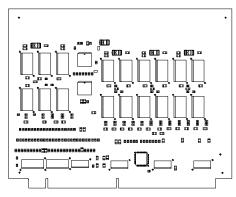

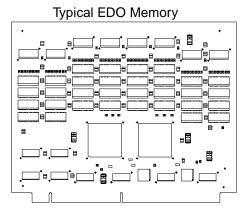

Figure 1-15 Memory Module Layout

Typical Synchronous Memory

PKW0423C-96

#### **Memory Variants**

Each memory option consists of two identical modules. Each 4100 drawer supports up to four memory options, for a total of 4 Gbytes of memory: 4000 drawers support half that. Memory modules are used only in pairs and are available in 128 Mbyte, 512 Mbyte, and 1 Gbyte sizes. The 128-Mbyte option is synchronous memory, while the larger sizes are asynchronous memory (EDO).

|          |        |          | DRAM          |        |           |

|----------|--------|----------|---------------|--------|-----------|

| Option   | Size   | Module   | Туре          | Number | Size      |

| MS320-CA | 128 MB | B3020-CA | Synch.        | 36     | 4 MB x 4  |

| MS330-EA | 512 MB | B3030-EA | Asynch. (EDO) | 144    | 4 MB x 4  |

| MS330-FA | 1 GB   | B3030-FA | Asynch. (EDO) | 72     | 16 MB x 4 |

| MS330-GA | 2 GB   | B3030-GA | Asynch. (EDO) | 144    | 16 MB x 4 |

#### **Memory Operation**

Memory modules are used only in pairs; each module provides half the data, or 64 bits plus 8 ECC bits, of the octaword (16 byte) transferred on the system bus. Modules are placed in slots designated MEMxL and MEMxH.

NOTE: Modules in slots MEMxL do not drive the lower 8 bytes, and modules in slots MEMxH do not drive the higher 8 bytes of the 16 byte transfer.

Unless otherwise programmed, memory drives the system bus in bursts. Upon each memory fetch, data is transferred in 4 consecutive cycles transferring 64 bytes. There are situations, however, when memories made with EDO DRAMs cannot provide data fast enough to complete the system bus transactions. When these situations arise, EDO type memories assert a signal that causes the system bus to stall for one (occasionally more) clock tick. When memory completes such an operation, it releases the system bus.

#### **Memory Configuration Rules**

In a system, memories of different sizes and types are permitted, but:

- Memory modules are installed and used in pairs. Both modules in a memory pair must be of the same size and type.

- The largest memory pair must be in slots MEM 0L and MEM 0H.

- Other memory pairs must be the same size or smaller than the first memory pair.

- Memory pairs must be installed in consecutive slots.

## 1.12 Memory Addressing

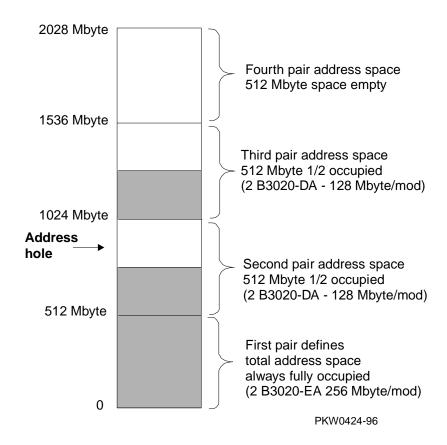

Alpha system memory addressing is unusual because memory address space is determined not by the amount of physical memory but is calculated by a multiple of the size of the memory pair in slot MEM0x.

Figure 1-16 How Memory Addressing Is Calculated

The rules for addressing memory are as follows:

- 1. Address space is determined by the memory pair in slot MEM0.

- 2. Memory pairs need not be the same size.

- 3. The memory pair in slot MEM0 must be the largest of all memory pairs. Other memory pairs may be as large but none may be larger.

- 4. The starting address of each memory pair is N times the size of the memory pair in slot MEM0. N=0,1,2,3.

- 5. Memory addresses are contiguous within each module pair.

- 6. If memory pairs are of different sizes, memory "holes" can occur in the physical address space. See Figure 1-16.

- 7. Software creates contiguous virtual memory even though physical memory may not be contiguous.

# 1.13 System Bus

The system bus consists of a 40-bit command/address bus, a 128-bit plus ECC data bus, and several control signals and clocks.

Figure 1-17 System Bus Block Diagram

PKW0425-96

The system bus motherboard consists of a 40-bit command/address bus, a 128-bit plus ECC data bus, and several control signals, clocks, and a bus arbiter. The bus requires that all CPUs have the same high-speed oscillator providing the clock to the Alpha chip.

The AlphaServer 4100 system bus connects up to four CPUs, four pairs of memory modules, and a single I/O bus bridge module. Note that the I/O bus bridges may be desinated as IODn where n is the number of the PCI bus. The first bridge is designated IOD0 and IOD1.

The AlphaServer 4000 system bus connects up to two CPUs, two pairs of memory modules, and two I/O bus bridge modules. The second bridge on the 4000 system bus is designated IOD2 and IOD3.

The system bus clock is provided by an oscillator on the CPU in slot CPU0. This oscillator has a 1:5 ratio to the Alpha chip. With 300 MHz CPUs, for example, the system bus operates at 60 MHz.

The system bus motherboard initiates memory refresh transactions. The motherboard sits at the bottom of the system drawer, and in addition to CPUs, memory, and I/O bridges, holds a power control module.

5 volt and 3.43 volt power is provided directly to the motherboard from the power supplies.

# 1.14 System Bus to PCI Bus Bridge Module

The bridge module is the physical interconnect between the system motherboard and any PCI motherboard in the system.

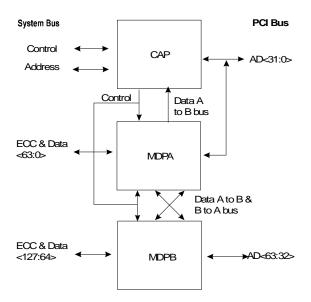

Figure 1-18 Bridge Module

PKW0426r-96

The system bus to PCI bus bridge module converts system bus commands and data addressed to I/O space to PCI commands and data; and converts PCI bus commands and data addressed to system memory or CPUs to system bus commands and data. An AlphaServer 4100 system has one bridge module; an AlphaServer 4000 system can have a second bridge module.

The bridge has two major components:

- Command/address processor (CAP) chip

- Two data path chips (MDPA and MDPB)

There are two sets of these three chips, one set on each side of the module. Each set bridges to one of the PCI buses on the PCI motherboard.

The interface on the system bus side of the bridge responds to system bus commands addressed to the upper 64 Gbytes of I/O space. I/O space is addressed whenever bit <39> on the system bus address lines is set. The space so defined is 512 Gbytes in size. The first 448 Gbytes are reserved and the last 64 Gbytes, when bits <38:36> are set, are mapped to the PCI I/O buses.

The interface on the PCI side of the bridge responds to commands addressed to CPUs and memory on the system bus. On the PCI side, the bridge provides the interface to the PCIs. Each PCI bus is addressed separately. The bridge does not respond to devices communicating with each other on the same PCI bus. However, should a device on one PCI address a device on the other PCI bus, commands, addresses, and data run through the bridge out onto the system bus and back through the bridge to the other PCI bus.

In addition to its bridge function, the system bus to PCI bus bridge module monitors every transaction on the system bus for errors. It monitors the data lines for ECC errors and the command/address lines for parity errors.

NOTE: When errors are logged, the two bridge modules on the AlphaServer 4000 are differentiated in the error log by their engineering code names, the left hand horse and the right hand horse. The left hand horse is the B3040-AA module; it is in the left most slot on the system bus motherboard when seen from the rear of the drawer. The right hand horse is the B3040-AB module, and it is in the right most slot on the system bus motherboard when seen from the rear of the drawer.

## 1.15 PCI I/O Subsystem

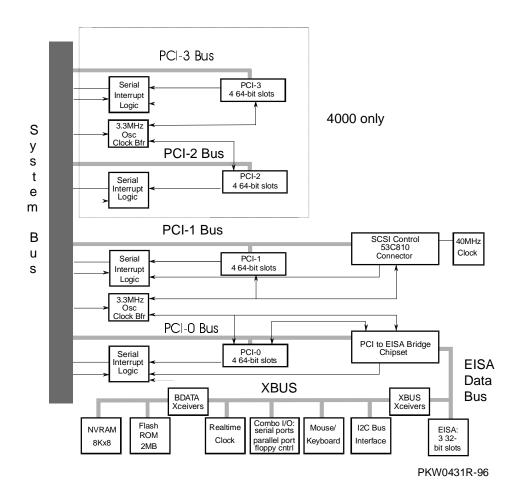

The I/O subsystem is PCI. Both the 4100 and the 4000 have two four-slot PCI buses that hold up to eight I/O options. One of these buses can be both PCI and EISA but can hold not more than four options three of which may be EISA. The 4000 can have an additional two four-slot PCI buses allowing a total of sixteen I/O options.

Figure 1-19 PCI Block Diagram

Table 1–1 PCI Motherboard Slot Numbering

| Slot | PCI0                  | PCI1                       | PCI2<br>(4000 only) | PCI3<br>(4000 only) |

|------|-----------------------|----------------------------|---------------------|---------------------|

| 0    | Reserved              | Reserved                   | Reserved            | Reserved            |

| 1    | PCI to EISA<br>bridge | Internal CD-ROM controller | Reserved            | Reserved            |

| 2    | PCI or EISA slot      | PCI slot                   | PCI slot            | PCI slot            |

| 3    | PCI or EISA slot      | PCI slot                   | PCI slot            | PCI slot            |

| 4    | PCI or EISA slot      | PCI slot                   | PCI slot            | PCI slot            |

| 5    | PCI slot              | PCI slot                   | PCI slot            | PCI slot            |

The logic for two PCI buses is on each PCI motherboard.

- PCI0 is a 64-bit bus with a built-in PCI to EISA bus bridge. PCI0 has one dedicated PCI slot and three slots, though there are six connectors, that can be PCI or EISA slots. Each slot has an EISA connector and a PCI connector only one of which may be used at a time. PCI0 is powered by 5V.

- PCI1 is a 64-bit bus with a built-in CD-ROM controller and four PCI slots. PCI1 is powered by 5V.

- PCI2 (4000 only) is a 64-bit four-slot PCI bus powered by both 3V and 5V.

- PCI3 (4000 only) is a 64-bit four-slot PCI bus powered by both 3V and 5V.

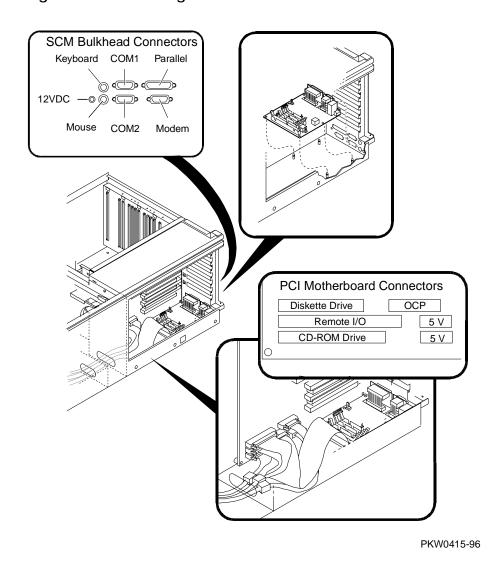

The B3050-AA PCI motherboard has cable connections to remote I/O (mouse, keyboard, serial port, and parallel port), an internal floppy drive, an internal CD-ROM drive, the control panel, and 5V power. Also on this module are the chips for the PCI to EISA bridge and the internal CD-ROM controller. This module is the motherboard for the PCI card cage on the left side of the system drawer.

An 8-bit XBUS is connected to the EISA bus. On this bus there is an interface to the system I<sup>2</sup>C bus; mouse and keyboard support; an I/O combo controller supporting two serial ports, the floppy controller, and a parallel port; a real-time clock; two 1-Mbyte flash ROMs containing system firmware, and an 8-Kbyte NVRAM.

The B3050-AB PCI motherboard, used only in the AlphaServer 4000, contains two four-slot 64-bit PCI buses.

## 1.16 Server Control Module

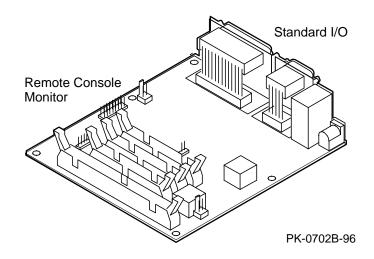

The server control module enables remote console connections to the system drawer. The module passes signals to COM ports 1 and 2, the keyboard, and the mouse to the standard I/O connectors.

Figure 1-20 Server Control Module

The server control module has two sections: the remote console monitor (RCM) and the standard I/O. See Appendix C for information on controlling the system remotely.

The remote console monitor connects to a modem through the modem port on the bulkhead. The RCM requires a 12V power connection.

The standard I/O ports (keyboard, mouse, COM1 and COM2 serial, and parallel ports) are on the same bulkhead.

## 1.17 Power Control Module

The power control module controls power sequencing and monitors power supply voltage, temperature, and fans.

Figure 1-21 Power Control Module

The power control module performs these functions:

- Controls power sequencing.

- Monitors the combined output of power supplies and shuts down power if it is not in range.

- Monitors system temperature and shuts off power if it is out of range.

- Monitors the fans in the system drawer and on the CPU modules and shuts down power if a fan fails.

- Provides visual indication of faults through LEDs.

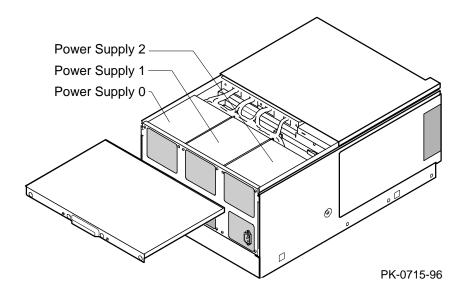

# 1.18 Power Supply

The system drawer power supplies provide power only to components in the drawer. One or two power supplies are required, depending on the number of CPU modules and PCI card cages; a second or third can be added for redundancy. The power system is described in detail in Chapter 4.

Figure 1-22 Location of Power Supply

#### **Description**

One to three power supplies provide power to components in the system drawer. (They supply power only for the drawer in which they are located.) Three power supplies provide redundant power in fully loaded AlphaServer 4000/4100 systems.

These power supplies share the load, and redundant configurations are supported. They autoselect line voltage (120V to 240V). Each has 450 W output and supplies up to 75A of 3.43V, 50A of 5.0V, 11A of 12V, and small amounts of -5V, -12V, and auxiliary voltage (Vaux).

*NOTE:* The LEDs on some modules are on when the line cord is plugged in, regardless of the position of the On/Off button.

#### Configuration

- An AlphaServer 4100 system with one or two CPUs requires one power supply (two for redundancy).

- An AlphaServer 4100 system with three or four CPUs requires two power supplies (three for redundancy).

- An AlphaServer 4000 system with one or two CPUs and one PCI card cage requires one power supply (two for redundancy).

- An AlphaServer 4000 system with one or two CPUs and two PCI card cages requires two power supplies (three for redundancy).

- Power supply 0 is installed first, power supply 2 second, and power supply 1 third. See Figure 1-22. (The power supply numbering shown here corresponds to the numbering displayed by the SRM console's **show power** command.)

# Chapter 2

# Power-Up

This chapter describes system power-up testing and explains the power-up displays. The following topics are covered:

- Control Panel

- Power-Up Sequence

- SROM Power-Up Test Flow

- SROM Errors Reported

- XSROM Power-Up Test Flow

- XSROM Errors Reported

- Console Power-Up Tests

- Console Device Determination

- Console Power-Up Display

- Fail-Safe Loader

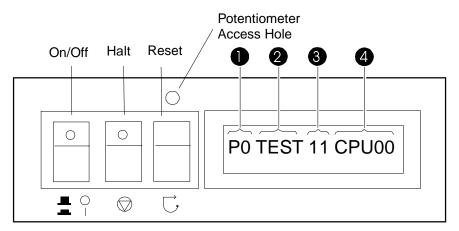

### 2.1 Control Panel

The control panel display indicates the likely device when testing fails.

Figure 2-1 Control Panel and LCD Display

PK-0706G-96

- When the On/Off button LED is on, power is applied and the system is running. When it is off, the system is not running, but power may or may not be present. If power is present, the PCM or the power LED on the system bus to PCI bus bridge module should be flashing. Otherwise, there is a power problem.

- When the Halt button LED is lit and the On/Off button is on, the system should be running either the SRM console or Windows NT. If the Halt button is in, but the LED is off, the OCP, its cables, or the PCM is likely to be broken.

Table 2-1 Control Panel Display

| Field    | Content          | Display                  | Meaning                                                                |

|----------|------------------|--------------------------|------------------------------------------------------------------------|

| 0        | CPU number       | P0-P3                    | CPU reporting status                                                   |

| <b>2</b> | Status           | TEST                     | Tests are executing                                                    |

|          |                  | FAIL                     | Failure has been detected                                              |

|          |                  | MCHK                     | Machine check has occurred                                             |

|          |                  | INTR                     | Error interrupt has occurred                                           |

| <b>©</b> | Test number      |                          |                                                                        |

| 4        | Suspected device | CPU0-3                   | CPU module number <sup>1</sup>                                         |

|          |                  | MEM0–3 and<br>L, H, or * | Memory pair number and low module, high module, or either <sup>2</sup> |

|          |                  | IOD0                     | Bridge to PCI bus 0 <sup>3</sup>                                       |

|          |                  | IOD1                     | Bridge to PCI bus 1 <sup>3</sup>                                       |

|          |                  | IOD2                     | Bridge to PCI bus 2 <sup>4</sup>                                       |

|          |                  | IOD3                     | Bridge to PCI bus 3 <sup>4</sup>                                       |

|          |                  | FROM0                    | Flash ROM <sup>5</sup>                                                 |

|          |                  | COMBO                    | COM controller <sup>5</sup>                                            |

|          |                  | PCEB                     | PCI-to-EISA bridge⁵                                                    |

|          |                  | ESC                      | EISA system controller <sup>5</sup>                                    |

|          |                  | NVRAM                    | Nonvolatile RAM <sup>5</sup>                                           |

|          |                  | TOY                      | Real-time clock <sup>5</sup>                                           |

|          |                  | I8242                    | Keyboard and mouse controller <sup>5</sup>                             |

The potentiometer, accessible through the access hole just above the Reset button controls the intensity of the LCD. Use a small Phillips head screwdriver to adjust.

<sup>&</sup>lt;sup>1</sup> CPU module

<sup>&</sup>lt;sup>2</sup> Memory module

<sup>&</sup>lt;sup>3</sup> Bridge module (B3040-AA)

<sup>&</sup>lt;sup>4</sup> Bridge module (B3040-AB)

<sup>&</sup>lt;sup>5</sup> EISA/PCI motherboard

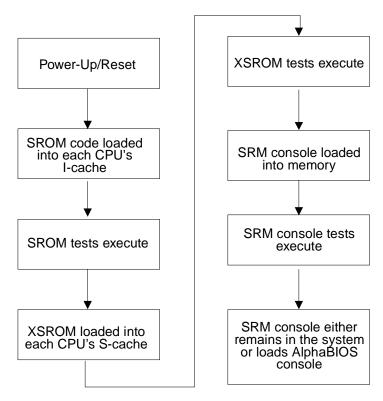

## 2.2 Power-Up Sequence

Console and most power-up tests reside on the I/O subsystem, not on the CPU nor on any other module on the system bus.

Figure 2-2 Power-Up Flow

PKW0432B-96

#### **Definitions**

**SROM**. The SROM is a 128-Kbit ROM on each CPU module. The ROM contains minimal diagnostics that test the Alpha chip and the path to the XSROM. Once the path is verified, it loads XSROM code into the Alpha chip and jumps to it.

**XSROM**. The XSROM, or extended SROM, contains back-up cache and memory tests, and a fail-safe loader. The XSROM code resides in sector 0 of FEPROM 0 on

the XBUS. Sector 2 of FEPROM 0 contains a duplicate copy of the code and is used if sector 0 is bad.

**FEPROM**. Two 1-Mbyte programmable ROMs are on the XBUS on PCIO. FEPROM 0 contains two copies of the XSROM, the OpenVMS and DIGITAL UNIX PALcode, and the SRM console and decompression code. FEPROM 1 contains the AlphaBIOS and NT HALcode. See Figure 2-3. These two FEPROMs can be flash updated. Refer to Appendix A.

Figure 2-3 Contents of FEPROMs

For the console to run, the path from the CPU to the XSROM must be functional. The XSROM resides in FEPROM0 on the XBUS, off the EISA bus, off PCI 0, off IOD 0. See Figure 2-4. This path is minimally tested by SROM.

Memory CPU Pair

Figure 2-4 Console Code Critical Path (4100 Block Diagram)

PKW0431E-96

The SROM contents are loaded into each CPU's I-cache and executed on power-up/reset. After testing the caches on each processor chip, it tests the path to the XSROM. Once this path is tested and deemed reliable, layers of the XSROM are loaded sequentially into the processor chip on each CPU. None of the SROM or XSROM power-up tests are run from memory—all run from the caches in the CPU chip, thus providing excellent diagnostic isolation. Later power-up tests, run under the console, are used to complete testing of the I/O subsystem.

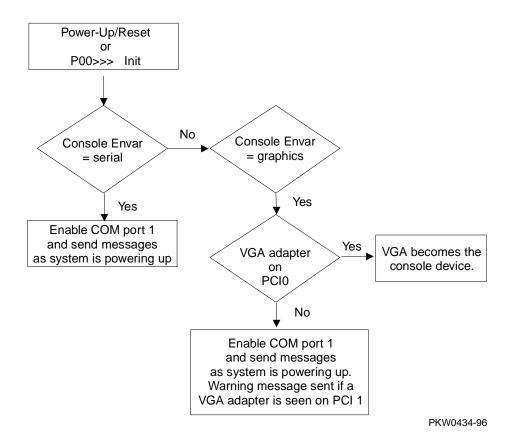

There are two console programs: the SRM console and the AlphaBIOS console, as detailed in the *AlphaServer 4100 System Drawer User's Guide* (EK–4100A–UG) and the *AlphaServer 4000 System Drawer User's Guide* (EK–4000A–UG). By default, the SRM console is always loaded and I/O system tests are run under it before the system loads AlphaBIOS. To load AlphaBIOS, the **os\_type** environment variable must be set to **NT** and the Halt button should be out (LED not lit). Otherwise, the SRM console continues to run.

## 2.3 SROM Power-Up Test Flow

The SROM tests the CPU chip and the path to the XSROM.

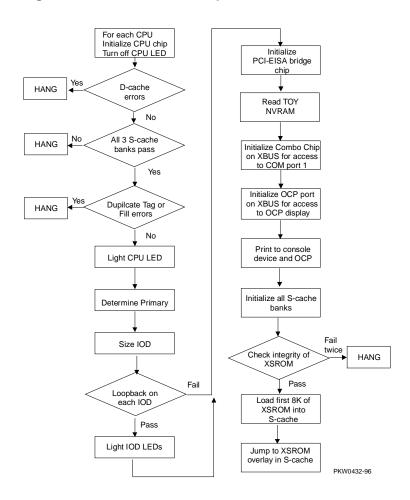

Figure 2-5 **SROM Power-Up Test Flow**

The Alpha chip built-in self-test tests the I-cache at power-up and upon reset.

Each CPU chip loads its SROM code into its I-cache and starts executing it. If the chip is partially functional, the SROM code continues to execute. However, if the chip cannot perform most of its functions, that CPU hangs and that CPU pass/fail LED remains off.

If the system has more than one CPU and at least one passes both the SROM and XSROM power-up tests, the system will bring up the console. The console checks the FW\_SCRATCH register where evidence of the power-up failure is left. Upon finding the error, the console sends these messages to COM1 and the OCP:

• COM1 (or VGA): Power-up tests have detected a problem with your system

• OCP: Power-up failure

Table 2-2 lists the tests performed by the SROM.

Table 2-2 SROM Tests

| Test Name                     | Logic Tested                                                                                                               |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| D-cache RAM March test        | D-cache access, D-cache data, D-cache address logic                                                                        |

| D-cache Tag RAM<br>March test | D-cache tag store RAM, D-cache bank address logic                                                                          |

| S-cache Data March test       | S-cache RAM cells, S-cache data path, S-cache address path                                                                 |

| S-cache Tag RAM<br>March test | S-cache tag store RAM, S-cache bank address logic                                                                          |

| I-cache Parity Error test     | I-cache parity error detection, ISCR register and error forcing logic, IC_PERR_STAT register and reporting logic           |

| D-cache Parity Error test     | D-cache parity error detection, DC_MODE register and parity error forcing logic, DC_PERR_STAT register and reporting logic |

| S-cache Parity Error<br>test  | S-cache parity error detection, AC_CTL register and parity error forcing logic, SC_STAT register and reporting logic       |

| IOD Access test               | Access to IOD CSRs, data path through CAP chip and MDP0 on each IOD, PCI0 A/D lines <31:0>                                 |

## 2.4 SROM Errors Reported

The SROM reports machine checks, pending interrupt/exception errors, and errors related to corruption of FEPROM 0. If SROM errors are fatal, the particular CPU will hang and only the CPU self-test pass LEDs and/or the LEDs on the system bus to PCI bus bridge module will indicate the failure.

#### Example 2-1 SROM Errors Reported at Power-Up

#### **Unexpected Machine Check (CPU Error)**

```

UNEX MCHK on CPU 0

EXC_ADR 42a9

EI_STAT ffffffff004ffffff

EI_ADDR fffffff000000801f

SC_STAT 0

SC ADDR FFFFFF0000005F2F

```

#### Pending Interrupt/Exception (CPU Error)

#### FEPROM Failures (PCI Motherboard Error)

```

Sctr 0 -XSROM headr PTTRN fail

Sctr 0 -XSROM headr CHKSM fail

Sctr 0 -XSROM code CHKSM fail

Sctr 2 -XSROM headr PTTRN fail

Sctr 2 -XSROM headr CHKSM fail

Sctr 2 -XSROM code CHKSM fail

```

## 2.5 XSROM Power-Up Test Flow

Once the SROM has completed its tests and verified the path to the FEPROM containing the XSROM code, it loads the first 8 Kbytes of XSROM into the primary CPU's S-cache and jumps to it.

XSROM banner to OCP/console device Run memory texts. Print trace to OCP/console dev. Print errors to OCP/console dev. Clear SC\_FHIT (force hit) Done message to console dev. Enable all 3 S-cache banks Boot processor Run B-cache tests redetermination Print errors to OCP/console dev. Done message to console dev. Primary Boot processor verifies checksum Fail redetermination Fail-safe of PAL/decomp/console loader Pass Initialize B-cache and enable duplicate tag Primary unloads PAL/ decompression code or fail-safe loader depending upon results of checksum Size system memory through I squared C bus Primary jumps to PALcode and starts the console Print mem info to console dev. Check for illegal memory config. Print warnings to console dev. Initialize all memory pairs. Secondaries alerted that console has started. They jump to and run PALcode joining the console. Note: The XSROM can only print to the console device if

Figure 2-6 XSROM Power-Up Flowchart

XSROM tests are described in Table 2-3. Failure indicates a CPU failure.

PKW0432A-96

output to the OCP.

the environment variable console = serial. It always sends

After jumping to the primary CPU's S-cache, the code then intentionally I-caches itself and is completely register based (no D-stream for stack or data storage is used). The only D-stream accesses are writes/reads during testing.

Each FEPROM has sixteen 64-Kbyte sectors. The first sector contains B-cache tests, memory tests, and a fail-safe loader. The second sector contains PALcode. The third sector contains a copy of the first sector. The remaining thirteen sectors contain the SRM console and decompression code.

NOTE: Memory tests are run during power-up and reset (see Table 2-4). They are also affected by the state of the memory\_test environment variable, which can have the following values:

FULL Test all memory

PARTIAL Test up to the first 256 Mbytes

NONE Test 32 Mbytes

Table 2-3 XSROM Tests

| Test | Test Name                                    | Logic Tested                                                                                                |

|------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| 11   | B-cache Tag Data Line test                   | Access to B-cache tags, shorts between tag data and its status and parity bits                              |

| 12   | B-cache Tag March test                       | B-cache tag store RAMs, B-cache STAT store RAMs                                                             |

| 13   | B-cache Data Line test                       | B-cache data lines to B-cache data RAMs,<br>B-cache read/write logic                                        |

| 14   | B-cache Data March test                      | B-cache data RAMs, CPU chip B-cache control, CPU chip B-cache address decode, INDEX_H<2x:6> (address bus)   |

| 15   | B-cache ECC Data Line test                   | CPU chip ECC generation and checking logic,<br>ECC lines from CPU chip to B-cache, B-cache<br>ECC RAMs      |

| 16   | B-cache Data ECC March test                  | Portion of B-cache data RAMs used for ECC                                                                   |