# AlphaStation 600 Series

# **Technical Reference Information**

Part Number: EK-AS800-RM. A01

#### July 1995

The purpose of this manual is to provide programming information that will assist system programmers in writing AlphaStation 600 System support code for their operating system.

**Revision Information:**

This is a new manual.

Digital Equipment Corporation Maynard, Massachusetts

#### July 1995

Digital Equipment Corporation makes no representation that the use of its products in the manner described in this publication will not infringe on existing or future rights, nor do the descriptions contained in this publication imply the granting of licenses to make, use, or sell equipment or software in accordance with the description.

Possession, use, or copying of the software described in this publication is authorized only pursuant to a valid written license from Digital or an authorized sublicensor.

© Digital Equipment Corporation 1995. All rights reserved.

The postpaid Reader's Comments form at the end of this document requests your critical evaluation to assist in preparing future documentation.

The following are trademarks of Digital Equipment Corporation: Alpha, AlphaStation and the DIGITAL logo.

The following are third-party trademarks:

Microsoft and Windows NT are registered trademarks of Microsoft Corporation.

SIMM is a trademark of Molex Corporation.

OSF/1 is a trademark of the Open Software Foundation, Inc.

All other trademarks and registered trademarks are the property of their respective holders.

[S2739]

## Contents

#### Preface

| Introduction      | XV  |

|-------------------|-----|

| Document Contents |     |

| Conventions       | xvi |

| Abbreviations     |     |

|                   |     |

### 1 AlphaStation 600 System Overview

| Introduction     | 1-1 |

|------------------|-----|

| ASIC Summary     | 1-5 |

| Hardware Jumpers |     |

|                  |     |

|                  |     |

### 2 AlphaStation 600 ASIC Overview

| Introduction                          |

|---------------------------------------|

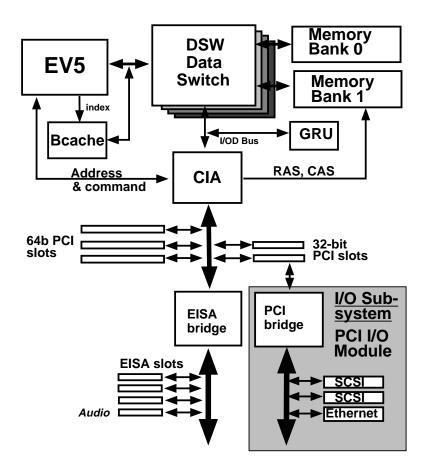

| The CIA ASIC                          |

| EV5 Instruction and Address Region2-2 |

| PCI Datapath                          |

| Memory Logic2-4                       |

| I/O Address Logic2-6                  |

| DMA Address Logic2-6                  |

| The DSW ASIC                          |

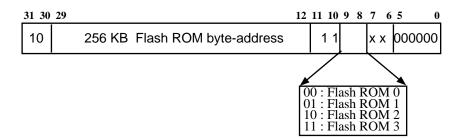

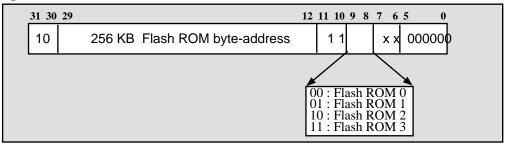

| Flash ROM2-7                          |

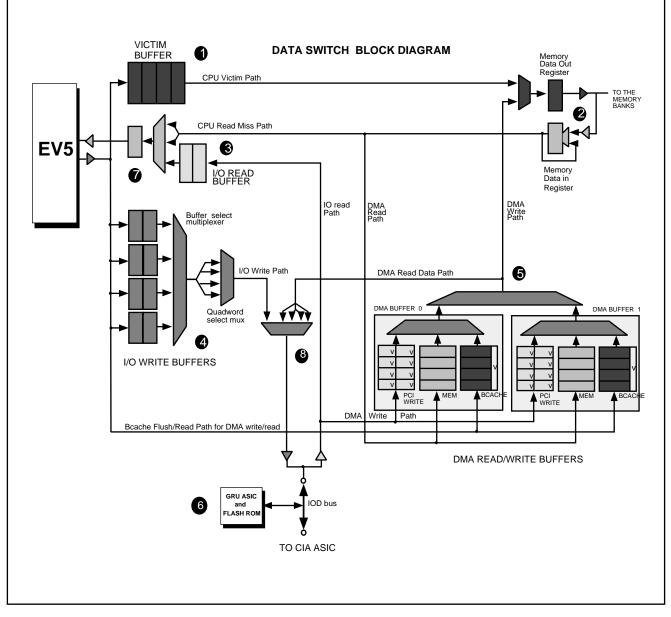

| CPU Memory Read2-8                    |

| CPU Memory Read with Victim2-9        |

| CPU I/O Read                          |

| CPU I/O Write                         |

| DMA Transactions                      |

| DMA Read                              |

| DMA Read Prefetching2-12              |

| DMA Write                             |

| MB Instruction                        |

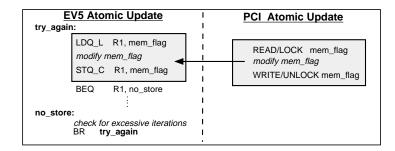

| LOCK Instructions                     |

| Locks to Uncached Space2-15           |

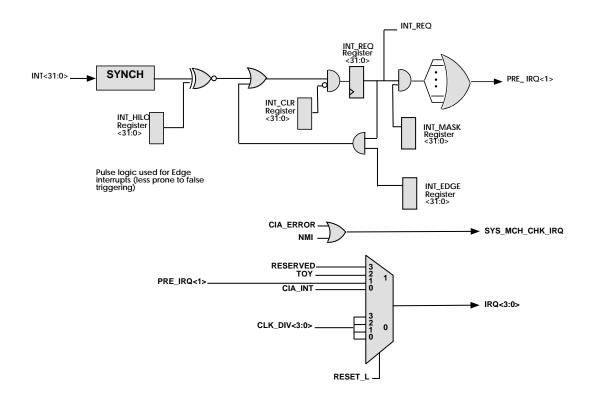

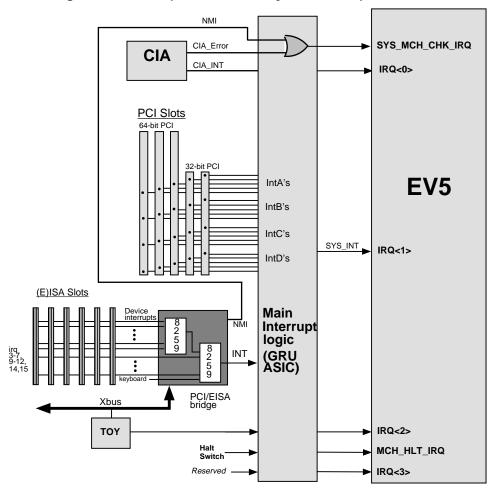

| GRU ASIC                              |

| IOD Interface                         |

| GRU Addressing2-16                    |

| Flash ROM Interface                   |

| Interrupt Logic                              |  |

|----------------------------------------------|--|

| Configuration Registers for Cache and Memory |  |

| Reset Logic                                  |  |

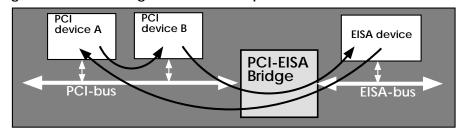

| AlphaStation 600 PCI-EISA Bridge             |  |

| ESC functionality                            |  |

| PCEB Functionality                           |  |

| PCI-to-EISA Address Decode                   |  |

| PC Compatibility Addressing and Holes        |  |

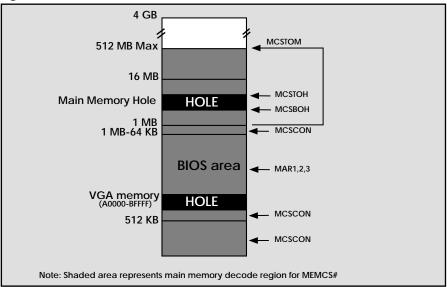

| MEMCS#                                       |  |

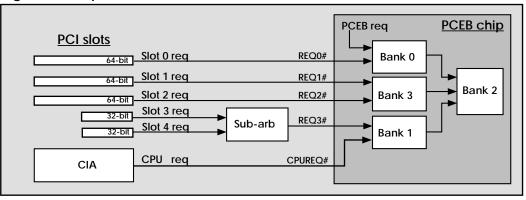

| PCI Arbitration                              |  |

| PCI Arbitration - Power-Up                   |  |

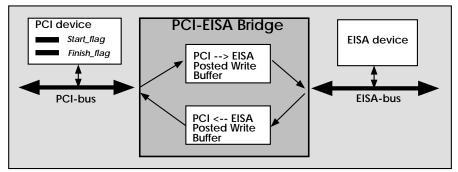

| Data Buffering in the PCEB                   |  |

|                                              |  |

## 3 AlphaStation 600 Addressing

| Introduction                                       | 3-1  |

|----------------------------------------------------|------|

| Address Mapping Introduction                       | 3-1  |

| PCI Addressing                                     |      |

| CPU Address Space                                  |      |

| CPU Address <38:35>                                |      |

| Cacheable Memory Space                             | 3-7  |

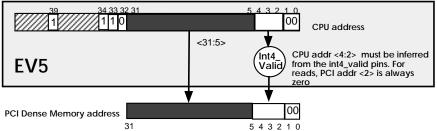

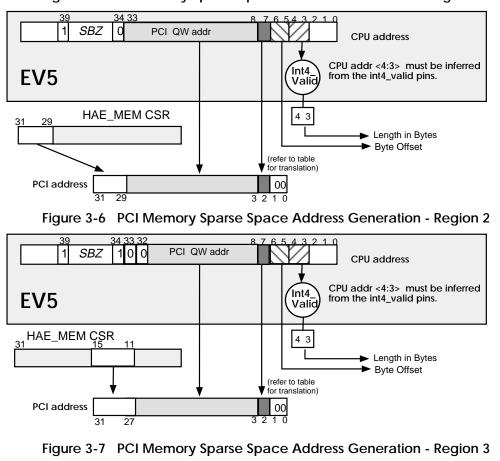

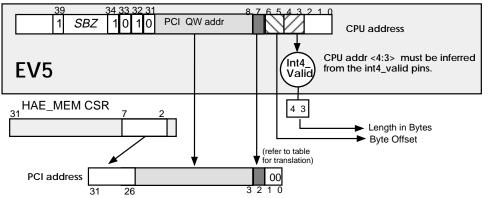

| PCI Sparse Memory Space                            | 3-8  |

| Hardware Extension Registers (HAE)                 |      |

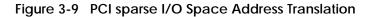

| PCI Sparse I/O Space                               | 3-13 |

| PCI Configuration Space                            |      |

| PCI Special/Interrupt Cycles                       | 3-18 |

| Hardware Specific and Miscellaneous Register Space | 3-19 |

| PCI to Physical Memory Addressing                  | 3-19 |

| Direct-mapped Addressing                           | 3-22 |

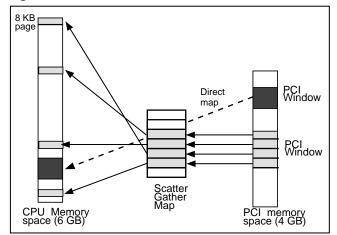

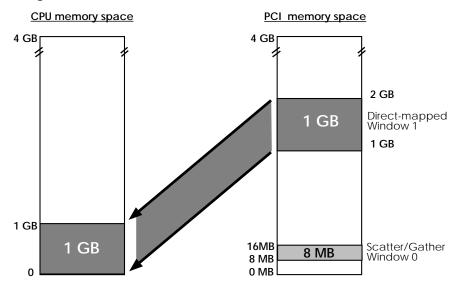

| Scatter/Gather Addressing                          | 3-23 |

| Scatter/Gather TLB                                 | 3-24 |

| PCI Window Suggested Use                           | 3-26 |

| PC Compatibility Addressing and Holes              | 3-27 |

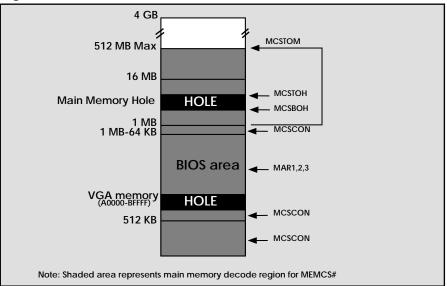

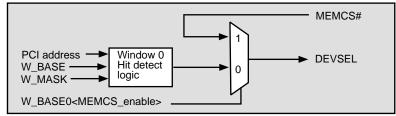

| MEMCS <sup>*</sup> #                               | 3-27 |

|                                                    |      |

### 4 Modules

| Memory MotherBoard   | 4-1 |

|----------------------|-----|

| Presence Detect Bits |     |

| Cache SIMM           | 4-3 |

| I/O Subsystem Module |     |

| Major Components     |     |

|                      |     |

## 5 Power Up and Reset

| Introduction   | 5-1 |

|----------------|-----|

| Power Up       | 5-1 |

| Halt and Reset |     |

|                |     |

## 6 AlphaStation 600 Physical Partitioning

| Introduction                                 |

|----------------------------------------------|

| Hardware Jumpers                             |

| Fan Fail Detect Jumpers6-1                   |

| Flash ROM Write Jumper6-2                    |

| Alternate Console Jumper6-2                  |

| Secure Console Jumper                        |

| SROM Code Select Jumper 6-2                  |

| EV5 clock multiple DIP switch6-3             |

| Physical Organization                        |

| I/O Subsystem Organization                   |

| AlphaStation 600 Module Overview6-11         |

| System Board6-11                             |

| Memory Motherboard6-11                       |

| Cache SIMM                                   |

| PCI Options                                  |

| EISA Options                                 |

| AlphaStation 600 SystemBoard - ASICs         |

| EV5 CPU                                      |

| CIA ASIC                                     |

| AlphaStation 600 I/O & External Interconnect |

| Serial Ports6-38                             |

| Parallel Port6-38                            |

| Keyboard/Mouse Connectors6-39                |

| PCI Connector                                |

| EISA Connector6-42                           |

| Power Connectors                             |

| Fan Connectors6-45                           |

| OCP Connector                                |

| Floppy Connector                             |

| Serial ROM Connector                         |

| System Testability Features                  |

### 7 Control and Status Registers

| Register Types                                 | . 7-1 |

|------------------------------------------------|-------|

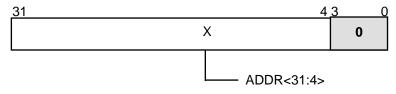

| Register Addressing                            |       |

| General Registers                              |       |

|                                                |       |

| Memory Control Registers                       | . 7-3 |

| PCI Address-related Registers                  |       |

| Scatter/Gather Address Translation Registers   |       |

| Flash ROM Space                                |       |

| Addressing                                     |       |

| EV5 Configuration Registers                    |       |

| EV5 Registers                                  |       |

| General CIA Registers - Description            |       |

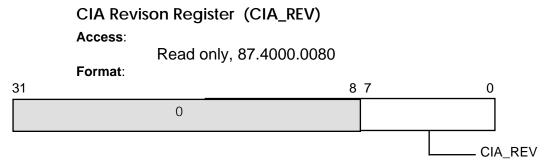

| CIA Revison Register (CIA_REV)                 |       |

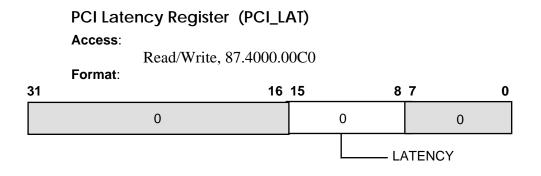

| PCI Latency Register (PCI_LAT)                 |       |

| CIA Control Register (CIA_CTRL)                |       |

| Hardware Address Extension Register (HAE_MEM)  |       |

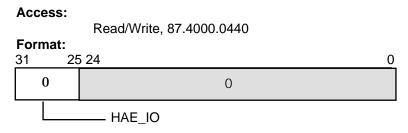

| Hardware Address Extension Register (HAE_IO)   |       |

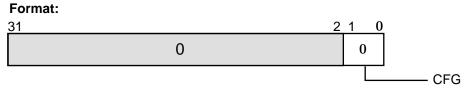

| Configuration Type Register (CFG)              |       |

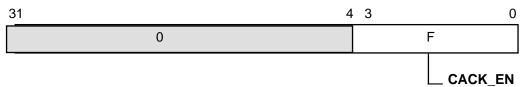

| CIA Acknowledgement Control Register (CACK_EN) |       |

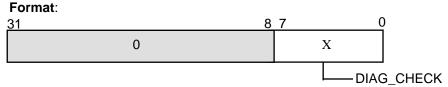

| Diagnostic Registers - description             |       |

| CIA Diagnostic Control Register (CIA_DIAG)                                                                  |

|-------------------------------------------------------------------------------------------------------------|

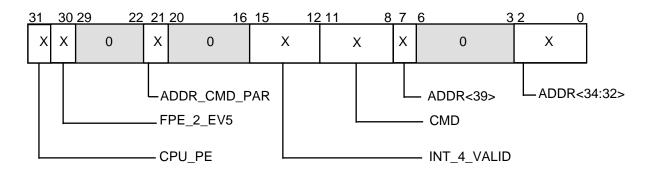

| CPU Error Information Register 0 (CPU_ERR0)                                                                 |

| CPU Error Information Register 1 (CPU_ERR1)                                                                 |

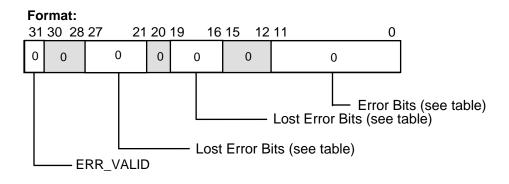

| CIA Error Register (CIA_ERR)                                                                                |

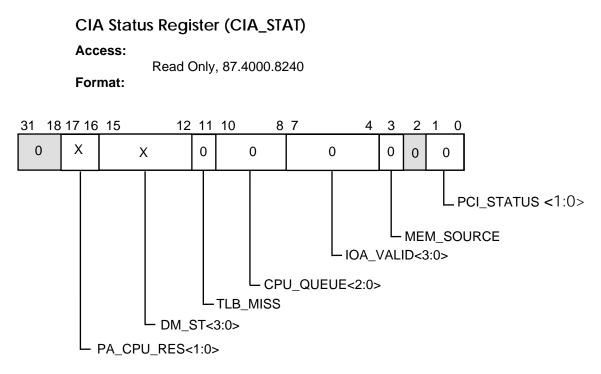

| CIA Status Register (CIA_STAT)                                                                              |

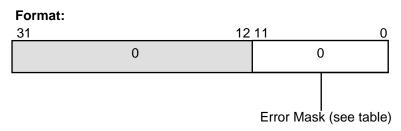

| CIA Error Mask Register (ERR_MASK)                                                                          |

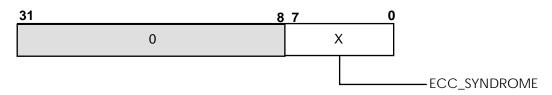

| CIA Error Syndrome Register (CIA_SYN)                                                                       |

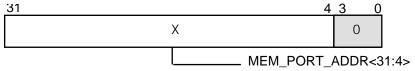

| CIA Memory Port Status Register 0 (MEM_ERR0)                                                                |

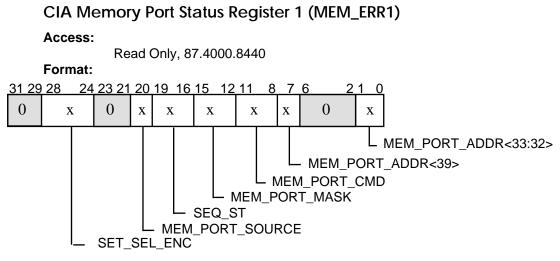

| CIA Memory Port Status Register 1 (MEM_ERR1)                                                                |

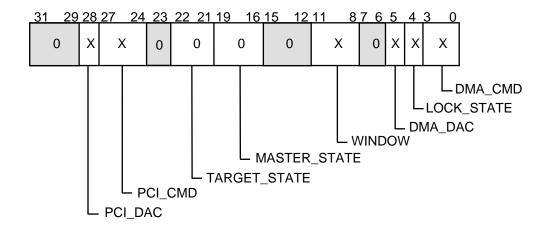

| PCI Error Register 0 (PCI_ERR0)7-35                                                                         |

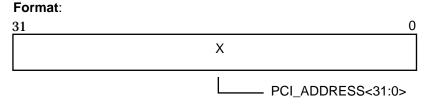

| PCI Error Register 1 (PCI_ERR1)7-37                                                                         |

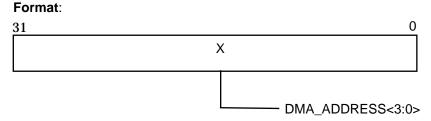

| PCI Error Register 2 (PCI_ERR2)7-38                                                                         |

| Memory Control Registers - description                                                                      |

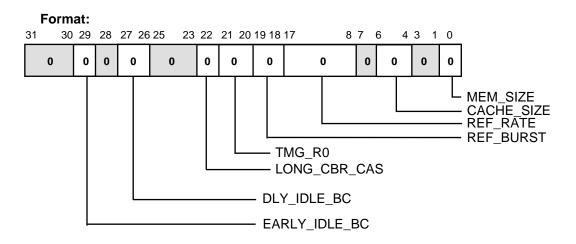

| Memory Configuration Register (MCR)                                                                         |

| Memory Base Address Registers 0-E (MBA0-E)                                                                  |

| Memory Timing Registers (TMG0-TMG2)                                                                         |

| 7-44                                                                                                        |

| PCI Address-related Registers - Description                                                                 |

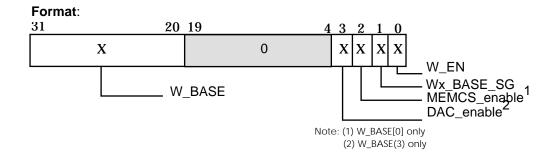

| Scatter/Gather Translation Buffer Invalidate Register (TBIA) 7-45<br>Window Base Registers (Wx_BASE, x=0-3) |

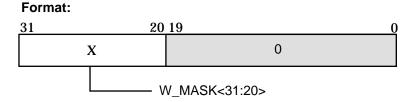

| Window Mask Registers (Wx_MASE, x=0-3)                                                                      |

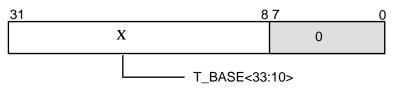

| Translated Base Registers (Tx_BASE, x=0-3)                                                                  |

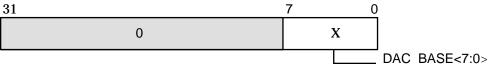

| Window DAC Base Register (W_DAC)                                                                            |

| Scatter/Gather Address Translation Registers                                                                |

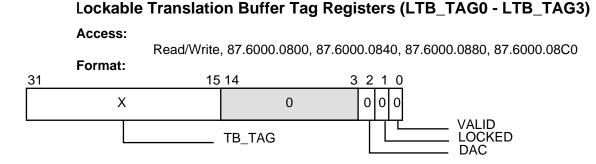

| Lockable Translation Buffer Tag Registers (LTB_TAG0 - LTB_TAG3) 7-53                                        |

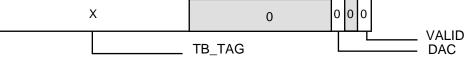

| Translation Buffer Tag Registers (TB_TAG0 - TB_TAG3)                                                        |

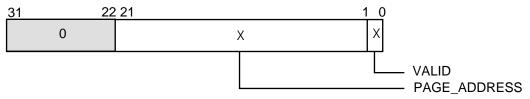

| Translation Buffer Page Register (TBx_PAGEn)                                                                |

| GRU ASIC - related Registers                                                                                |

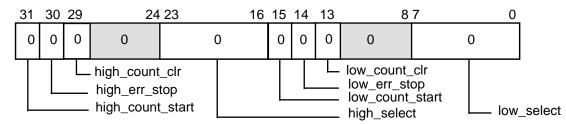

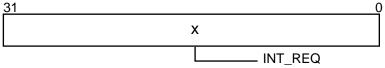

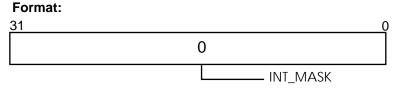

| Interrupt Mask Register (INT_MASK)                                                                          |

| Interrupt Level/Edge Select Register (INT_EDGE)                                                             |

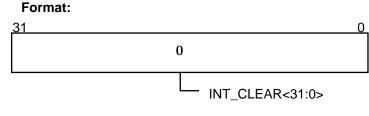

| Interrupt Clear Register (INT_CLEAR)                                                                        |

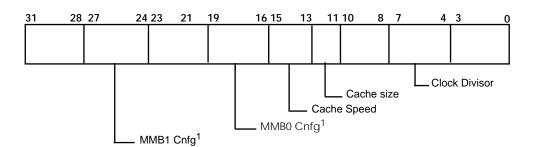

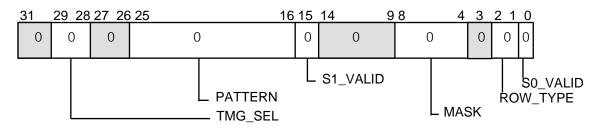

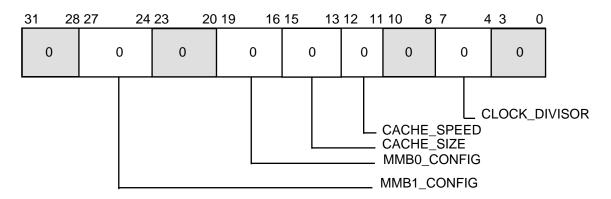

| Cache & Memory Configuration Register (CACHE_CNFG)                                                          |

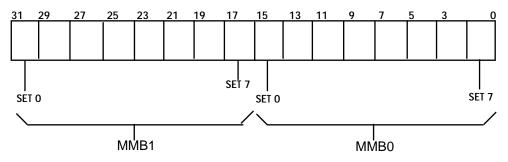

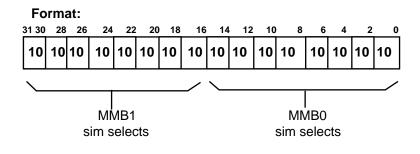

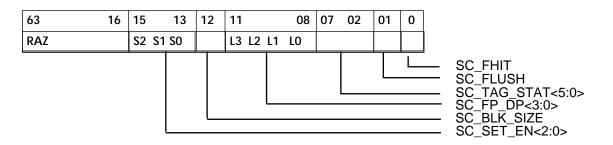

| SET Configuration Register (SCR)                                                                            |

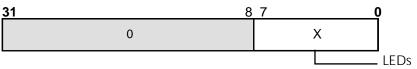

| LED Register (LED)                                                                                          |

| Reset Register (RESET)7-64                                                                                  |

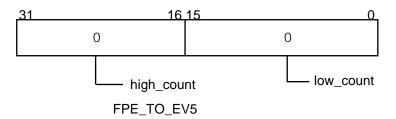

| EV5 Configuration Registers - description                                                                   |

| Scache Control Register, SC_CTL7-65                                                                         |

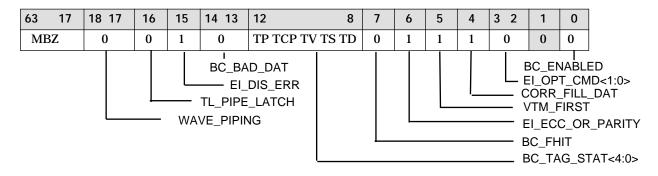

| Bcache Control Register, BC_CONTROL                                                                         |

| Bcache Configuration Register, (BC_CONFIG)                                                                  |

|                                                                                                             |

## 8 Hardware Exceptions and Interrupts

| Introduction                    |  |

|---------------------------------|--|

| System Interrupts               |  |

| SYS_MCH_CHK_IRQ                 |  |

| Halt/Reset Switches             |  |

| EV5 Error Handling              |  |

| PCI Error Handling              |  |

| PERR# Implications              |  |

| SERR# implications              |  |

| AlphaStation 600 Error Handling |  |

| CIA ASIC Error Registers        |  |

| CIA Error Mask Register         |  |

| 5                               |  |

| CIA Error Reporting8                                        | -16 |

|-------------------------------------------------------------|-----|

| CIA Detected Errors                                         | -16 |

| Error Insertion                                             | -21 |

| Force Error Registers8                                      | -21 |

| Accessing Main Memory Via CPU Uncached Space                | -21 |

| Writing Bad ECC Into Memory                                 | -21 |

| Machine Check Logout Data Structure8                        |     |

| Correctable Error Logout Frame                              | -23 |

| Deciphering a Correctable Error Machine Check Logout Frame8 | -25 |

| ECC Syndromes for Single-Bit Errors                         | -27 |

| Uncorrectable Error Logout Frame                            | -28 |

| Deciphering an Uncorrectable Error Logout Frame             | -35 |

## 9 AlphaStation 600 System Initialization

| Introduction                                    |  |

|-------------------------------------------------|--|

| Serial ROM Performed Initialization             |  |

| System Firmware Performed Initialization        |  |

| Overview of Sizing the PCI Bus                  |  |

| Sizing/Configuring the PCI Bus                  |  |

| Accessing PCI Bus Configuration                 |  |

| PCI-PCI Bridge Configuration                    |  |

| Driver Initiated PCI Configuration              |  |

| PCI-EISA Bridge Configuration                   |  |

| COM1 (87312) Device Initialization              |  |

| COM2 (87312) Device Initialization              |  |

| Parallel Port (87312) Device Initialization     |  |

| Floppy Controller (87312) Device Initialization |  |

| Keyboard/Mouse Device Initialization            |  |

| Battery Backed SRAM Device Initialization       |  |

| TOY Driver Device Initialization                |  |

| NCR810 Driver Device Initialization             |  |

| TULIP Driver Device Initialization              |  |

| TGA Driver Device Initialization                |  |

| Memory Initialization                           |  |

| Miscellaneous CIA Related Initialization        |  |

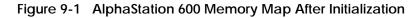

| Address Map                                     |  |

| ISA Devices Address Map                         |  |

| Software Considerations                         |  |

|                                                 |  |

### 10 AlphaStation 600 PCI-EISA Bridge

| Introduction                                     |       |

|--------------------------------------------------|-------|

| Related Documentation                            |       |

| ESC Functionality                                |       |

| ESC Registers                                    |       |

| PCEB Functionality                               |       |

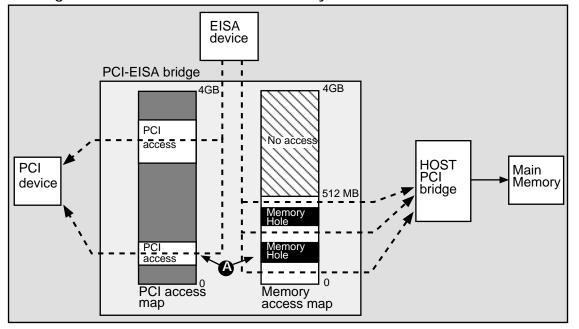

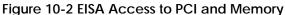

| PCI-to-EISA Address Decode                       |       |

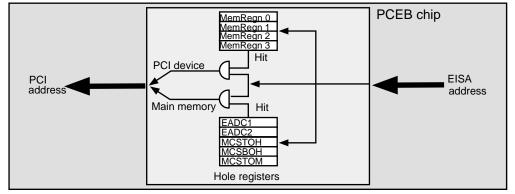

| PC Compatibility Addressing and Holes            |       |

| MEMCS# Details                                   |       |

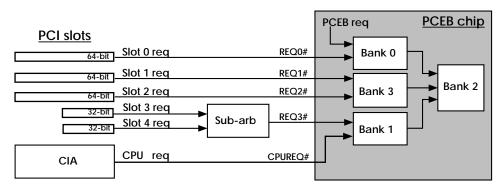

| PCI Arbitration                                  | 10-13 |

| PCI Arbitration - Power-up                       | 10-13 |

| Potential for PCI-EISA Bridge Starvation         |       |

| Coherency Implications                           |       |

| Coherency: Posted Write Buffer in the PCI Device |       |

| PCI Deadlock Avoidance Rule | 10-16 |

|-----------------------------|-------|

| Coherency: CIA and FLSHREQ# |       |

| Guaranteed Access Time Mode |       |

| Gat-Mode Software Notes     |       |

| Data Buffering in the PCEB  | 10-18 |

## 11 System Coherency

| Introduction 1                                            | 1-1 |

|-----------------------------------------------------------|-----|

| Referenced Documents 1                                    | 1-1 |

| Alpha System Reference Manual1                            | 1-1 |

| PCI Local Bus Specification1                              | 1-1 |

| NCR 53C820                                                | 1-1 |

| Other Devices1                                            | 1-1 |

| Coherency Summary1                                        | 1-1 |

| Classification of Coherency Situations1                   | 1-2 |

| Generic Event Types in the AlphaStation 600 System1       | 1-2 |

| Possible Write - Read and Write - Write interactions 1    | 1-4 |

| Basic Properties of the AlphaStation 600 System1          | 1-5 |

| Analysis of Interactions with Writes1                     | 1-6 |

| Data fails to make it to a later read1                    | 1-6 |

| Data overwrites some later write11                        | -12 |

| Data is overwritten before readers are finished with it11 | -19 |

| Data fails to make it to destination11                    | -19 |

| Side Effects happen out of order11                        |     |

| Analysis of I/O Page Table Modification Interactions11    | -22 |

| Failure to use the latest I/O Page Table State            | -22 |

| I/O Page Table Changed While In Use11                     | -24 |

| Triangle Inequality for I/O Busses 11                     | -25 |

## A CIA - DSW Command Fields (CMC and IOC)

| Introduction A | 4- | 1 |

|----------------|----|---|

|----------------|----|---|

## Figures

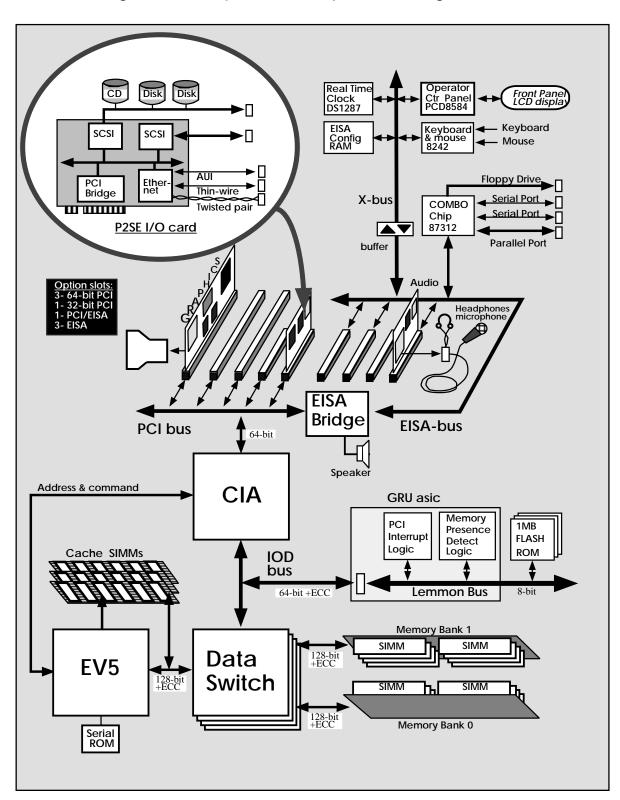

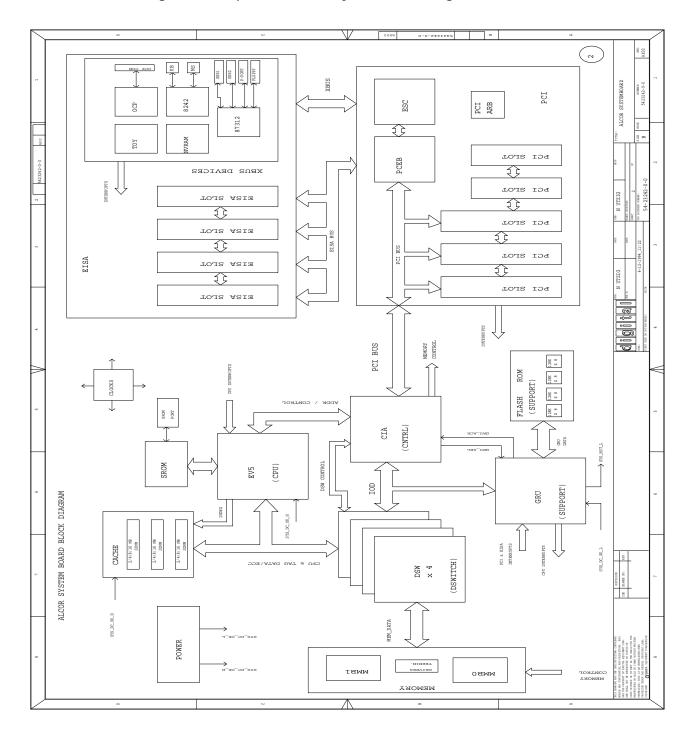

| Figure 1-1  | The AlphaStation 600 System Block Diagram1-3    |

|-------------|-------------------------------------------------|

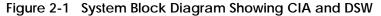

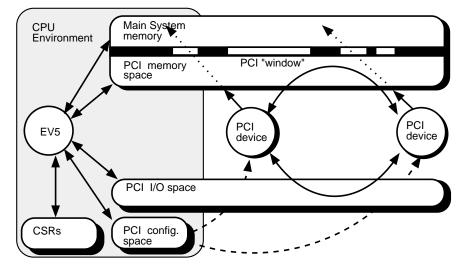

| Figure 2-1  | System Block Diagram Showing CIA and DSW 2-1    |

| Figure 2-2  | The CIA Block Diagram2-2                        |

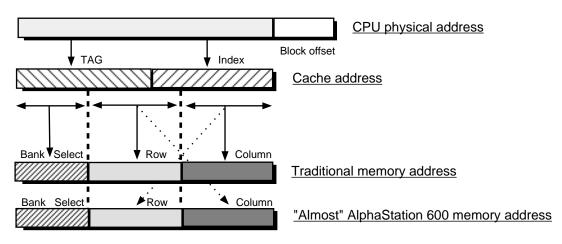

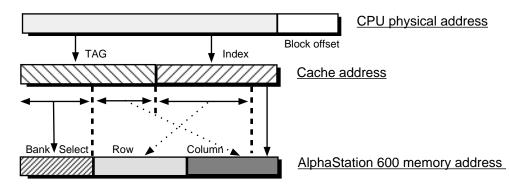

| Figure 2-3  | Memory Address Swizzling2-4                     |

| Figure 2-4  | Victim Aliasing2-5                              |

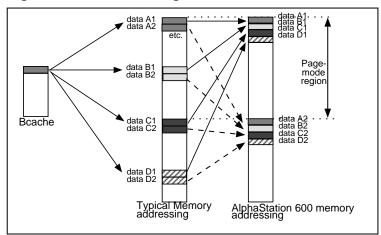

| Figure 2-5  | AlphaStation 600 System Memory Addressing2-5    |

| Figure 2-6  | The Data Switch Block Diagram2-8                |

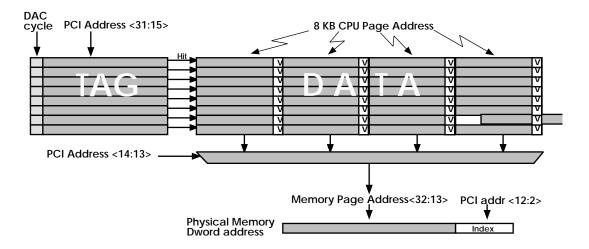

| Figure 2-7  | Scatter/Gather TLB                              |

| Figure 2-8  | Flash ROM Address scheme2-18                    |

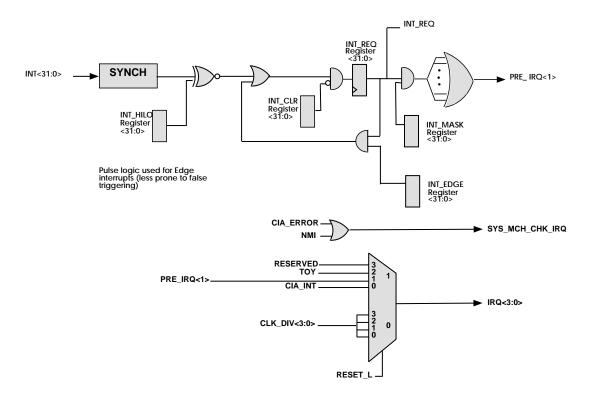

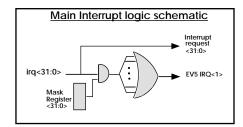

| Figure 2-9  | GRU Interrupt Logic2-18                         |

| Figure 2-10 | Cache and Memory Configuration Register2-19     |

| Figure 2-11 | SET Configuration <sup>1</sup> 2-19             |

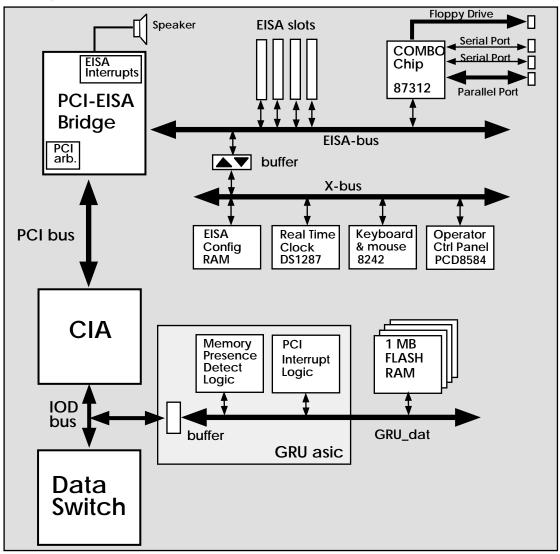

| Figure 2-12 | AlphaStation 600 System Standard I/O Busses2-20 |

| Figure 2-13 | AlphaStation 600 System PCI arbiter scheme2-22  |

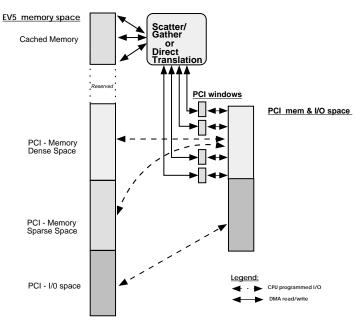

| Figure 3-1  | Address Space Overview                          |

| Figure 3-2  | CPU and DMA Reads and Writes                    |

|             |                                                 |

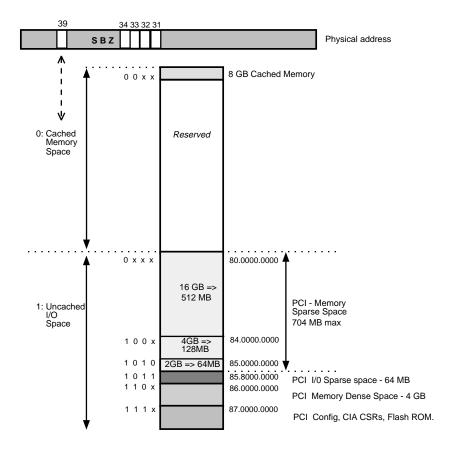

| Figure 3-3                                                                                                                                                                                                                                                                                                                 | CPU Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3-4                                                                                                                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3-4                                                                                                                                                                                                                                                                                                                 | Dense Space Address Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3-8                                                                                                                                                                                                                                                                         |

| Figure 3-5                                                                                                                                                                                                                                                                                                                 | CI Memory Sparse Space Address Generation - Region 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-11                                                                                                                                                                                                                                                                        |

| Figure 3-6                                                                                                                                                                                                                                                                                                                 | PCI Memory Sparse Space Address Generation - Region 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-11                                                                                                                                                                                                                                                                        |

| Figure 3-7                                                                                                                                                                                                                                                                                                                 | PCI Memory Sparse Space Address Generation - Region 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-11                                                                                                                                                                                                                                                                        |

| Figure 3-8                                                                                                                                                                                                                                                                                                                 | AlphaStation 600 System PCI and (E)ISA I/O Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3-13                                                                                                                                                                                                                                                                        |

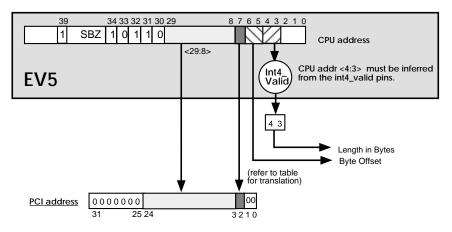

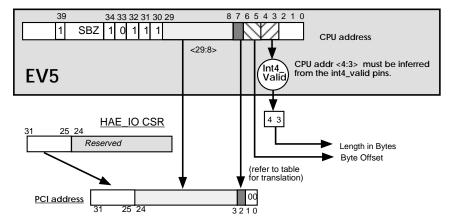

| Figure 3-9                                                                                                                                                                                                                                                                                                                 | PCI sparse I/O Space Address Translation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3-15                                                                                                                                                                                                                                                                        |

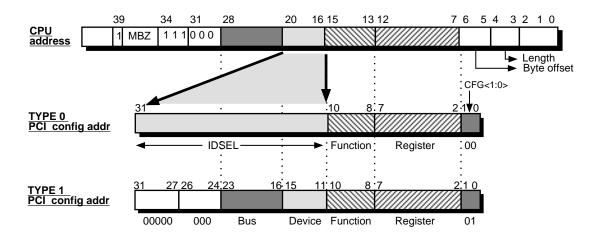

| Figure 3-10                                                                                                                                                                                                                                                                                                                | PCI Configuration Space Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3-16                                                                                                                                                                                                                                                                        |

| Figure 3-11                                                                                                                                                                                                                                                                                                                | PCI Configuration Space Read/Write Encodings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-17                                                                                                                                                                                                                                                                        |

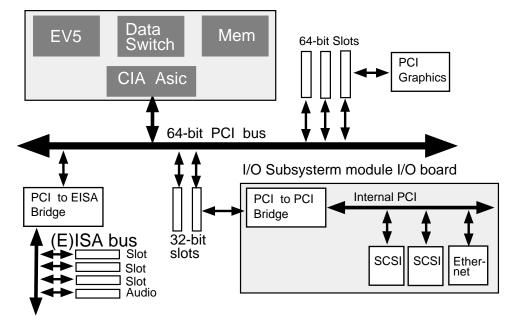

| Figure 3-12                                                                                                                                                                                                                                                                                                                | AlphaStation 600 System PCI Bus Hierarchy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3-18                                                                                                                                                                                                                                                                        |

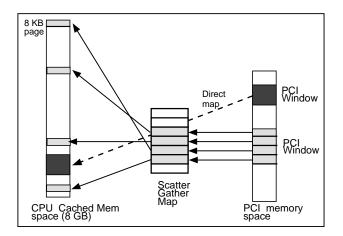

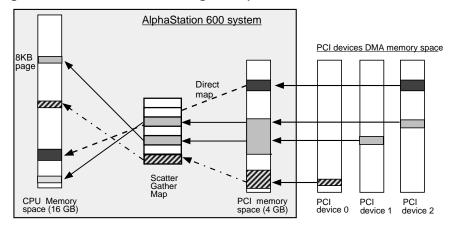

| Figure 3-13                                                                                                                                                                                                                                                                                                                | PCI DMA Addressing Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3-21                                                                                                                                                                                                                                                                        |

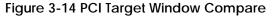

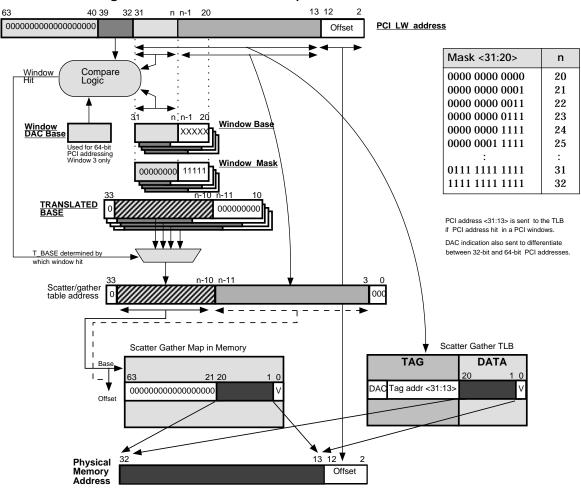

| Figure 3-14                                                                                                                                                                                                                                                                                                                | PCI Target Window Compare                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                             |

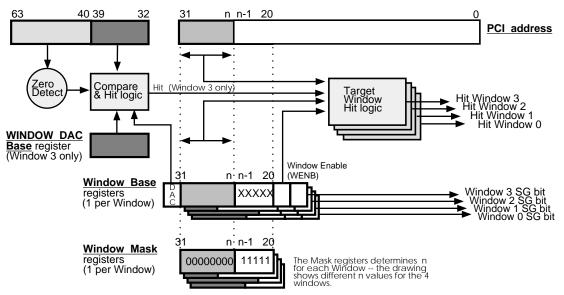

| Figure 3-15                                                                                                                                                                                                                                                                                                                | Direct-mapped Translation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3-23                                                                                                                                                                                                                                                                        |

| Figure 3-16                                                                                                                                                                                                                                                                                                                | Scatter/Gather PTE Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3-24                                                                                                                                                                                                                                                                        |

| Figure 3-17                                                                                                                                                                                                                                                                                                                | Scatter/Gather Associative TLB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3-25                                                                                                                                                                                                                                                                        |

| Figure 3-18                                                                                                                                                                                                                                                                                                                | Scatter/Gather Map Translation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3-26                                                                                                                                                                                                                                                                        |

| Figure 3-19                                                                                                                                                                                                                                                                                                                | Default PCI Window Allocation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                             |

| Figure 3-20                                                                                                                                                                                                                                                                                                                | MEMCS# Decode Area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                             |

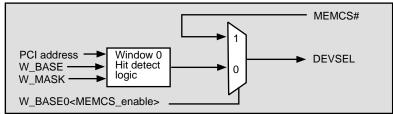

| Figure 3-21                                                                                                                                                                                                                                                                                                                | MEMCS# Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-28                                                                                                                                                                                                                                                                        |

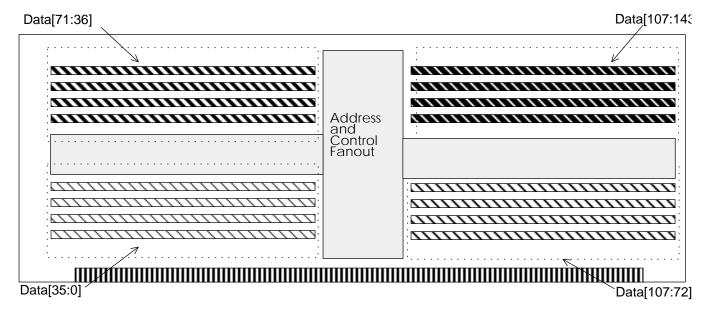

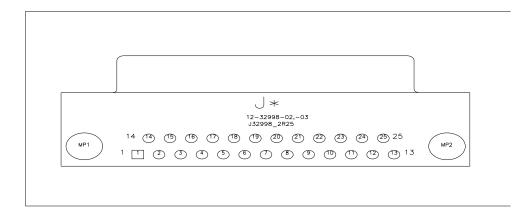

| Figure 4-1                                                                                                                                                                                                                                                                                                                 | MMB Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                             |

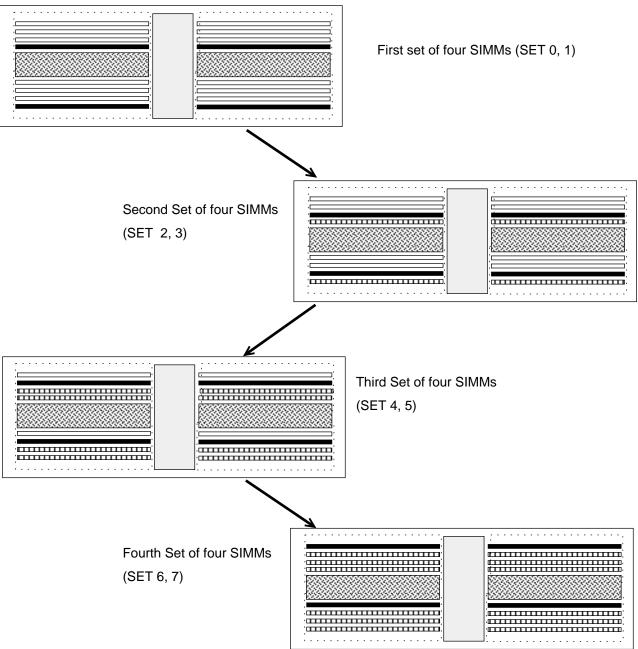

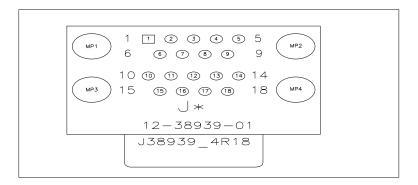

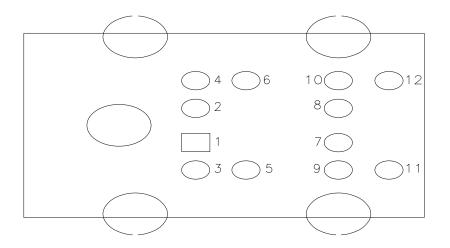

| Figure 4-2                                                                                                                                                                                                                                                                                                                 | SIMM Population Order                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                             |

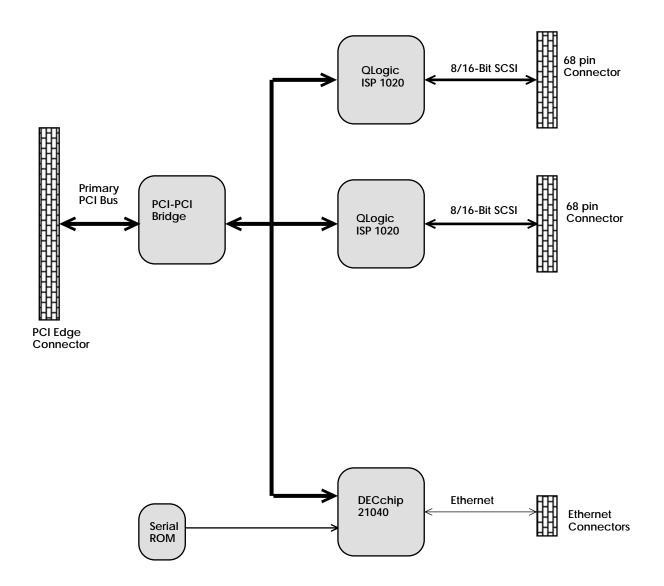

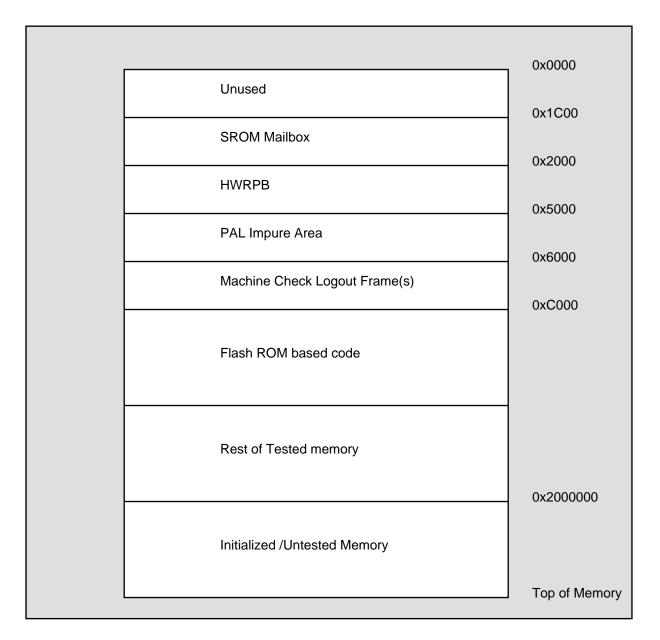

| Figure 4-3                                                                                                                                                                                                                                                                                                                 | I/O Subsystem Module Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                             |

| Figure 6-1                                                                                                                                                                                                                                                                                                                 | AlphaStation 600 System Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                             |

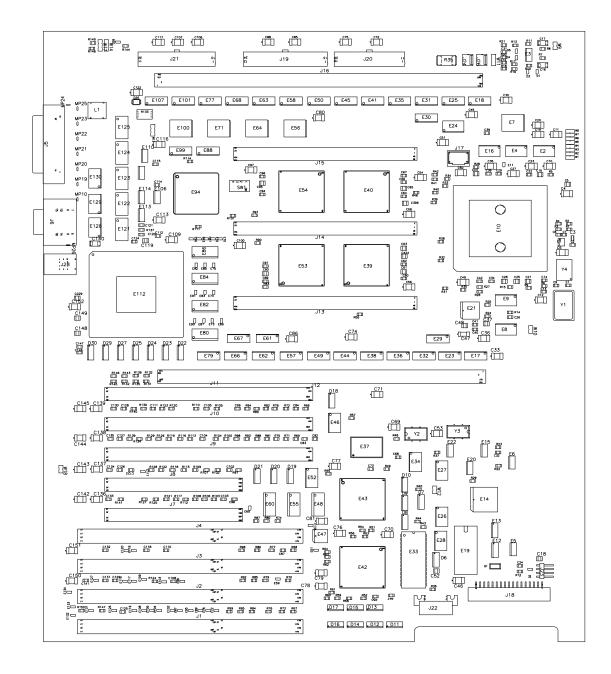

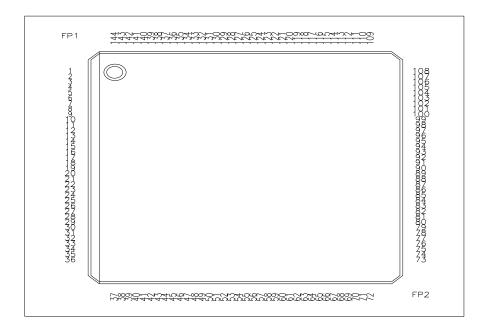

| Figure 6-2                                                                                                                                                                                                                                                                                                                 | AlphaStation 600 System Board Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                             |

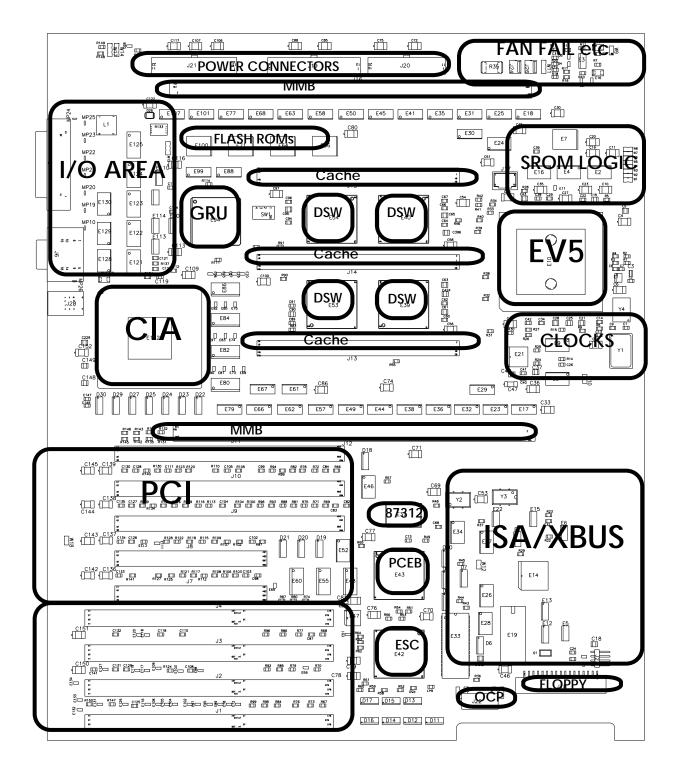

| Figure 6-3                                                                                                                                                                                                                                                                                                                 | AlphaStation 600 System Board Function Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                             |

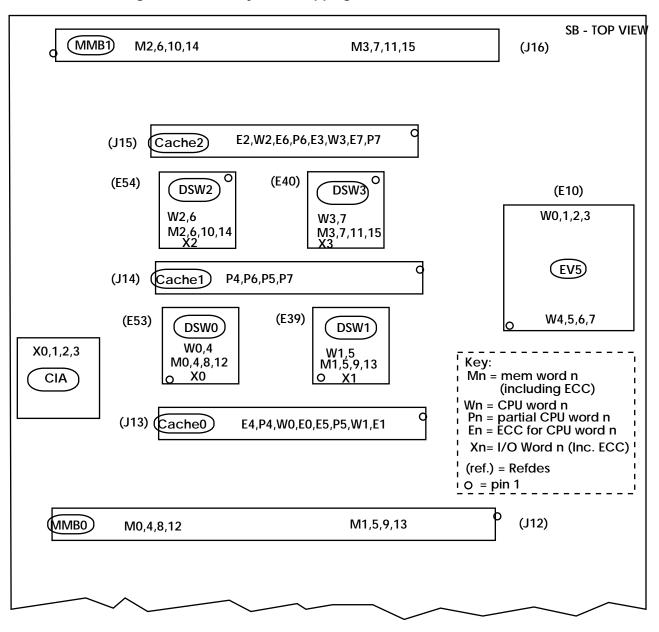

| Figure 6-4                                                                                                                                                                                                                                                                                                                 | Memory Data Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                             |

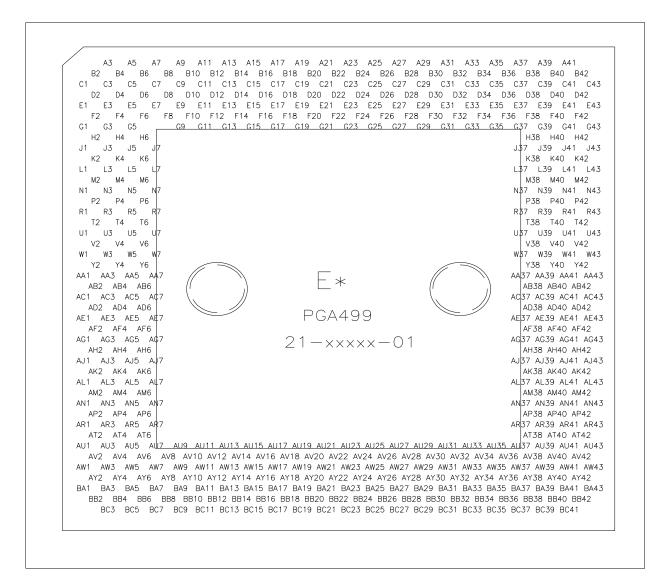

| Figure 6-5                                                                                                                                                                                                                                                                                                                 | EV5 CPU Package - Top View                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                             |

| 0                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                             |

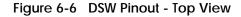

| Figure 6-6                                                                                                                                                                                                                                                                                                                 | DSW Pinout - Top View                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6-21                                                                                                                                                                                                                                                                        |

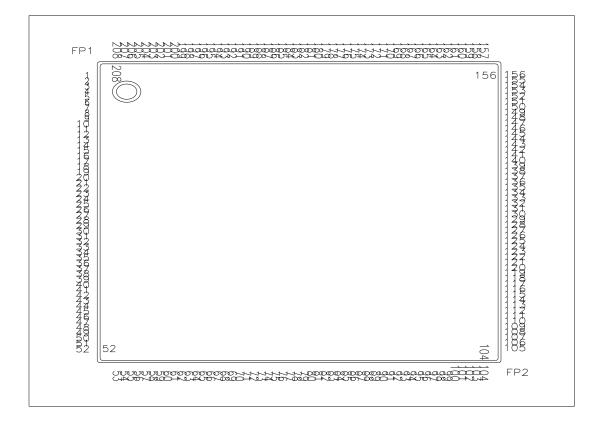

| Figure 6-6<br>Figure 6-7                                                                                                                                                                                                                                                                                                   | DSW Pinout - Top View<br>GRU Pinout - Top View                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                             |

| Figure 6-7                                                                                                                                                                                                                                                                                                                 | GRU Pinout - Top View                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6-26                                                                                                                                                                                                                                                                        |

| Figure 6-7<br>Figure 6-8                                                                                                                                                                                                                                                                                                   | GRU Pinout - Top View<br>CIA Pinout - Top View                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6-26<br>6-31                                                                                                                                                                                                                                                                |

| Figure 6-7<br>Figure 6-8<br>Figure 6-9                                                                                                                                                                                                                                                                                     | GRU Pinout - Top View<br>CIA Pinout - Top View<br>Serial Port Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6-26<br>6-31<br>6-38                                                                                                                                                                                                                                                        |

| Figure 6-7<br>Figure 6-8<br>Figure 6-9<br>Figure 6-10                                                                                                                                                                                                                                                                      | GRU Pinout - Top View<br>CIA Pinout - Top View<br>Serial Port Connector<br>Parallel Port Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6-26<br>6-31<br>6-38<br>6-39                                                                                                                                                                                                                                                |

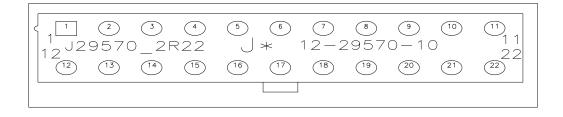

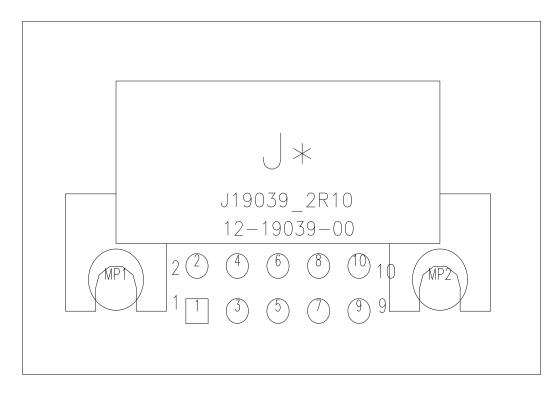

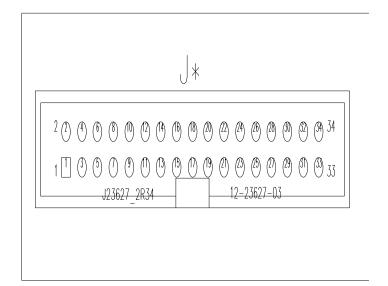

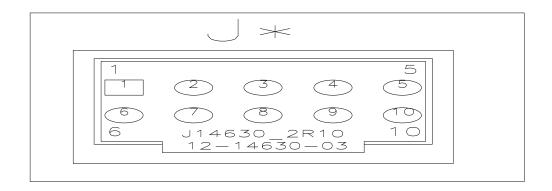

| Figure 6-7<br>Figure 6-8<br>Figure 6-9<br>Figure 6-10<br>Figure 6-11                                                                                                                                                                                                                                                       | GRU Pinout - Top View<br>CIA Pinout - Top View<br>Serial Port Connector<br>Parallel Port Connector<br>Keyboard/Mouse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6-26<br>6-31<br>6-38<br>6-39<br>6-39                                                                                                                                                                                                                                        |

| Figure 6-7<br>Figure 6-8<br>Figure 6-9<br>Figure 6-10<br>Figure 6-11<br>Figure 6-12                                                                                                                                                                                                                                        | GRU Pinout - Top View<br>CIA Pinout - Top View<br>Serial Port Connector<br>Parallel Port Connector<br>Keyboard/Mouse<br>Control Power Connector Pinout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6-26<br>6-31<br>6-38<br>6-39<br>6-39<br>6-44                                                                                                                                                                                                                                |

| Figure 6-7<br>Figure 6-8<br>Figure 6-9<br>Figure 6-10<br>Figure 6-11<br>Figure 6-12<br>Figure 6-13                                                                                                                                                                                                                         | GRU Pinout - Top View<br>CIA Pinout - Top View<br>Serial Port Connector<br>Parallel Port Connector<br>Keyboard/Mouse<br>Control Power Connector Pinout<br>OCP Connector Pinout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6-26<br>6-31<br>6-38<br>6-39<br>6-39<br>6-44<br>6-47                                                                                                                                                                                                                        |

| Figure 6-7<br>Figure 6-8<br>Figure 6-9<br>Figure 6-10<br>Figure 6-11<br>Figure 6-12<br>Figure 6-13<br>Figure 6-14                                                                                                                                                                                                          | GRU Pinout - Top View<br>CIA Pinout - Top View<br>Serial Port Connector<br>Parallel Port Connector<br>Keyboard/Mouse<br>Control Power Connector Pinout<br>OCP Connector Pinout<br>Floppy Connector Pinout                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6-26<br>6-31<br>6-38<br>6-39<br>6-39<br>6-44<br>6-47<br>6-48                                                                                                                                                                                                                |

| Figure 6-7<br>Figure 6-8<br>Figure 6-9<br>Figure 6-10<br>Figure 6-11<br>Figure 6-12<br>Figure 6-13<br>Figure 6-14<br>Figure 6-15                                                                                                                                                                                           | GRU Pinout - Top View<br>CIA Pinout - Top View<br>Serial Port Connector<br>Parallel Port Connector<br>Keyboard/Mouse<br>Control Power Connector Pinout<br>OCP Connector Pinout<br>Floppy Connector Pinout<br>SROM Port Connector Pinout                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6-26<br>6-31<br>6-38<br>6-39<br>6-39<br>6-44<br>6-47<br>6-48<br>6-49                                                                                                                                                                                                        |

| Figure 6-7<br>Figure 6-8<br>Figure 6-9<br>Figure 6-10<br>Figure 6-11<br>Figure 6-12<br>Figure 6-13<br>Figure 6-14<br>Figure 6-15<br>Figure 7-1                                                                                                                                                                             | GRU Pinout - Top View<br>CIA Pinout - Top View<br>Serial Port Connector<br>Parallel Port Connector<br>Keyboard/Mouse<br>Control Power Connector Pinout<br>OCP Connector Pinout<br>Floppy Connector Pinout<br>SROM Port Connector Pinout<br>GRU Interrupt Logic                                                                                                                                                                                                                                                                                                                                                                                                                       | 6-26<br>6-31<br>6-38<br>6-39<br>6-39<br>6-44<br>6-47<br>6-48<br>6-49<br>7-57                                                                                                                                                                                                |

| Figure 6-7<br>Figure 6-8<br>Figure 6-9<br>Figure 6-10<br>Figure 6-11<br>Figure 6-12<br>Figure 6-13<br>Figure 6-14<br>Figure 6-15<br>Figure 7-1<br>Figure 8-1                                                                                                                                                               | GRU Pinout - Top View<br>CIA Pinout - Top View<br>Serial Port Connector<br>Parallel Port Connector<br>Keyboard/Mouse<br>Control Power Connector Pinout<br>OCP Connector Pinout<br>Floppy Connector Pinout<br>SROM Port Connector Pinout<br>GRU Interrupt Logic<br>The AlphaStation 600 System Interrupt Scheme                                                                                                                                                                                                                                                                                                                                                                       | 6-26<br>6-31<br>6-38<br>6-39<br>6-39<br>6-44<br>6-47<br>6-48<br>6-49<br>7-57<br>8-2                                                                                                                                                                                         |

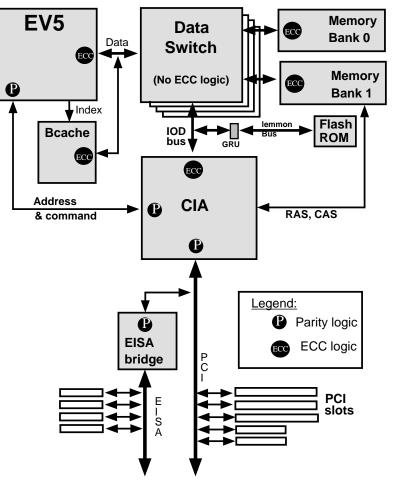

| Figure 6-7<br>Figure 6-8<br>Figure 6-9<br>Figure 6-10<br>Figure 6-12<br>Figure 6-13<br>Figure 6-13<br>Figure 6-14<br>Figure 6-15<br>Figure 7-1<br>Figure 8-1<br>Figure 8-2                                                                                                                                                 | GRU Pinout - Top View<br>CIA Pinout - Top View<br>Serial Port Connector<br>Parallel Port Connector<br>Keyboard/Mouse<br>Control Power Connector Pinout<br>OCP Connector Pinout<br>Floppy Connector Pinout<br>SROM Port Connector Pinout<br>GRU Interrupt Logic<br>The AlphaStation 600 System Interrupt Scheme<br>AlphaStation 600 Error Logic                                                                                                                                                                                                                                                                                                                                       | 6-26<br>6-31<br>6-38<br>6-39<br>6-44<br>6-47<br>6-48<br>6-49<br>7-57<br>8-2<br>8-10                                                                                                                                                                                         |

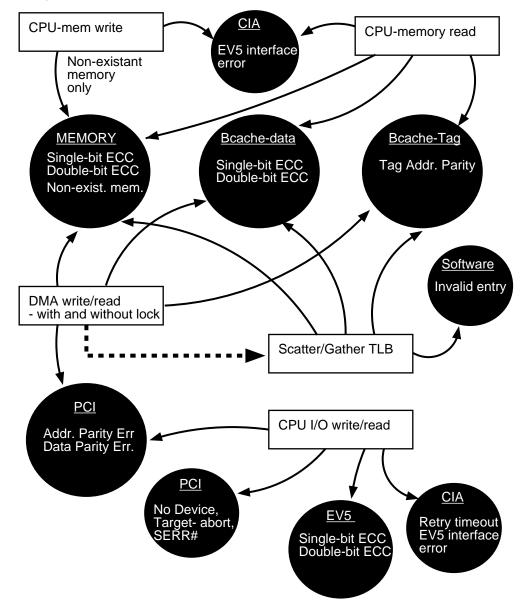

| Figure 6-7<br>Figure 6-8<br>Figure 6-9<br>Figure 6-10<br>Figure 6-11<br>Figure 6-12<br>Figure 6-13<br>Figure 6-13<br>Figure 6-14<br>Figure 6-15<br>Figure 8-1<br>Figure 8-2<br>Figure 8-3                                                                                                                                  | GRU Pinout - Top View<br>CIA Pinout - Top View<br>Serial Port Connector<br>Parallel Port Connector<br>Keyboard/Mouse<br>Control Power Connector Pinout<br>OCP Connector Pinout<br>Floppy Connector Pinout<br>SROM Port Connector Pinout<br>GRU Interrupt Logic<br>The AlphaStation 600 System Interrupt Scheme<br>AlphaStation 600 Error Logic<br>Possible Errors                                                                                                                                                                                                                                                                                                                    | 6-26<br>6-31<br>6-38<br>6-39<br>6-44<br>6-47<br>6-48<br>7-57<br>8-2<br>8-10<br>8-11                                                                                                                                                                                         |

| Figure 6-7<br>Figure 6-8<br>Figure 6-9<br>Figure 6-10<br>Figure 6-12<br>Figure 6-13<br>Figure 6-13<br>Figure 6-14<br>Figure 6-15<br>Figure 7-1<br>Figure 8-1<br>Figure 8-2<br>Figure 8-3<br>Figure 8-4                                                                                                                     | GRU Pinout - Top View<br>CIA Pinout - Top View<br>Serial Port Connector<br>Parallel Port Connector<br>Keyboard/Mouse<br>Control Power Connector Pinout<br>OCP Connector Pinout<br>Floppy Connector Pinout<br>SROM Port Connector Pinout<br>GRU Interrupt Logic<br>The AlphaStation 600 System Interrupt Scheme<br>AlphaStation 600 Error Logic<br>Possible Errors<br>Correctable Error Machine Check Logout Frame                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                             |

| Figure 6-7<br>Figure 6-8<br>Figure 6-9<br>Figure 6-10<br>Figure 6-11<br>Figure 6-12<br>Figure 6-13<br>Figure 6-13<br>Figure 6-14<br>Figure 6-15<br>Figure 7-1<br>Figure 8-1<br>Figure 8-2<br>Figure 8-3<br>Figure 8-4<br>Figure 8-5                                                                                        | GRU Pinout - Top View<br>CIA Pinout - Top View<br>Serial Port Connector<br>Parallel Port Connector<br>Keyboard/Mouse<br>Control Power Connector Pinout<br>OCP Connector Pinout<br>Floppy Connector Pinout<br>SROM Port Connector Pinout<br>GRU Interrupt Logic<br>The AlphaStation 600 System Interrupt Scheme<br>AlphaStation 600 Error Logic<br>Possible Errors<br>Correctable Error Machine Check Logout Frame<br>AlphaStation 600 Specific Error Information                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                             |