# AXPvme Single-Board Computer Technical Description

Order Number: EK-EBV1X-TD. B01

Digital Equipment Corporation Maynard, Massachusetts

July 1995 Printed in U.S.A.

Digital Equipment Corporation makes no representations that the use of its products in the manner described in this publication will not infringe on existing or future patent rights, nor do the descriptions contained in this publication imply the granting of licenses to make, use, or sell equipment or software in accordance with the description.

© Digital Equipment Corporation 1995. All Rights Reserved.

The prepaid Reader's Comments form at the end of this document requests your critical evaluation to assist in preparing future documentation.

The following are trademarks of Digital Equipment Corporation: Alpha AXP, DECnet, Digital, DECchip, OpenVMS, ULTRIX, VAX, VAX DOCUMENT, VxWorks, and the DIGITAL logo.

The following are third-party trademarks:

DALLAS is a registered trademark of Dallas Systems Corporation. Futurebus/Plus is a registered trademark of Force Computers GMBH, Germany. Intel is a trademark of Intel Corporation. NCR is a registered trademark of National Cash Register Company. OSF and OSF/1 are registered trademarks of Open Software Foundation, Inc. UNIX is a registered trademark licensed exclusively by X/Open Company Ltd. VIC64 is a trademark of Cypress Semiconductor Corporation.

VxWORKS is a registered trademark of Wind River Systems, Inc..

All other trademarks and registered trademarks are the property of their respective holders.

S2923

This document was prepared using VAX DOCUMENT Version 2.1.

# Contents

| P | reface                                                                  | xiii |

|---|-------------------------------------------------------------------------|------|

| 1 | Technical Hardware Specifications                                       |      |

|   | 1.1 Overview                                                            | 1–1  |

|   | 1.1.1 Related Hardware Specification Documents                          | 1–2  |

|   | 1.1.2 Conventions and Terms                                             | 1–2  |

|   | 1.1.3 System Description                                                | 1–2  |

|   | 1.1.3.1 LCA Processor                                                   | 1–2  |

|   | 1.1.3.2 Memory Controller                                               | 1–2  |

|   | 1.1.3.3 I/O Controller                                                  | 1–3  |

|   | 1.1.3.4 VME Interface                                                   | 1–3  |

|   | 1.1.3.5 Network Interface (IEEE 802.3)                                  | 1–4  |

|   | 1.1.3.6 SCSI                                                            | 1–4  |

|   | 1.1.3.7 ROM                                                             | 1–4  |

|   | 1.1.3.8 Console UART                                                    | 1–4  |

|   | 1.1.3.9 Watchdog                                                        | 1–4  |

|   | 1.1.3.10 Interval Timers                                                | 1–4  |

|   | 1.1.3.11 TOY Clock                                                      | 1–4  |

|   | 1.1.3.12 Nonvolatile RAM                                                | 1–4  |

|   | 1.1.3.13 Display                                                        | 1–5  |

|   | 1.1.3.14 PCI Mezzanine                                                  | 1–5  |

|   | 1.1.3.15DIP Switches                                                    | 1–5  |

|   | 1.2 LCA Processor                                                       | 1–6  |

|   | 1.3 Memory Subsystem                                                    | 1–7  |

|   | 1.3.1 Main Memory                                                       | 1–8  |

|   | 1.3.2   Backup Cache                                                    | 1–8  |

|   | 1.3.3 Memory Initialization                                             | 1–9  |

|   | 1.3.4 Error Handling                                                    | 1–9  |

|   | 1.4 I/O Subsystem                                                       | 1–10 |

|   | 1.4.1 PCI Addressing and Configuration                                  | 1–10 |

|   | 1.4.2 PCI Arbitration                                                   | 1–12 |

|   | 1.4.3 PCI Transfer                                                      | 1–14 |

|   | 1.4.3.1 Masked Transfers                                                | 1–15 |

|   | 1.4.3.2 Unmasked Transfers                                              | 1–16 |

|   | 1.4.4 Main Memory as PCI Target                                         | 1–16 |

|   | 1.4.5 PCI Address Space Layout                                          | 1–17 |

|   | 1.4.5.1         PCI Memory Space           1.4.5.2         PCI MC Space | 1-17 |

|   | 1.4.5.2 PCI I/O Space                                                   | 1-19 |

|   | 1.5 VME Interface                                                       | 1–20 |

| 1.5.1   | PCI Access to VME Interface                               | 1–20 |

|---------|-----------------------------------------------------------|------|

| 1.5.1.1 | VME_CSR_BASE Register                                     | 1–20 |

| 1.5.1.2 | VME_WINDOW_1_BASE Register                                | 1–21 |

| 1.5.1.3 | VME_SG_BASE Register                                      | 1–21 |

| 1.5.1.4 | VME_WINDOW_2_BASE Register                                | 1–22 |

| 1.5.1.5 | VME_WINDOW_2_SIZE Register                                | 1–22 |

| 1.5.2   | Master Operation                                          | 1–23 |

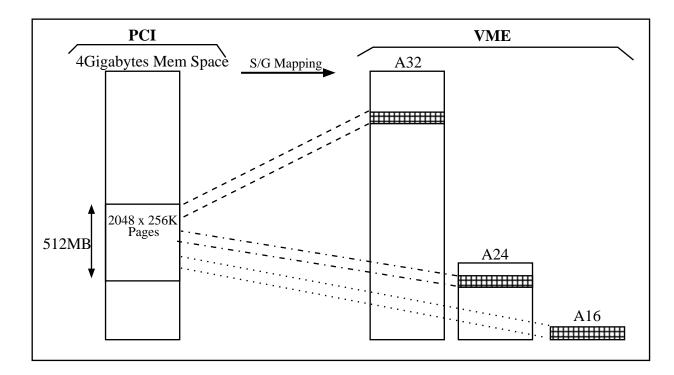

| 1.5.2.1 | Outbound S/G Mapping                                      | 1-24 |

| 1.5.2.2 |                                                           | 1–26 |

| 1.5.2.3 | Master Block Mode                                         | 1-26 |

| 1.5.3   | VMEbus Requester                                          | 1-28 |

| 1.5.3.1 | VMEbus Request                                            | 1-28 |

| 1.5.3.2 | VMEbus Release                                            | 1-20 |

| 1.5.4   | Slave Operation                                           | 1-20 |

| 1.5.4.1 | A32, A24 VMEbus Address Decode                            | 1-29 |

| 1.5.4.1 |                                                           | 1–30 |

|         | Inbound S/G Mapping                                       |      |

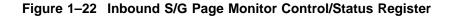

| 1.5.4.3 | Inbound S/G Page Monitor                                  | 1–31 |

| 1.5.5   | Programming S/G RAM                                       | 1–32 |

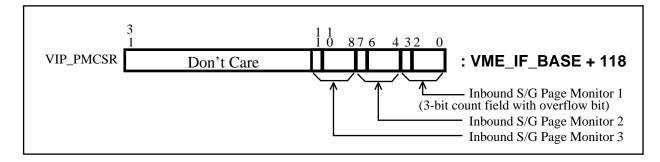

| 1.5.6   | Byte Swapping                                             | 1–33 |

| 1.5.7   | System Controller Operation                               | 1–37 |

| 1.5.7.1 | VMEbus Arbitration                                        | 1–37 |

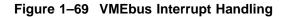

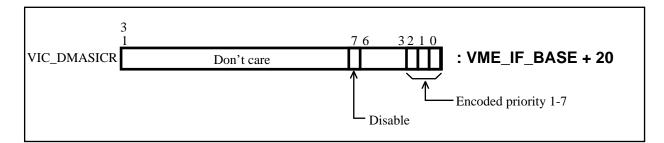

| 1.5.7.2 | VMEbus Interrupt Handling                                 | 1–37 |

| 1.5.7.3 | SYSCLK Output                                             | 1–37 |

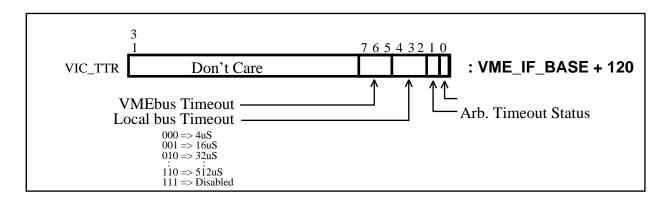

| 1.5.7.4 | Timeout Timers for Arbitration and Transfers              | 1–38 |

| 1.5.8   | Interprocessor Communication                              | 1–38 |

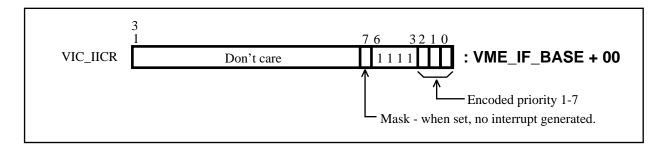

| 1.5.8.1 | Interprocessor Communication Registers (ICRs)             | 1–38 |

| 1.5.8.2 | Interprocessor Communication Global Switches (ICGS)       | 1–39 |

| 1.5.8.3 | Interprocessor Communication Module Switches (ICMS)       | 1–39 |

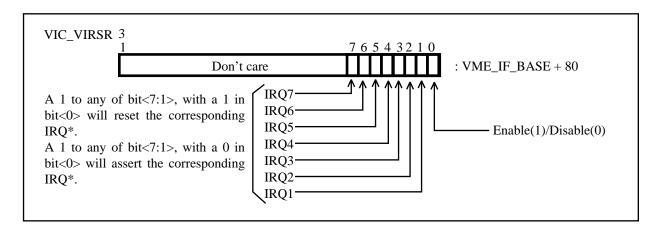

| 1.5.9   | AXPvme Generated VMEbus Interrupts                        | 1–40 |

| 1.6     | VME Interface                                             | 1–42 |

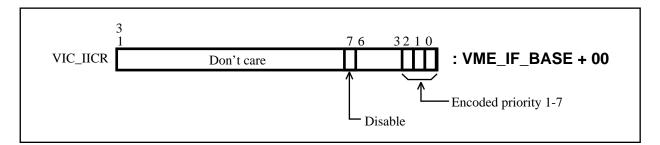

| 1.6.1   | How AXPvme Uses the VIC64 Registers                       | 1–42 |

| 1.6.2   | VME Register Summary                                      | 1–46 |

| 1.6.3   | VME Subsystem Restrictions (as of 22-Nov-94)              | 1–48 |

| 1.6.3.1 | D64 Writes to Invalid Pages.                              | 1–48 |

| 1.6.3.2 | D64 Write/IACK Cycle Collisions                           | 1-48 |

| 1.6.3.3 | Collision of VIC64 Master Write Posting with Master Block | 1 40 |

| 1.0.0.0 | Transfers                                                 | 1–48 |

| 1.6.3.4 | VIC64 Errata: A16 Master Cycles During Interleave         | 1-48 |

| 1.6.3.5 | Module Reset Temporarily Disables IACK Chain              | 1-40 |

|         |                                                           |      |

| 1.7     | Network Interface                                         | 1-50 |

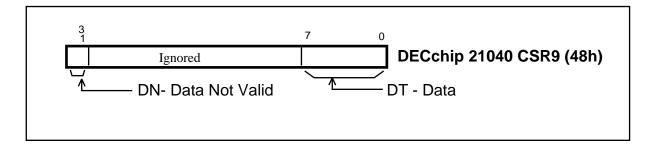

| 1.7.1   | DECchip 21040-AA PCI Configuration Registers              | 1-50 |

| 1.7.2   | DECchip 21040-AA CSRs                                     | 1–50 |

| 1.7.3   | DECchip 21040-AA PCI Cycles                               | 1–51 |

| 1.7.4   | Ethernet Address ROM                                      | 1–51 |

| 1.8     | SCSI                                                      | 1–52 |

| 1.8.1   | SCSI ID                                                   | 1–52 |

| 1.8.2   | SCSI Connection and Termination                           | 1–52 |

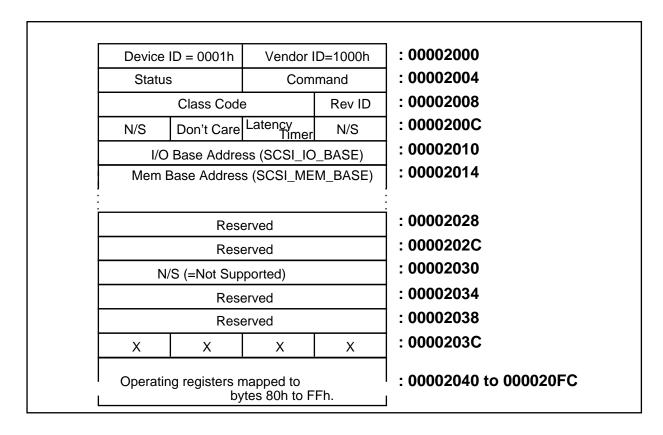

| 1.8.3   | 53C810 Configuration Block                                | 1–52 |

| 1.8.4   | SCSI Programming                                          | 1–53 |

| 1.8.5   | SCSI Control Status Registers                             | 1–53 |

| 1.8.6   | Clocking Information                                      | 1–55 |

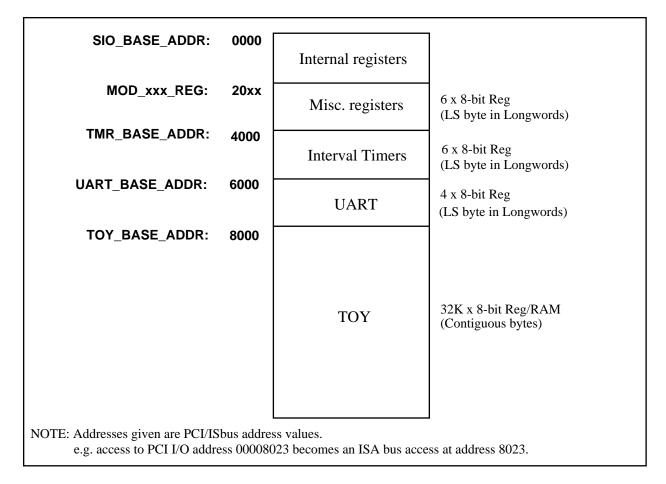

| 1.9     | ISbus                                                     | 1–56 |

| 1.9.1   | ISbus Adapter (SIO) Configuration Space                   | 1–56 |

| 1.9.1.1 | AXPvme Required Setup                                     | 1–56 |

|         | ·····                                                     |      |

| 1.9.2    | ISbus Address Space                  | 1–57 |

|----------|--------------------------------------|------|

| 1.9.3    | ISbus Operation                      | 1–59 |

| 1.10 Mo  | odule Registers                      | 1–59 |

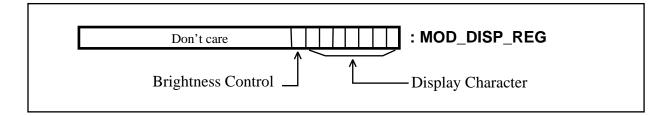

| 1.10.1   | Module Display Control Register      | 1–59 |

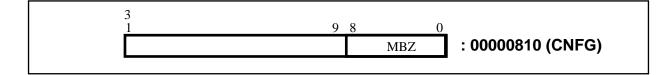

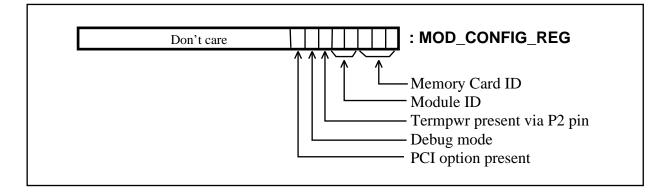

| 1.10.2   | Module Configuration Register        | 1–60 |

| 1.10.2.1 | Memory Card ID <2:0>                 | 1–61 |

| 1.10.2.2 | Module ID <4:3>                      | 1–61 |

| 1.10.2.3 | Present Bits <7:5>                   | 1–61 |

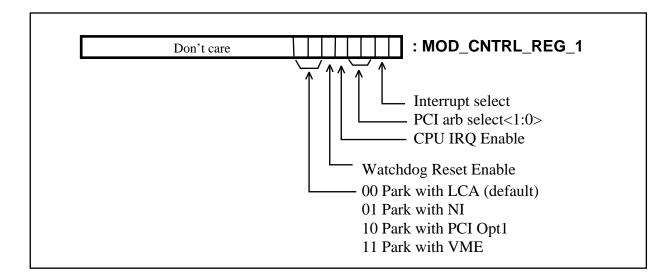

| 1.10.3   | Module Control Register 1            | 1–61 |

| 1.10.3.1 | Park Device Select Bits <7:6>        | 1–62 |

| 1.10.3.2 | Watchdog Reset Enable Bit <5>        | 1–62 |

| 1.10.3.3 | CPU IRQ Enable Bit <4>               | 1–62 |

| 1.10.3.4 | PCI Arbitration Selection Bits <3:2> | 1–62 |

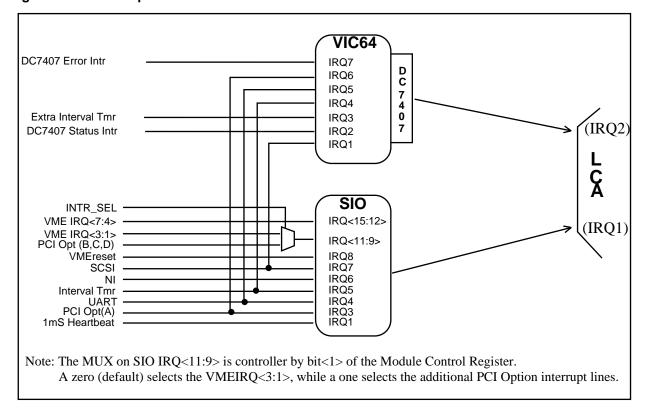

| 1.10.3.5 | Interrupt Select Bit <1>             | 1–62 |

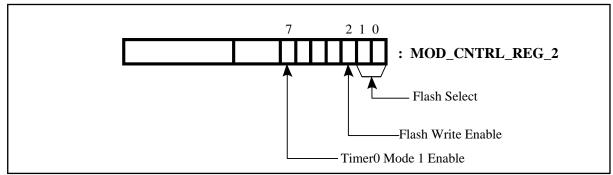

| 1.10.4   | Module Control Register 2            | 1–63 |

| 1.10.4.1 | Flash Select <1:0>                   | 1–63 |

| 1.10.4.2 | Flash Write Enable <2>               | 1–63 |

| 1.10.4.3 | Timer 0 Mode 1 Enable                | 1-63 |

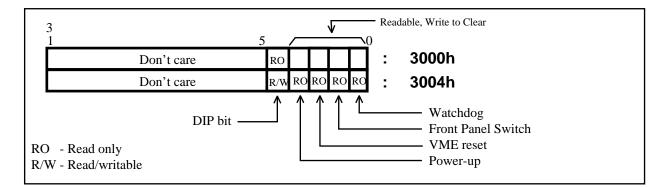

| 1.10.5   | Reset Reason Register                | 1-64 |

| 1.10.6   | Heartbeat "Clear-Interrupt" Register | 1-64 |

| 1.10.7   | Front Panel Status LEDs              | 1-65 |

| 1.10.7.1 | The AMBER LED                        | 1-65 |

| 1.10.7.2 | The GREEN LED                        | 1-65 |

|          | DM                                   | 1-65 |

| 1.11.1   | Serial ROM                           | 1-65 |

| 1.11.2   | System ROM                           | 1-05 |

| 1.11.3   | Flash ROM Updating                   | 1-66 |

| 1.11.4   | Write Protect                        | 1-66 |

|          | nsole UART                           | 1-67 |

| 1.12 00  | UART Operation                       | 1-67 |

| 1.12.1   | Data/Register Access                 | 1-67 |

| 1.12.2.1 | Serial Line Data                     | 1-68 |

| 1.12.2.1 |                                      | 1-68 |

| 1.12.2.2 | Internal Registers                   | 1-00 |

| -        | SCC Operation in Asynchronous Mode   | 1-70 |

| 1.12.3.1 | RX Operation                         |      |

| 1.12.3.2 | TX Operation                         | 1-70 |

| 1.12.3.3 | Baud Rate Control                    | 1-71 |

| 1.12.3.4 | Interrupt Generation                 | 1-72 |

| 1.12.3.5 | Read Registers                       | 1-73 |

| 1.12.4   | System Use and Firmware              | 1-74 |

| 1.12.5   | Physical Details                     | 1-74 |

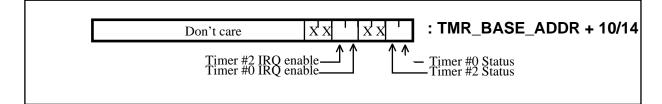

|          | OY Clock                             | 1–74 |

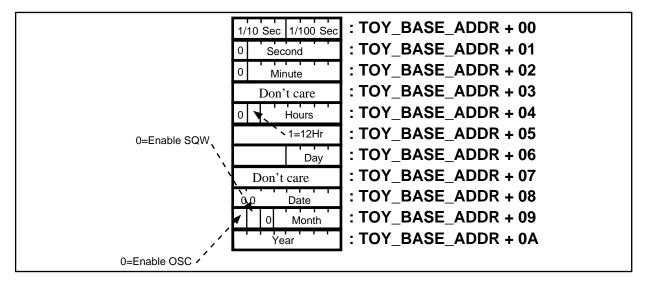

| 1.13.1   | TOY Clock Operation                  | 1-75 |

| 1.13.2   | Fixed Frequency "Heartbeat" Output   | 1-76 |

| 1.13.3   | Standby Power                        | 1–76 |

|          | terval Timers                        | 1-77 |

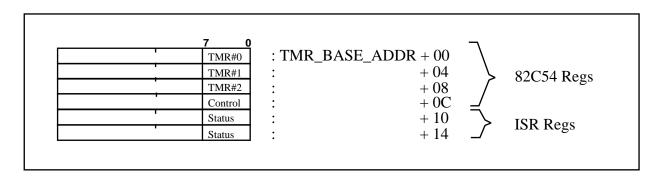

| 1.14.1   | 82C54 Operation                      | 1–78 |

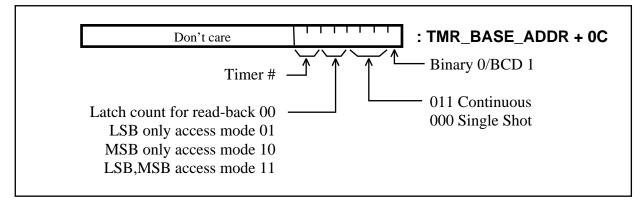

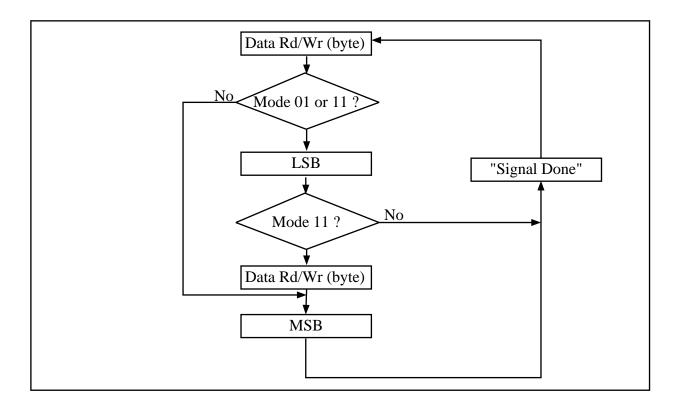

| 1.14.1.1 | Control Byte                         | 1–78 |

| 1.14.1.2 | Timer Modes                          | 1–79 |

| 1.14.1.3 | Status Read                          | 1–81 |

| 1.14.2 Interval Timers in AXPvme 14.2                              | -81  |

|--------------------------------------------------------------------|------|

| 1.14.2.1 Timer Clocking 1-                                         | -82  |

| 1.14.2.2 Timer Outputs 14                                          | -82  |

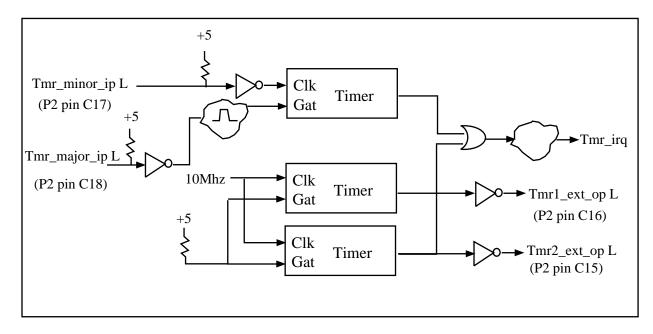

| 1.14.2.3 Timer Interrupt/Expiration Control and Status Register 1  | -83  |

| 1.14.2.4 Timer #0 Restrictions (AXPvme 64, AXPvme 64LC, and AXPvme |      |

| 160 modules only) 14                                               | -83  |

|                                                                    | -84  |

| 0                                                                  | -84  |

| 0 1                                                                | -84  |

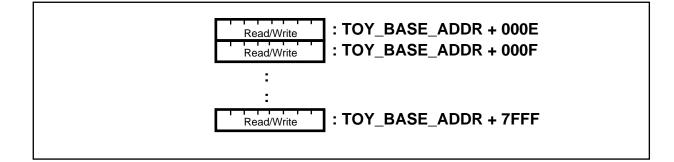

| 1.16         Nonvolatile RAM         1                             | -85  |

|                                                                    | -86  |

| I                                                                  | -86  |

| 1                                                                  | -87  |

| JI                                                                 | -88  |

|                                                                    | -88  |

| 1                                                                  | -89  |

|                                                                    | -89  |

| $\mathbf{v}$                                                       | -91  |

| 1                                                                  | -92  |

| 0 1                                                                | -94  |

|                                                                    | -94  |

|                                                                    | -95  |

|                                                                    | -95  |

| 1.17.5     Nonmaskable System Events     1                         | -95  |

|                                                                    | -96  |

|                                                                    | -96  |

| 1.18         Error Handling         1                              | -96  |

|                                                                    | -97  |

|                                                                    | -97  |

|                                                                    | -97  |

|                                                                    | -97  |

|                                                                    | -98  |

| 1 0                                                                | -98  |

| 0                                                                  | -98  |

| J I I I I I I I I I I I I I I I I I I I                            | -99  |

|                                                                    | 100  |

|                                                                    | 100  |

| 0                                                                  | 102  |

|                                                                    | 104  |

|                                                                    | 105  |

|                                                                    | 107  |

| 0                                                                  | 108  |

| 1.22    Power and Environmental Requirements    1–                 | -110 |

## 2 Console Primer

| 2.1   | Introduction                                           | 2–1 |

|-------|--------------------------------------------------------|-----|

| 2.1.1 | Console Features                                       | 2–1 |

| 2.1.2 | Command Overview                                       | 2–2 |

| 2.1.3 | Console Shell Operators                                | 2–2 |

| 2.2   | Getting Information About the System                   | 2–4 |

| 2.3   | Online Help                                            | 2–4 |

| 2.4   | Examining and Depositing to Memory or System Registers | 2–6 |

| 2.4.1 | Accessing Memory                                       | 2–7 |

| 2.4.2 | Examining Registers                         | 2–8  |

|-------|---------------------------------------------|------|

| 2.5   | Using Pipes (   ) and grep to Filter Output | 2–9  |

| 2.6   | Using I/O Redirection (>)                   | 2–9  |

| 2.7   | Running Commands in the Background "&"      | 2–10 |

| 2.8   | Monitoring Status                           | 2–10 |

| 2.9   | Killing a Process                           | 2–10 |

| 2.10  | Creating Scripts                            | 2–12 |

| 2.11  | Using Flow Control                          | 2–13 |

| 2.12  | Copying Scripts over the Network            | 2–15 |

## 3 Console Commands

| 3.1            | Console Commands                            | 3–2        |

|----------------|---------------------------------------------|------------|

| 3.1.1          | Special Keys                                | 3–2        |

| 3.1.2<br>3.1.3 | Command Line Characteristics                | 3–2<br>3–2 |

| 3.1.3<br>3.1.4 | Radix Control    Console Command Dictionary | 3-2<br>3-2 |

| 5.1.4          | #                                           | 3–2        |

|                | #alloc                                      | 3–3<br>3–4 |

|                | boot                                        | 3–4<br>3–5 |

|                | break                                       | 3–5        |

|                |                                             | 3–11       |

|                | cat                                         | -          |

|                | chmod                                       | 3–13       |

|                | chown                                       | 3–15       |

|                | clear                                       | 3–16       |

|                | clear_log                                   | 3–17       |

|                | continue                                    | 3–18       |

|                | crc                                         | 3–19       |

|                | date                                        | 3–21       |

|                | deposit                                     | 3–23       |

|                | dynamic                                     | 3–27       |

|                | echo                                        | 3–29       |

|                | edit                                        | 3–31       |

|                | eval                                        | 3–34       |

|                | examine                                     | 3–36       |

|                | exer                                        | 3–40       |

|                | exit                                        | 3–46       |

|                | false                                       | 3–47       |

|                | free                                        | 3–48       |

|                | grep                                        | 3–49       |

|                | hd                                          | 3–51       |

|                | help, man                                   | 3–52       |

|                | initialize                                  | 3–54       |

|                | init ev                                     | 3–55       |

|                | kill                                        | 3–56       |

|                | line                                        | 3–57       |

|                | ls                                          | 3–58       |

|                | memexer                                     | 3–59       |

|                | memtest                                     | 3–60       |

| net             | 3–65 |

|-----------------|------|

| nettest         | 3–68 |

| ps              | 3–71 |

| pwrup           | 3–72 |

| rm              | 3–73 |

| sa              | 3–74 |

| semaphore       | 3–75 |

| set             | 3–76 |

| set led         | 3–78 |

| set mode        | 3–79 |

| set reboot srom | 3–80 |

| set toy sleep   | 3–81 |

| sh              | 3–82 |

| show            | 3–83 |

| show config     | 3–85 |

| show device     | 3–86 |

| show hwrpb      | 3–88 |

| show led        | 3–89 |

| show map        | 3–90 |

| show mode       | 3–91 |

| show_log        | 3–92 |

| sleep           | 3–94 |

| sort            | 3–95 |

| sp              | 3–96 |

| start           | 3–97 |

| stop            | 3–98 |

| update          | 3–99 |

# 4 Environment Variables

| 4.1   | Overview                                      | 4–1 |

|-------|-----------------------------------------------|-----|

| 4.2   | Application-Independent Environment Variables | 4–2 |

| 4.3   | Diagnostic Environment Variables              | 4–4 |

| 4.4   | Console-Specific Environment Variables        | 4–5 |

| 4.4.1 | Ethernet Environment Variables                | 4–5 |

| 4.4.2 | Storage Environment Variables                 | 4–6 |

| 4.4.3 | Console Configuration Environment Variables   | 4–7 |

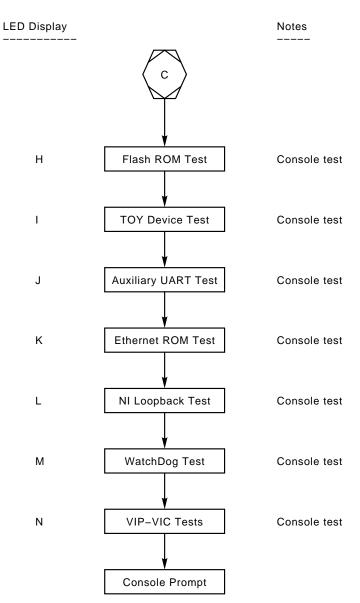

# 5 Diagnostics

| 5.1   | Power-up Self-Test                     | 5–1 |

|-------|----------------------------------------|-----|

| 5.2   | Miscellaneous Diagnostic Hooks         | 5–1 |

| 5.3   | Diagnostic Test Descriptions           | 5–1 |

| 5.3.1 | Available Console and SROM Diagnostics | 5–1 |

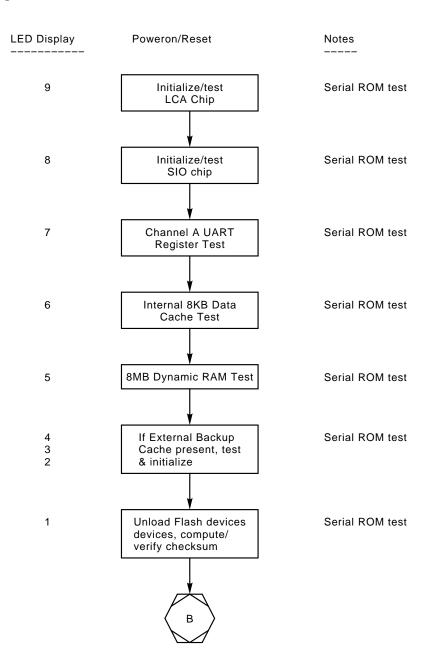

| 5.3.2 | SROM Diagnostic Test Descriptions      | 5–4 |

|       | SROM System I/O Device Test            | 5–5 |

|       | SROM Console UART Test                 | 5–6 |

|       | SROM Internal Data Cache Test          | 5–7 |

|       | SROM Dynamic RAM Test                  | 5–8 |

|       | SROM External Backup Cache Test                  | 5–9  |

|-------|--------------------------------------------------|------|

|       | SROM Flash EPROM Unload Test                     | 5–10 |

| 5.3.3 | Console Power On Self Test Descriptions          | 5–11 |

|       | POST NVRAM Diagnostic                            | 5–12 |

|       | POST Memory Diagnostic                           | 5–13 |

| 5.3.4 | Console Diagnostic Test Descriptions             | 5–15 |

|       | Flash EPROM Tests                                | 5–16 |

|       | Module Display Control Register/LED Tests        | 5–18 |

|       | Module Control Register Test                     | 5–19 |

|       | Heartbeat Timer Test                             | 5–20 |

|       | Interval Timer Tests                             | 5–21 |

|       | DECchip 21040 Ethernet Controller Tests          | 5–26 |

|       | Memory ECC Detection Test                        | 5–28 |

|       | Backup Cache Tests                               | 5–29 |

|       | 8530 Serial Communication Controller Tests       | 5–31 |

|       | DALLAS DS1386 RAMified Watchdog Timekeeper Tests | 5–33 |

|       | LAN Address ROM Test                             | 5–36 |

|       | NCR 53C810 PCI-SCSI IO Processor Tests           | 5–38 |

|       | Watchdog Timer Interrupt Test                    | 5–40 |

|       | VME Interface Tests                              | 5–41 |

| 5.4   | Test Sequence                                    | 5–43 |

# A Specifications

## **B** AXPvme Connectors

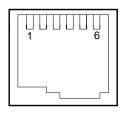

| B.1 | Serial Line Connectors | B–1 |

|-----|------------------------|-----|

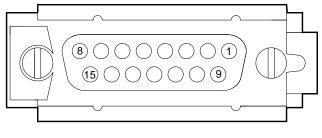

| B.2 | Ethernet AUI Connector | B–2 |

| B.3 | SCSI Connector         | B–2 |

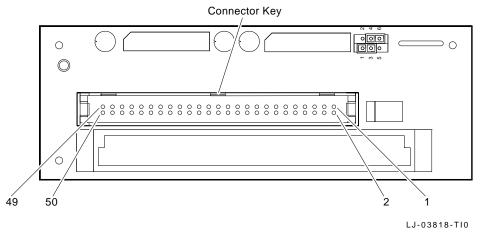

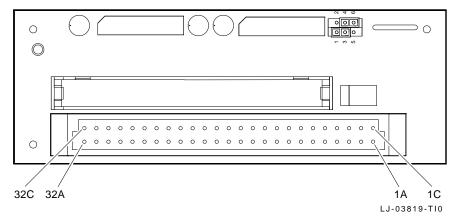

| B.4 | VMEbus P2 Connector    | B–4 |

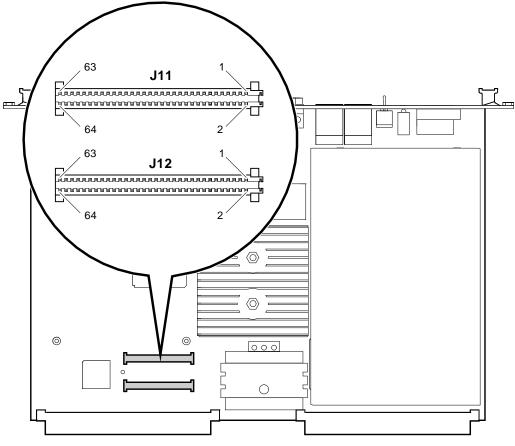

| B.5 | PCI Option Connectors  | B–6 |

## Index

# Figures

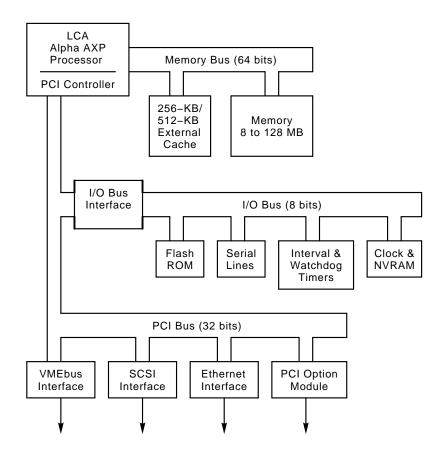

| 1–1  | AXPvme Module Block Diagram           | 1–1  |

|------|---------------------------------------|------|

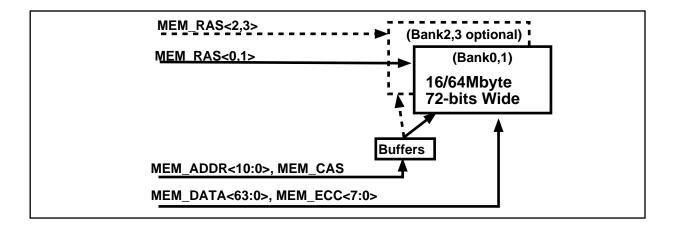

| 1–2  | Memory System                         | 1–8  |

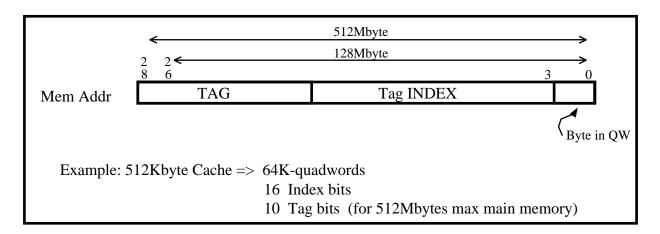

| 1–3  | Cache Tag                             | 1–9  |

| 1–4  | Generic Configuration Space Header    | 1–11 |

| 1–5  | PCI Devices, Size, and Base Registers | 1–12 |

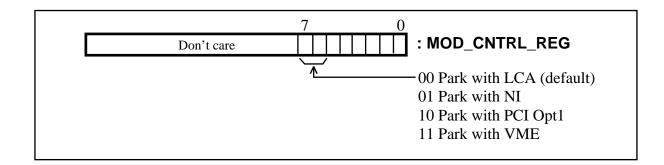

| 1–6  | Module Control Register (PCI Park)    | 1–14 |

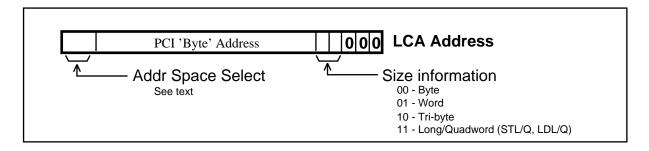

| 1–7  | LCA I/O Addressing                    | 1–14 |

| 1–8  | PCI Memory Space Address Map          | 1–19 |

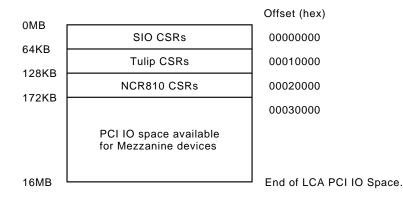

| 1–9  | PCI I/O Space Address Map             | 1–20 |

| 1–10 | VME_CSR_BASE Register                 | 1–21 |

| 1–11 | VME_WINDOW_1_BASE Register            | 1–21 |

| 1–12 | VME_SG_BASE Register                  | 1–21 |

| 1–13 | VME_WINDOW_2_BASE Register                              | 1–22 |

|------|---------------------------------------------------------|------|

| 1–14 | VME_WINDOW_2_SIZE Register                              | 1–22 |

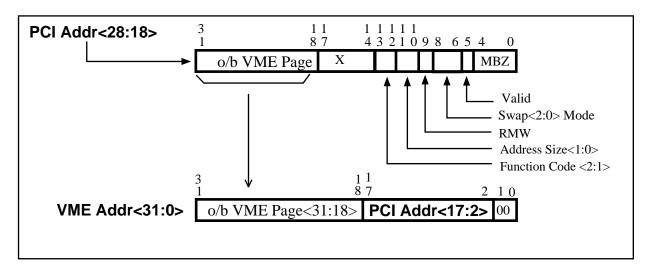

| 1–15 | Example PCI to VME Mapping                              | 1–24 |

| 1–16 | Outbound S/G Entry                                      | 1–25 |

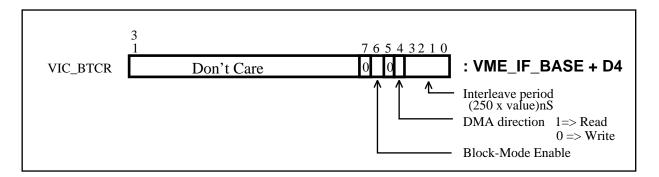

| 1–17 | VIC Block Transfer Control Register (VIC_BTCR)          | 1–27 |

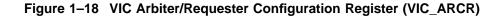

| 1–18 | VIC Arbiter/Requester Configuration Register (VIC_ARCR) | 1–28 |

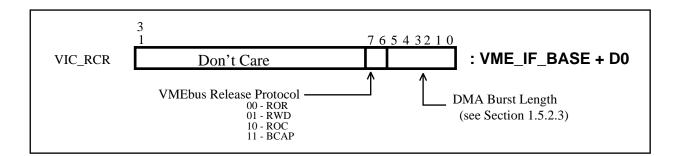

| 1–19 | VIC Release Control Register (VIC_RCR)                  | 1–29 |

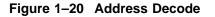

| 1–20 | Address Decode                                          | 1–30 |

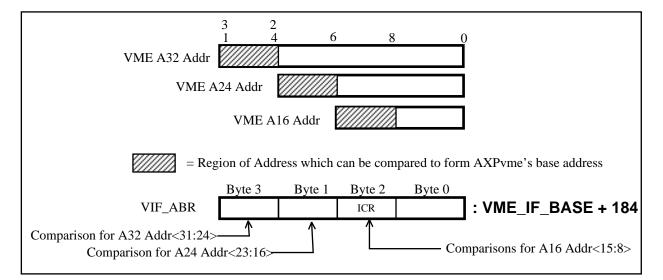

| 1–21 | Inbound S/G Entry (With A32 Addressing Example)         | 1–31 |

| 1–22 | Inbound S/G Page Monitor Control/Status Register        | 1–32 |

| 1–23 | DC7407 Swap Modes                                       | 1–34 |

| 1–24 | Big Endian VME Byte Lane Formats                        | 1–35 |

| 1–25 | VMEbus Transfer Timeout Register (VIC_TTR)              | 1–38 |

| 1–26 | Interprocessor Communication Register Map               | 1–40 |

| 1–27 | VMEbus Interrupt Request/Status Register                | 1–41 |

| 1–28 | VMEbus Interrupt Vector Base Registers                  | 1–41 |

| 1–29 | VMEbus Interrupter Interrupt Control Register           | 1–42 |

| 1–30 | DECchip 21040-AA PCI Configuration Registers            | 1–50 |

| 1–31 | DECchip 21040-AA CSR9 (ENET ROM Register)               | 1–52 |

| 1–32 | 53C810 Configuration Block                              | 1–53 |

| 1–33 | SIO Configuration Block                                 | 1–56 |

| 1–34 | ISbus I/O Address Layout                                | 1–58 |

| 1–35 | Display Character Set                                   | 1–60 |

| 1–36 | Module Display Control Register                         | 1–60 |

| 1–37 | Module Configuration Register                           | 1–61 |

| 1–38 | Module Control Register 1                               | 1–62 |

| 1–39 | Module Control Register 2                               | 1–63 |

| 1–40 | Reset Reason Register                                   | 1–64 |

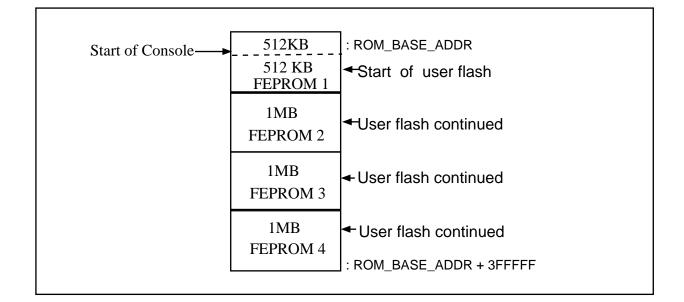

| 1–41 | Flash ROM Layout/Addressing                             | 1–66 |

| 1–42 | Typical Asynchronous Protocol                           | 1–67 |

| 1–43 | SCC Memory Map                                          | 1–68 |

| 1–44 | Write Register 0 (Channel A)                            | 1–69 |

| 1–45 | Read Register 0 (Channel A)                             | 1–69 |

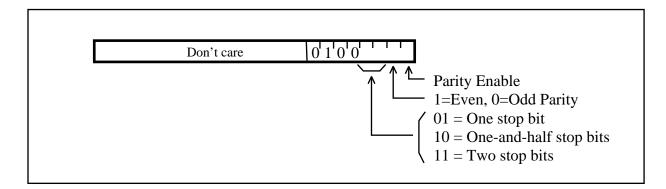

| 1–46 | Write Register 4                                        | 1–70 |

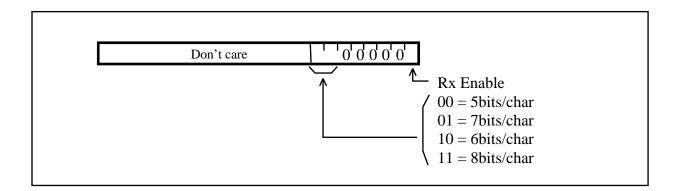

| 1–47 | Write Register 3                                        | 1–70 |

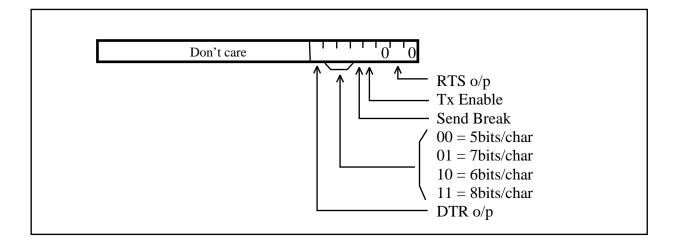

| 1–48 | Write Register 5                                        | 1–71 |

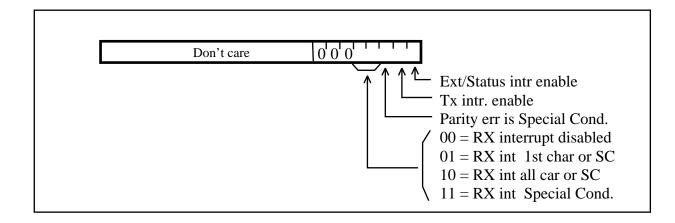

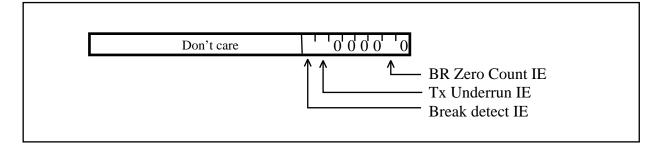

| 1–49 | Interrupt Control Register (Write Register 1)           | 1–72 |

| 1–50 | External/Status Interrupt Control (Write Register 15)   | 1–73 |

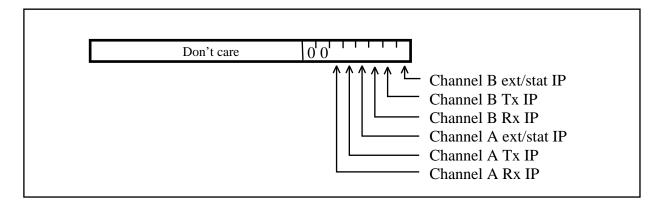

| 1–51 | Read Register 3 (Interrupt Pending Register)            | 1–73 |

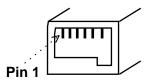

| 1–52 | DEC423 MMJ Connector                                    | 1–74 |

| 1–53 | TOY Time Registers                                      | 1–75 |

| 1–54 | TOY Command Register                                    | 1–76 |

| 1-55 | Timer Memory Map                                        | 1-77 |

| 1–56 | 82C54 Control Byte                                      | 1–78 |

| 1–57 | 82C54 Timer Data Access                                 | 1–79 |

| 1-58 | Timer Clocking                                          | 1-82 |

| 1–59 | Timer Interrupt/Expiration Status Register              | 1–83 |

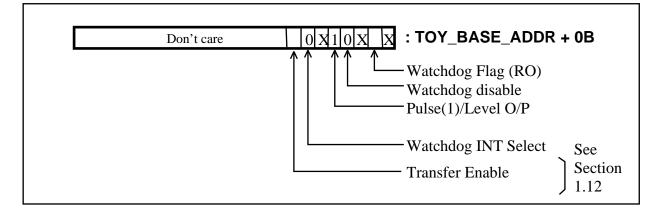

| 1–60 | Watchdog Time Registers                               | 1–84  |

|------|-------------------------------------------------------|-------|

| 1–61 | TOY Command Register (Watchdog)                       | 1–85  |

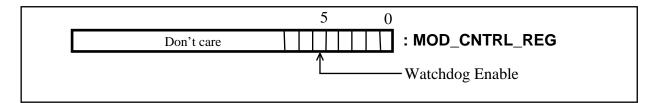

| 1–62 | Module Control Register (Watchdog)                    | 1–85  |

| 1–63 | NVRAM Access                                          | 1–86  |

| 1–64 | Interrupt Overview                                    | 1–87  |

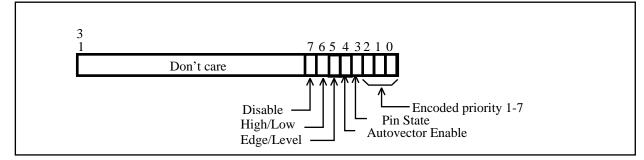

| 1–65 | Generic Interrupt Control Register                    | 1–88  |

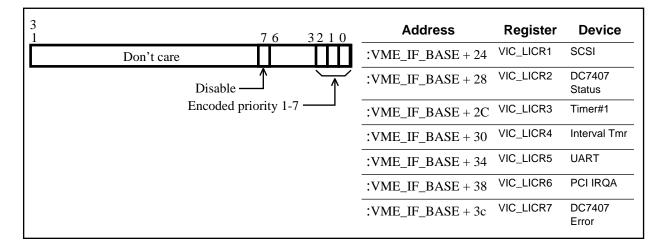

| 1–66 | Device Interrupt Control Registers                    | 1–90  |

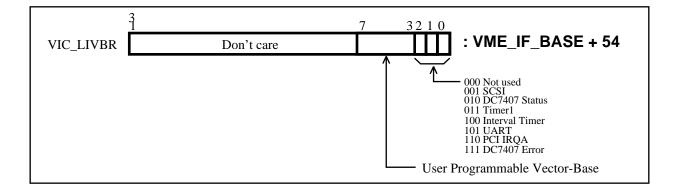

| 1–67 | VIC Local Interrupt Vector Base Register              | 1–91  |

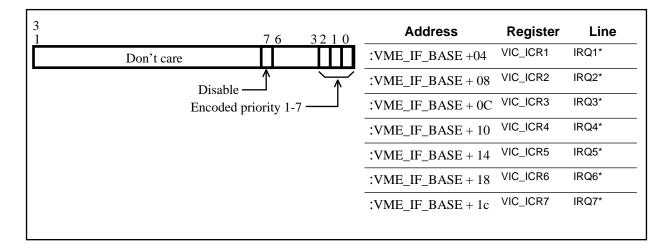

| 1–68 | VME IRQ* Interrupt Control Registers                  | 1–91  |

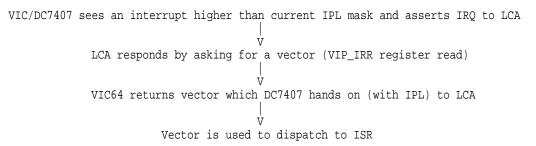

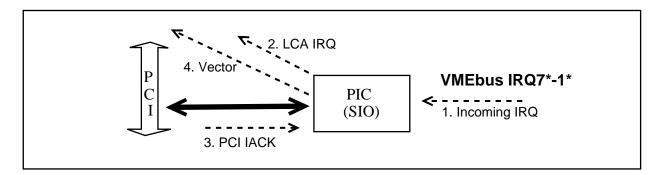

| 1–69 | VMEbus Interrupt Handling                             | 1–92  |

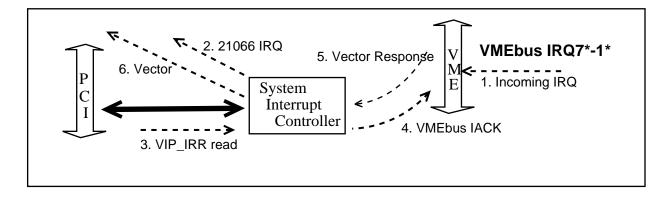

| 1–70 | DMA Status Interrupt Control Register                 | 1–92  |

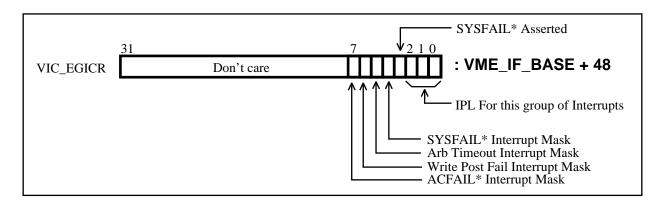

| 1–71 | VIC Error Group Interrupt Control Register            | 1–93  |

| 1–72 | VMEbus Interrupter Interrupt Control Register         | 1–93  |

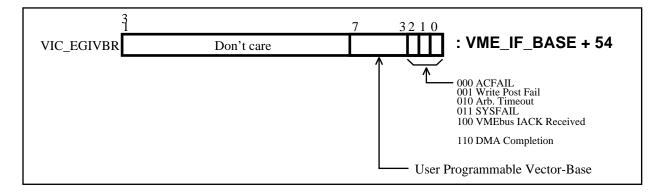

| 1–73 | VIC Error Group Interrupt Vector Base Register        | 1–94  |

| 1–74 | VMEbus Auto-Vector Interrupt Handling                 | 1–95  |

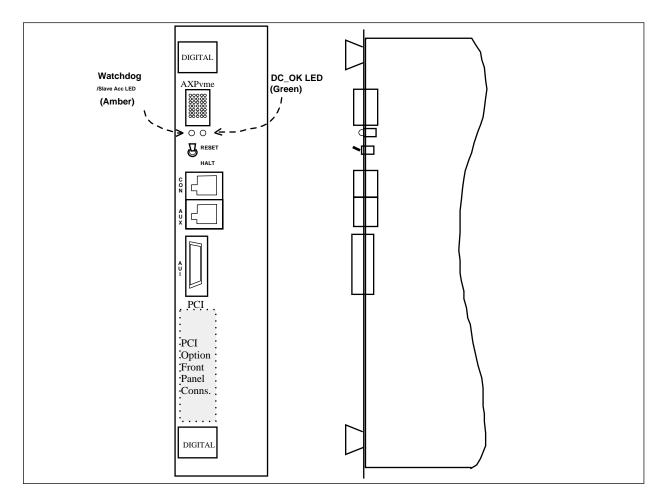

| 1–75 | Module and Front Panel                                | 1–99  |

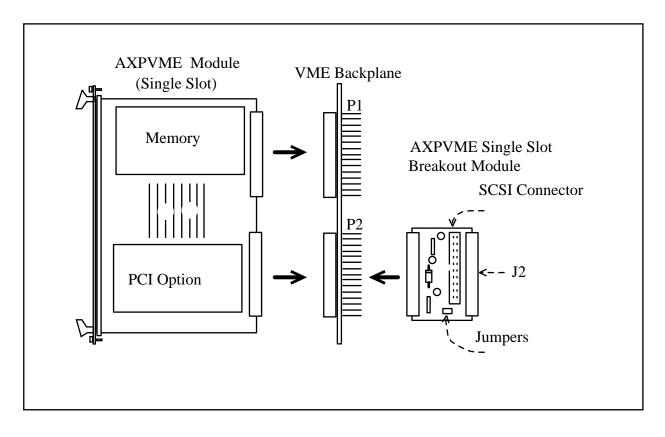

| 1–76 | AXPvme Single-Slot Breakout Module Installation       | 1–102 |

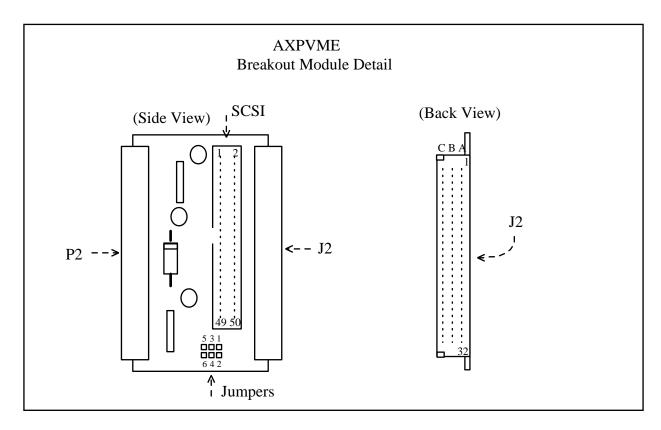

| 1–77 | AXPvme Single-Slot Breakout Module Detail             | 1–103 |

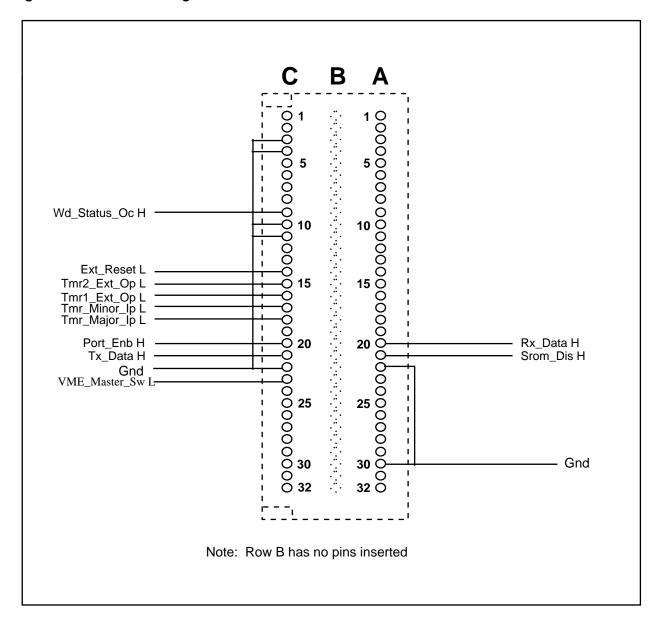

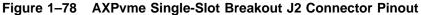

| 1–78 | AXPvme Single-Slot Breakout J2 Connector Pinout       | 1–104 |

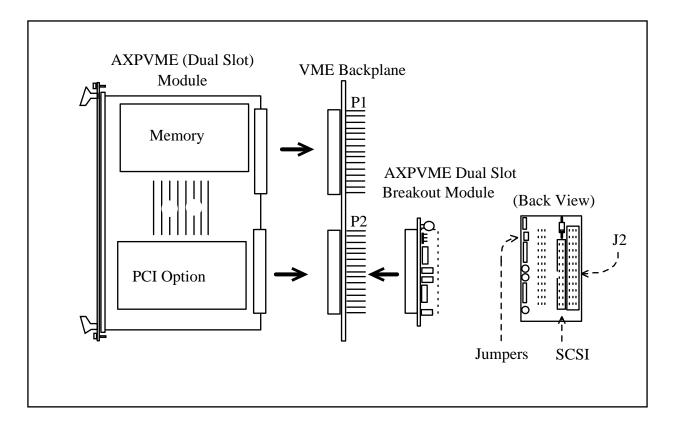

| 1–79 | AXPvme Dual-Slot Breakout Module Installation         | 1–105 |

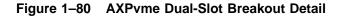

| 1–80 | AXPvme Dual-Slot Breakout Detail                      | 1–106 |

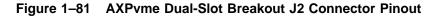

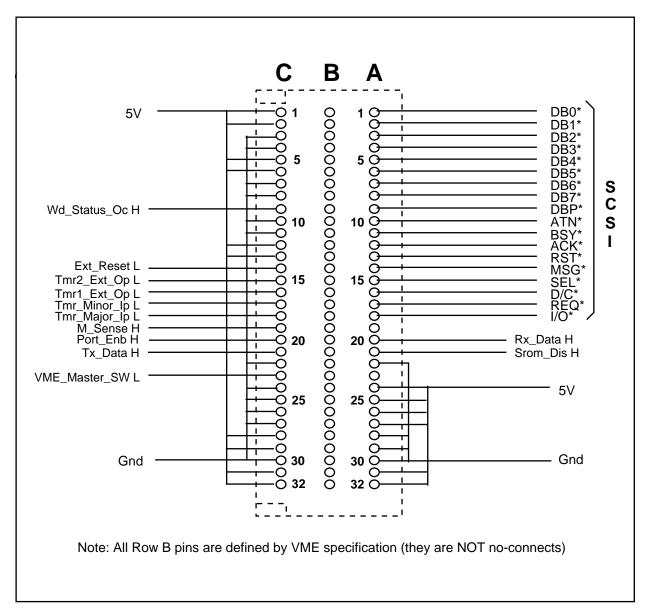

| 1–81 | AXPvme Dual-Slot Breakout J2 Connector Pinout         | 1–107 |

| 1–82 | AXPvme P2 Connector Pinout, Dual-Slot and Single-Slot | 1–109 |

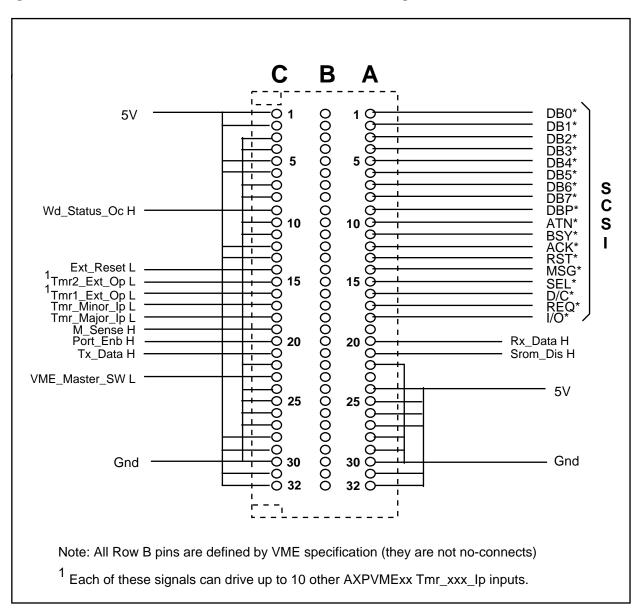

| 4–1  | Storage Locations of Environment Variables            | 4–2   |

| 5–1  | Memory Regions                                        | 5–14  |

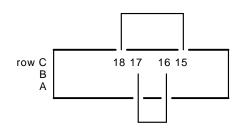

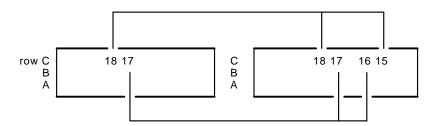

| 5–2  | Loopback Descriptions for Interval Timer Test 3 and 4 | 5–25  |

| 5–3  | LAN Address ROM Format                                | 5–37  |

| 5–4  | SROM Test Flows                                       | 5–43  |

| 5–5  | Console Power-On/Self-Test Flows                      | 5–44  |

| 5–6  | Console Power-On/Self-Test Flows                      | 5–45  |

| B–1  | Serial Line Connectors                                | B–1   |

| B–2  | Ethernet AUI Connector                                | B–2   |

| B–3  | SCSI Connector                                        | B–3   |

| B–4  | VMEbus P2 Connector                                   | B–4   |

| B–5  | PCI Option Connectors                                 | B–6   |

|      |                                                       |       |

## Tables

| 1–3 | AXPvme Backup Cache Memory Size      | 1–3  |

|-----|--------------------------------------|------|

| 1–2 | Dip Switch Functions                 | 1–5  |

| 1–3 | AXPvme Backup Cache Memory Size      | 1–8  |

| 1–4 | Configuration Space Addressing       | 1–11 |

| 1–5 | PCI Device Arbitration Control       | 1–13 |

| 1–6 | CPU Address Window to PCI            | 1–15 |

| 1–7 | PCI Target Window Masking            | 1–16 |

| 1–8 | PCI to CPU Address Translation       | 1–17 |

| 1–9 | Formation of AM Codes from S/G Entry | 1–25 |

| 1–10 | PCI BE# to Local A1,0 and SIZ1,0 Translation for Various Swap |       |

|------|---------------------------------------------------------------|-------|

|      | Modes                                                         | 1–35  |

| 1–11 | Local Bus A1,0 and SIZ1,0 to PCI BE# Translation              | 1–36  |

| 1–12 | DECchip 21040-AA CSRs                                         | 1–51  |

| 1–13 | 53C810 Register List                                          | 1–54  |

| 1–14 | SCC Baud Rates                                                | 1–72  |

| 1–15 | Timer Modes                                                   | 1–80  |

| 1–16 | VIC64 Interrupt Ranking                                       | 1–89  |

| 1–17 | Physical and Environmental Specifications                     | 1–110 |

| 1–18 | Power and Heat Dissipation at Processor Frequencies           | 1–110 |

| 2–1  | Frequently Used Commands                                      | 2–2   |

| 2–2  | Console Shell Operators                                       | 2–3   |

| 4–1  | ARM Defined Environment Variables                             | 4–2   |

| 4–2  | Console Diagnostic Environment Variables                      | 4–4   |

| 4–3  | Ethernet Configuration Environment Variables                  | 4–5   |

| 4–4  | Storage Configuration Environment Variables                   | 4–6   |

| 4–5  | Console Configuration Environment Variables                   | 4–7   |

| 5–1  | Test Patterns in Flash                                        | 5–1   |

| 5–2  | Console Diagnostic Tests                                      | 5–2   |

| A–1  | Physical and Environmental Specifications                     | A–1   |

| A–2  | Power Supply Current and Module Power Dissapation             | A–1   |

| B–1  | Serial Line Connectors                                        | B–1   |

| B–2  | Ethernet AUI Connector                                        | B–2   |

| B–3  | SCSI Connector                                                | B–3   |

| B–4  | VMEbus P2 Connector                                           | B–4   |

| B–5  | PCI Option J11 Connector                                      | B–6   |

| B–6  | PCI Option J12 Connector                                      | B–7   |

|      |                                                               |       |

# Preface

## Purpose

This guide describes the AXPvme module and its built-in features including the console code and diagnostics.

## Audience

This guide is intended for users who wish to have in-depth information about the AXPvme module. This guide does not provide programming information. For programming information, refer to the operating system calls section of your operating system documentation.

## **Related Documents**

| Document                                                             | Part Number |

|----------------------------------------------------------------------|-------------|

| AXPvme Single-Board Computer Installation/User Guide                 | EK-EBV1X-IN |

| VxWorks Digital AXPvme Single-Board Computers<br>Hardware Supplement | AA-QA5HA-TE |

| VxWorks Programmer's Guide                                           | AA-Q3YLB-TE |

| DEC OSF/1 Installation Guide                                         | AA-PS2DD-TE |

## Conventions

This manual uses the following conventions:

| Convention     | Meaning                                                                                                                                                       |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Return         | Press the key that executes commands or terminates a sequence. This key is labeled Return, Enter, or $\leftrightarrow$ , depending on your keyboard.          |

| Ctrl/x         | While you hold down the Ctrl key, press any other key.                                                                                                        |

|                | OSF and VxWorks commands are case sensitive. You must enter commands in the correct case, as printed in the text.                                             |

| Monospace type | Indicates examples of system output or user input.                                                                                                            |

| italics        | In commands and examples, italics indicates a value that you should supply.                                                                                   |

| U*X            | Is used in place of UNIX and ULTRIX in this document.                                                                                                         |

| []             | Square brackets in command descriptions enclose the optional command qualifiers. Do not type the brackets when entering information enclosed in the brackets. |

| Convention | Meaning                                                                                                                                                      |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | A vertical bar in command descriptions indicates that you have<br>a choice between two or more entries. Select one entry unless<br>the entries are optional. |

| {}         | Braces indicate that you are required to specify one (and only<br>one) of the enclosed options. Do not type the braces when you<br>enter the command.        |

| ()         | Parentheses enclose a set of options that must be specified together.                                                                                        |

1

# **Technical Hardware Specifications**

## 1.1 Overview

The AXPvme single-board computer is a 6U-sized Versa Module Eurocard bus (VMEbus) device with the low-cost Alpha (21066A) processor chip, memory, and peripheral device controllers on a single module. The AXPvme single-board computer is for VME real-time and embedded systems, where high performance with a Digital supported operating system is desirable. The supported operating systems are OSF/1 and VxWorks. Figure 1–1 shows a block diagram of the systems on the AXPvme module.

Figure 1–1 AXPvme Module Block Diagram

## 1.1.1 Related Hardware Specification Documents

The following documents should be used with the hardware specifications provided in this chapter:

- Alpha Architecture Reference Manual

- DECchip 21066-AA (Low-cost Alpha) Engineering Specification

- PCI Interface Specification 2.0

- DECchip 21040-AA Specification

- NCR 53C810 Documentation

- Intel 82378ZB Chip Specification

- Chip Specifications for 85C30, 8254, and VIC068/64

## 1.1.2 Conventions and Terms

The following conventions and terms are used in this chapter:

- All address numbering is in hexidecimal

- Other hexidecimal numbers are suffixed by "h," for example, 4C00h

- RO = Read only

- W1C = Write one to clear

- MBZ = Must be zero, for example, must be written as zero and expected as zero on reads

## 1.1.3 System Description

The AXPvme system is based on the LCA chip with the PCI as the onboard I/O bus.

## 1.1.3.1 LCA Processor

The Low-Cost Alpha chip (LCA) is a dual-issue Alpha implementation with full floating-point support, internal 8 Kbyte Instruction and Data caches, full memory, and I/O bus controllers, as well as a PLL clock generator.

## 1.1.3.2 Memory Controller

The LCA's integral memory controller handles all interface operations to the main memory and external write-back backup cache.

The AXPvme will support 8/16/32/64/128 Mbytes of DRAM memory.

The external backup cache is a fixed 256 Kbytes or 512 Kbytes depending on the module version. Table 1-3 shows the cache size of each AXPvme module.

| AXPvme<br>Module | Cache Size |  |

|------------------|------------|--|

| 64               | 256 Kbytes |  |

| 64LC             | 256 Kbytes |  |

| 160              | 256 Kbytes |  |

| 100              | 512 Kbytes |  |

| 166              | 512 Kbytes |  |

| 230              | 512 Kbytes |  |

Table 1–3 AXPvme Backup Cache Memory Size

#### 1.1.3.3 I/O Controller

The LCA's integral I/O controller implements the interface to the peripheral component interconnect (PCI) bus. The PCI is used as the system I/O bus. All I/O is mapped into the 32-bit PCI address space. Byte, Word, Longword, and Quadword accesses over the PCI are support for CPU initiated cycles. The I/O controller also acts as a PCI target and PCI to main memory bridge for I/O initiated transfers and DMAs.

#### 1.1.3.4 VME Interface

AXPvme supports a full master/slave VME interface to IEC 821, IEEE1014-1987 standards. The module can act as VME system controller (in slot 1), and as such, handles bus arbitration, interrupt handling, and so forth.

The VME interface operates in A16, A24, and A32 addresses spaces with D08, D16, D32, and D64 data transfers.

As a VME master, AXPvme can be programmed to any of the four bus request levels. The system will be a fair requester and can be programmed to releaseon-request or when done. An outbound programmable scatter/gather (S/G) is used to facilitate flexible VME access. This S/G allows access to 2048 256-Kbyte pages of VME space and is used to specify address modifier and byte swapping information, and so forth. Full outgoing DMA bursts are supported for fast memory to VME target data transfer. Support for D64 transfers offer data rates of up to >24 Mbytes/s.

As a slave, AXPvme responds to programmed addresses in the A24 and A32 VME address spaces. D08, D16, D32, and D64 transfers including block modes (no D08 block mode) and read-modify-write cycles are supported (though not atomic to main memory). An inbound S/G is employed to give flexibility in slave addressing of the 8-128 Mbytes of AXPvme main memory. The S/G also allows write-protection of designated pages and the implementation of interrupt-based inbound S/G page monitoring.

Byte swapping (selectable via S/G entries) is provided to ease data interchange between the little-endian Alpha AXP and other architectures without software overhead.

Interprocessor communication registers in A16 space are provided for limited message passing and signaling.

#### 1.1.3.5 Network Interface (IEEE 802.3)

A PCI-based network interface is standard on the AXPvme system. Connection to a network is via AUI at the front panel.

## 1.1.3.6 SCSI

A PCI-based SCSI interface is embedded on the AXPvme computer modules. This interface will provide SCSI-2 support (hardware will support either target and/or initiator). Connection to the SCSI interface is via a P2 breakout module using a standard nonshielded 50-pin low-density connector.

#### 1.1.3.7 ROM

4 Mbyte of flash ROM is provided on processors with 512 Kbyte of cache while 1 Mbyte of flash ROM is provided on processors with 256 Kbyte cache for console, diagnostics, PAL code store, and user-specific applications. This ROM is implemented in flash EPROM to allow in-place ROM updates. Updates are enabled/disabled via software and a module DIP switch. For full details of the ROM usage, see Section 1.11.

The 4 Mbyte of flash ROM is accessed in the bottom 1 Mbyte of PCI memory space. Two bits in the MODULE CONTROL2 REGISTER select the current 1 Mbyte window mapped into PCI space. The systems with 1 Mbyte of flash ROM directly access this ROM without mapping.

#### 1.1.3.8 Console UART

The AXPvme console is driven by a serial line DUART port. This DEC423 port is one of two asynchronous serial lines on the module.

## 1.1.3.9 Watchdog

A watchdog timer is included as a programmable fail-safe on system software. If enabled and allowed to expire, the watchdog first halts the CPU (causing a jump to console firmware) and then resets the entire AXPvme. On watchdog reset an open-collector signal, accessible via P2, is asserted and the amber front panel LED lights.

#### 1.1.3.10 Interval Timers

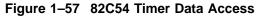

AXPvme features three programmable 16-bit interval timer/counters. Two of the timers are driven from a fixed 10 MHz clock, and can be used to generate rate outputs (via P2 pins) or onboard interval interrupts. The third counter /timer is clocked and gated by external inputs (via P2 pins) for event counting or synchronization. The output of this final counter can be enabled to generate an onboard interrupt request.

## 1.1.3.11 TOY Clock

A basic time-of-year function with battery backup is included on the AXPvme module. This device keeps time and date information with a resolution of 0.01 seconds and an accuracy of +/-1 minute per month, at 25°C.

#### 1.1.3.12 Nonvolatile RAM

32 Kbytes of nonvolatile RAM are available on the AXPvme card. For full details of the layout and use of the onboard NVRAM, refer to Section 1.16. An onboard DIP switch allows the NVRAM to be supplied by the backplane 5 V standby (to remove dependence on the internal battery). The device will retain data for 10 years in the absence of Vcc, at 25°C.

#### 1.1.3.13 Display

There is a single alphanumeric display on the front panel of the AXPvme, which is accessible in I/O space. The display is used for firmware status information. When not running resident firmware, the display is available for use under user software control.

## 1.1.3.14 PCI Mezzanine

A single PCI mezzanine connector is located on the system module to allow a PCI option daughtercard to be plugged in. PCI bus arbitration logic in AXPvme fully supports one optional PCI device with up to four PCI option interrupt request lines. The PCI clock is driven from AXPvme at a frequency of 32 MHz with processors with 256 Kbyte chache and 33 Mhz on processors with 512 Kbyte of cache.

## 1.1.3.15 DIP Switches

AXPvme modules have a set of four DIP switches used to enable/disable various functions. These switches are physically located behind the Network AUI connector and are labeled 1 through 4. The switches and their functions are listed in Table 1–2.

| Switch No. | Open                                                                            | Closed                                                                                                                                                                                                              |

|------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | TOY clock has no connection to<br>VME 5 V standby suppy.                        | TOY 5 V line assisted by VME standby power (extends battery life).                                                                                                                                                  |

| 2          | Flash ROM updates are disabled (Vpp = 0 V).                                     | Flash ROM updates are enabled (Vpp = $+12$ V).                                                                                                                                                                      |

| 3          | VME bus resets do not generate<br>a module reset.                               | VME bus resets will generate a module reset.                                                                                                                                                                        |

| 4          | Configures the VME corner<br>to not be the VME system<br>controller on powerup. | Configures the VME corner to be VME<br>system controller on powerup. This has<br>the same effect as connecting VMEP2<br>pin A23 (VME_MASTER_SWL) to<br>ground for the AXPvme 66, AXPvme<br>100, and the AXPvme 231. |

Table 1–2 Dip Switch Functions

The default configuration, as delivered from the factory, assumes the module will be a VME system controller (will perform VME bus arbitration from slot 1).

**Default Switch Settings:**

| 1 - | Closed | (Allow VME 5 V standby power to assist TOY supply) |

|-----|--------|----------------------------------------------------|

| 2 - | Open   | (Flash updates disabled)                           |

| 3 - | Open   | (VMEbus resets do not reset module)                |

| 4 - | Closed | (Configured as VME system controller)              |

An alternate configuration assumes the module is not a VME system controller (is not in slot 1 and does not perform VME bus arbitration).

Nonsystem Controller Switch Settings:

| 1 - | Closed | (Allow VME 5 V standby power to assist TOY supply) |

|-----|--------|----------------------------------------------------|

| 2 - | Open   | (Flash updates disabled)                           |

| 3 - | Closed | (VMEbus resets do reset module)                    |

| 4 - | Open   | (Not configured as VME system controller)          |

Note that switches 3 and 4 must always be configured opposite (one open, one closed) for normal system operation.

\_ Note \_\_

The AXPvme 66, AXPvme 100, and AXPvme 231 may be configured as the VME system controller by closing switch 4 or by grounding VMEP2 pin A23. Switch 4 must be **open** and VMEP2 pin A23 must **not** be connected to ground for the modules to operate as a non-controller.

## **1.2 LCA Processor**

The DECchip 21066A microprocessor is the second in a family of chips to implement the Alpha AXP architecture. The 21066A is a CMOS based superscalar, superpipelined processor using dual-instruction issue. The DECchip 21066A incorporates a high level of system integration to provide the best-inclass system performance for cost-focused applications. It integrates on-chip fully pipelined integer and floating-point processors, a high bandwidth memory controller, an industry standard I/O controller, an embedded graphics accelerator, internal instruction and data caches, and external cache control.

Summary of the DECchip 21066A features \*:

- Fully pipelined, 64-bit RISC architecture

- Supported by multiple operating systems:

- OSF

- VxWorks

- Best-in-class performance

- 231 MHz operation (AXPvme 230)

- Superscalar, superpipelined (dual issue)

- Pipelined on-chip floating-point unit:

- IEEE single- and double-precision, Digital F\_floating and G\_floating, longword and quadword data types. Limited support for D\_floating data type.

- On-chip demand-paged memory management unit:

- A 12-entry I-stream translation buffer with 8 entries for 8Kbyte pages and 4 entries for 4 MB pages

- A 32-entry D-stream translation buffer with each entry able to map a single 8K, 64K, 512K, or 4 MB page.

- Super page mapping

- On-chip high-bandwidth memory controller:

- Full 64-bit memory datapath

- Dynamic RAM (DRAM) controller

- 64-bit error correction code (ECC)

<sup>\*</sup> Refers to utilization in AXPvme dual-slot

- Supports up to 4 banks of memory

- RAS/CAS memory bus

- PCI I/O controller

- 32-bit multiplexed address/data

- Industry standard

- Burst mode reads and writes

- Asynchronous operation to CPU

- Multimaster with peer-to-peer access

- On-chip 8-Kbyte direct mapped write-through data cache

- On-chip 8-Kbyte direct mapped instruction cache

- On-chip control for optional, external, write-back secondary cache:

- Programmable cache size and speed

- Built-in phase-locked loop (PLL)

- Frequency multiplier allows low-cost input clock

- Programmable multiplier values

- Serial ROM interface:

- Loads Icache after reset

- Software controlled serial port after initialization

- 3.3 V supply voltage

- Interfaces directly to 5 V logic

Please refer to the DECchip 21066-AA (Low Cost Alpha Microprocessor Engineering Specification) for details of the LCA chip.

## 1.3 Memory Subsystem

The memory subsystem of the AXPvme system can be divided into two sections:

- Main memory

- External Bcache

The memory controller, internal to the DECchip 21066, handles the operation and control of the external memories under the configuration control of various LCA internal registers.

An 8-bit ECC is used on the 64-bit memory word for single-bit error correction and double-bit/nibble error detection. The controller generates a CAS-before-RAS cycle to refresh all banks simultaneously.

The AXPvme system will support 8/16/32/64/128 Mbytes of main memory.

The external backup cache of AXPvme is a fixed 256 Kbyte or 512 Kbyte SRAM write-back configuration, depending on the module version.

## 1.3.1 Main Memory

The memory interface is of the form shown in Figure 1–2. The memory controller attempts to maximize fast-page-mode operation. In this way the maximum memory bandwidth for AXPvme is approximately 75 Mbytes/s with a sustainable bandwidth of 64 Mbytes/s shared evenly between the CPU and the IOC.

## 1.3.2 Backup Cache

The external Bcache is an optional system component that increases overall system performance by returning cached main-memory data faster than is possible from the DRAMs. The cache is implemented as 512 Kbytes SRAM. The cache tag size (see Figure 1–3) depends on the cache size. Table 1–3 shows the cache size of each AXPvme module.

Table 1–3 AXPvme Backup Cache Memory Size

| AXPvme |            |  |

|--------|------------|--|

| Module | Cache Size |  |

| 64     | 256 Kbytes |  |

| 64LC   | 256 Kbytes |  |

| 160    | 256 Kbytes |  |

| 100    | 512 Kbytes |  |

| 166    | 512 Kbytes |  |

| 230    | 512 Kbytes |  |

## Figure 1–3 Cache Tag

The cache word size is a quadword.

To allow caching of any memory address in the 512-Mbyte range for a 512-Kbyte Bcache requires 10 tag bits. In addition, the cache interface requires one parity bit and one "dirty" bit associated with each tag entry. This gives a total of 12 tag RAM storage bits required.

## 1.3.3 Memory Initialization

Each memory bank in the AXPvme system is controlled by the values in four associated registers. The correct configuration is set at module power on and should not be altered. There is a single Global Timing Register, which affects all system banks. Each bank then has 3 bank-specific registers to configure to individual bank needs.

The serial ROM configures memory as follows:

- 1. Global timing register (GTR)

- 2. Individual bank setup as required

- a. Bank timing registers (BTRs)

- b. Bank address mask register

- c. Bank configuration register

The two types of timing registers allow the memory controller interface of the LCA to be tailored to the type and speed of RAM chips used in the system.

The basic RAM configuration of the AXPvme system is banks of 4 Mbit DRAM chips with an access time of 70 ns. The number of banks, 2 or 4, is a function of the memory array installed.

For further details of these registers, see the LCA specification in Section 1.5.5.

## 1.3.4 Error Handling

There are two error registers associated with the memory interface of the LCA. These are the error status register and the error address register.

The error status register gives syndrome information associated with a memory interface error while the error address register freezes with the address of the access that caused an error.

For bit definitions and more information, see Section 5.6 in the LCA Specification Rev 2.1.

## 1.4 I/O Subsystem

The AXPvme I/O subsystem is based on the PCI bus. For full details of the PCI, refer to the PCI Specification V2.0. All of the module's I/O components are connected via the 32-bit, 5 V only, PCI implementation. The Low Cost Alpha has an integral PCI bridge interface to which each of the other devices connect.

The main elements of the I/O subsystem are:

- LCA<->PCI bridge

- PCI central arbiter<sup>1</sup>

- VME interface

- SIO interface (giving connectivity to TOY, UART, ROM, and so forth.)

- Ethernet interface

- SCSI interface

- System interrupt controller<sup>1</sup>

- Mezzanine (PCI) connector

The maximum number of PCI devices supported for direct connection to AXPvme's PCI bus is six. They are the LCA, NI, SCSI, ISbus, VME adapters, and one other PCI option (which are supported via the mezzanine architecture). However, hierarchical configuration is supported to allow additional PCI devices connected over PCI-PCI bridges, and so forth.

## 1.4.1 PCI Addressing and Configuration

The base address of each PCI device, except the SIO, is programmable.

The individual base addresses are initialized by writing device configuration registers. The PCI defines a set of configuration registers for PCI compliant devices, which are accessible in PCI configuration space.

Within this special address space a fixed device select scheme is used to define the location of each device's configuration block.

The PCI defines a maximum size of 256 bytes for a configuration register block for any one device. The byte within the configuration area is defined by PCI\_ AD<7:0>, while PCI\_AD<10:8> are reserved for configuration function codes. Thus, only the lowest 11 bits of the LCA's generated (and driven) 32-bit address are needed to select any location in a device's configuration region. In this way, address bits 11 to 15 can be used for a "no-logic" device select decode in AXPvme. In PCI configuration space, the seven supported devices can be accessed at the locations shown in Table 1–4.

<sup>&</sup>lt;sup>1</sup> The PCI arbitration and system interrupt controller are not PCI devices but do have registers that are accessed in PCI I/O space.

| Device    | Configuration Address | Notes            |

|-----------|-----------------------|------------------|

| VME I/F   | 00000800 - 000008FF   | 4 base addresses |

| NI        | 00001000 - 000010FF   | -                |

| SCSI      | 00002000 - 000020FF   | -                |

| SIO I/F   | 00004000 - 000040FF   | _                |

| PCI Opt 1 | 00008000- ?           | Option dependent |

| LCA       | N/A                   | N/A              |

Table 1–4 Configuration Space Addressing

PCI configuration cycles can be driven from the LCA when the disable configuration bit in the IOC control status register is cleared. When this bit is cleared (for example, after reset), all accesses to normal PCI I/O addresses will map to configuration space cycles. Figure 1–4 shows the generic configuration space header.

## Figure 1–4 Generic Configuration Space Header

|                            |              |                           |                    | 6        | (From the table above) |

|----------------------------|--------------|---------------------------|--------------------|----------|------------------------|

| Device                     | e ID         | Ven                       | dor ID             | : CONFIG | _BASE + 00             |

| Status                     | 3            | Com                       | imand              | :        | + 04                   |

|                            | Class Code   | e                         | Rev ID             | :        | + 08                   |

| BIST                       | Hdr Type     | Laten <u>c</u> y<br>Timer | Cache Line<br>size | :        | + 0C                   |

|                            |              |                           | :                  | + 10     |                        |

| ¦ 1 to                     | o 6 Base Ado | dress Regist              | ers                |          |                        |

|                            |              |                           | :                  | + 24     |                        |

| Reserved                   |              |                           | :                  | + 28     |                        |

| Reserved                   |              |                           | :                  | + 2C     |                        |

| Expansion ROM Base Address |              |                           | :                  | + 30     |                        |

|                            | Res          | erved                     |                    | :        | + 34                   |

| Reserved                   |              |                           |                    | :        | + 38                   |

| Max_Lat                    | Min_Gnt      | Intr. Pin                 | Intr. Line         | :        | + 3C                   |

|                            | Device       | specific                  |                    | :        | + 40 to +FC            |

Configuration cycles with more than one of the address bits <11:15> set MUST NOT be made. There is no hardware mechanism to protect the user from the unpredictable results that this could cause.

Most of the devices that reside in PCI I/O in the AXPvme design have programmable base address registers that are set up in configuration space. Figure 1–5 shows each device and the layout of its base address registers.

| Device                                                   | Size                                               | Mem       | ю            | Base Register                             |

|----------------------------------------------------------|----------------------------------------------------|-----------|--------------|-------------------------------------------|

| VME - Registers<br>- PCI->VME<br>- S/G RAM<br>- PCI->VME | 512 bytes<br>512 Mbytes<br>128 Kbytes<br>64 Mbytes | ~ ~ ~ ~ ~ |              | 31 9 0<br>MBZ [0]<br>MBZ0<br>MBZ0<br>MBZ0 |

| NI - Registers                                           | 512 bytes                                          |           | $\checkmark$ | 31 0<br>                                  |

| SCSI - Registers<br>- Registers                          | 128 bytes<br>128 bytes                             | <         | <            | 31                                        |

Figure 1–5 PCI Devices, Size, and Base Registers

For further information about individual configuration registers, see the corresponding I/O device section.

## 1.4.2 PCI Arbitration

Arbitration for the PCI bus is centralized. A single bus arbiter monitors all "requests" for use of the bus and, based on some allocation scheme, decides on a bus winner to which it gives a "grant". The bus is owned by the winning device (once it takes up the grant by starting a cycle) until it finishes its cycle; that is, bus ownership is access based.

AXPvme's PCI arbitration logic is based on a fixed-priority allocation scheme. There is a small amount of programmability to the arbitration priority allocation, however, it is not intended as a general-purpose arbitration priority control mechanism. Currently, three priority schemes are supported based on the value written into the MOD\_CNTRL\_REG register bits <3:2>. These two bits will allow limited control over the PCI arbitration priority assignment based on the following scheme:

| Priority | <3:2>=00 | <3:2>=01 | <3:2>=10 | <3:2>=11 |

|----------|----------|----------|----------|----------|

| 1        | LCA      | PCI      | VME      | Reserved |

| 2        | ENET     | LCA      | LCA      | Reserved |

| 3        | SCSI     | VME      | PCI      | Reserved |

| 4        | PCI      | ENET     | ENET     | Reserved |

| 5        | VME      | SCSI     | SCSI     | Reserved |

Bus arbitration can also be tuned by modifying the way in which the various devices use their bus grants.

If the PCI device is programmed with a maximum data burst length, the duration for which the device will hold the bus is limited by a maximum data transfer. After the defined amount of data is transferred, the bus owner will give up the bus. Note that even with a programmed maximum bus burst length, there is no guarantee how long the bus owner will hold the bus. However, good device design should minimize holding of the bus when a master does not have data to transfer.

The second PCI mechanism for limiting the ability of one device to control the bus is the latency timer scheme.

| Priority    | Device    | Programmable<br>Burst | Latency<br>Timeout | Bandwidth   |

|-------------|-----------|-----------------------|--------------------|-------------|

| 6 (highest) | LCA       | Max=Quadword          | No                 | ?           |

| 5           | NI        | Yes                   | Yes                | 2 Mbyte/s   |

| 4           | SCSI      | Yes                   | Yes                | 5 Mbyte/s   |

| 3           | PCI Opt 1 | ?                     | ?                  | ?           |

| 2           | VME I/F   | Max=2<br>Quadwords    | Yes                | >24 Mbyte/s |

Table 1–5 PCI Device Arbitration Control

A latency timer value in the PCI configuration space of a device defines a minimum guaranteed bus tenure (measured in PCI cycles following the assertion of Frame#) beyond which the removal of the grant signal forces the device to end its access after the current data transfer completes.

AXPvme's fixed-priority arbiter understands the operation of the PCI latency timer mechanism. The bus is granted to the highest priority requester but once the winner starts its cycle, the arbiter will rearbitrate on the bus. The new winner cannot and will not (PCI specification) use the bus until the current owner concludes its cycle. This mechanism of reevaluating the bus winner during an active PCI cycle allows for full and efficient use of a device-based latency timeout scheme.

The arbiter will support "parking" the idle PCI bus with any one of the LCA, the VME interface, the NI, or PCI option 1. Selecting the device with which to park is programmed via two bits in the module control register (see Figure 1–6).

## Figure 1–6 Module Control Register (PCI Park)

## 1.4.3 PCI Transfer

The Alpha AXP architecture does not currently support transfers smaller than longword quantities. The PCI devices often require transfers of bytes and words rather than full 32-bit longword data. To this end, the LCA employs a mechanism for reading and writing arbitrary bytes and words when accessing PCI space. See DECchip 21066-AA Rev. 2.1 Section 6.2.6.1 for a better description of sparse space addressing.

This mechanism allows I/O addresses to be formed with encoded information pertaining to the number of bytes and byte offset. In particular, the LCA I/O address has the form shown in Figure 1–7.

Figure 1–7 LCA I/O Addressing

The LCA operates as a PCI master when the CPU executes a load or store instruction that addresses a PCI peripheral space The LCA's IOC provides address windows to the CPU that allow access to the memory, I/O, and configuration address spaces of PCI. The IOC also provides a register that, when read, will generate a PCI interrupt acknowledge cycle, or when written, will generate a PCI "special cycle".

The address ranges for the various PCI address spaces supported are listed in Table 1–6.

Throughout the text, I/O and memory addresses on the PCI are specified. The addresses described are the physical addresses that would appear on the PCI AD lines. If sparse space addressing is needed (less than longword data size), these address values should be inserted into the "PCI byte Address" field in the format above in order to form the CPU address.

| CPU Address <33:00>        | Access     | PCI Address Space     |  |

|----------------------------|------------|-----------------------|--|

| 1 Axxx xxxx<br>1 Bxxx xxxx | Read Only  | Interrupt Acknowledge |  |

| 1 Axxx xxxx<br>1 Bxxx xxxx | Write Only | Special Cycle         |  |

| 1 Cxxx xxxx<br>1 Dxxx xxxx | R/W        | I/O                   |  |

| 1 Exxx xxxx<br>1 Fxxx xxxx | R/W        | Configuration         |  |

| 2 xxxx xxxx                | R/W        | Sparse Memory         |  |

| 3 xxxx xxxx                | R/W        | Dense Memory          |  |

Table 1–6 CPU Address Window to PCI

Due to the encoding of the CPU address used to generate PCI byte enables, only 27 physical address bits (CPU Addr<31:5>) can be used to generate the PCI address (AD<26:0>). This gives an effective PCI address space of 128 Mbytes. This 128 Mbytes is subdivided into a 16-Mbyte region and a 112-Mbyte region. The top 5 address bits of the PCI address (AD<31:27>) are generated differently, depending on which of these regions is referenced.

The bottom 16 Mbytes always map to the bottom 16 Mbytes of the PCI space, while the remaining 112 Mbytes can be mapped to the top 112 Mbytes in any naturally aligned 128-Mbyte window.

For this latter 112-Mbyte portion of the CPU to PCI window, the high-order 5 address bits are supplied from the Hardware Address Extension bits in the IOC\_CNTRL register in the LCA (at CPU address 180000000h); that is, bits <31:27>. In other words, when addressing one of the PCI spaces described above,

if CPU Addr<31:29> = 000 then PCI AD<31:27> = 00000 else PCI AD<31:27> = HAE<31:27>.

## 1.4.3.1 Masked Transfers

Although the IOC supports arbitrary byte enables, only dual and tri-bytes that are contiguous and do not straddle a longword boundary are allowed.

To generate a masked PCI write transfer, always use an STL. This will become a single beat data burst on the PCI.

Either an LDQ or LDL instruction can be used to generate a masked PCI read. Again, the PCI burst length will be one.

#### 1.4.3.2 Unmasked Transfers

Unmasked PCI write transfers can be generated by either an STL or STQ, with CPU address bits  $\langle 4:3 \rangle = 11$ . The STL will produce a cycle of burst length 1 while an STQ will contain two data beats on the PCI.

Unmasked PCI read transfers can be generated by either an LDL or LDQ, with CPU address bits  $\langle 4:3 \rangle = 11$ . The LDL will produce a PCI transfer of burst length 1 while an LDQ will produce a PCI transfer of burst length 2.

See Section 6.2, CPU Initiated PCI Cycles, in the LCA Specification for further details.

## 1.4.4 Main Memory as PCI Target

The I/O controller of the LCA allows a window from the 32-bit PCI memory address space to be mapped to a 34-bit address for system main memory.

PCI initiated masked reads are treated as unmasked reads by the LCA, while arbitrary byte enable combinations for PCI initiated writes are implemented by a read-modify-write operation in the 21066 memory controller.

Memory coherency is maintained for all PCI initiated transfers to cacheable memory.

Registers internal to the LCA are not accessible by PCI devices.

In order to allow the window from PCI to memory to exist, it is necessary to translate the PCI address to the CPU address. The IOC provides two programmable address windows that control access by PCI peripherals to system memory. These address windows are referred to as the PCI Target Windows. There is a set of three registers associated with each PCI Target Window-Window Base register, Window Mask register, and Translation Base register.

Bits <31:20> of the Window Base register specify a starting address in the PCI memory address space for the target window. Bits <31:20> of the Window Mask register provide a mask for base address matching between the PCI address and the Window Base register. A one in the Window Mask register means the corresponding address bit does not take part in the base address match. Thus, the size of the window is controlled by the mask register as shown in Table 1–7. Note also that a target window must always be naturally aligned.

| WINDOW_MASK<31:20> | Size of Window          |

|--------------------|-------------------------|

| 0000 0000 0000     | 1 Mbyte                 |

| 0000 0000 0001     | 2 Mbytes                |

| 0000 0000 0011     | 4 Mbytes                |

| 0000 0000 0111     | 8 Mbytes                |

| 0000 0000 1111     | 16 Mbytes               |

| 0000 0001 1111     | 32 Mbytes               |

| 0000 0011 1111     | 64 Mbytes               |

| 0000 0111 1111     | 128 Mbytes              |

| All others         | Not supported by AXPvme |

Table 1–7 PCI Target Window Masking

Note also that there are two control bits in  $\langle 33:32 \rangle$  of the Window Base register. Bit $\langle 33 \rangle$  is a window enable bit. When cleared, the corresponding PCI target window is disabled. Bit<32> is a S/G enable bit. When cleared, there is a direct mapping from the PCI memory address to the CPU system memory address. The LCA supports PCI—memory S/Ging when this bit is set. Refer to the LCA Specification for full details of this facility.

When direct translation is used, the high-order address bits of the CPU address formed are supplied from the window's Translation base register, while the lower order bits are passed from the PCI unaltered. The number of Translation register bits used depends on the window size.

For more information, refer to Section 6.3 of the LCA Specification.

## 1.4.5 PCI Address Space Layout

Using the PCI base address registers (see Section 1.4.1) in each of the PCI devices, the layout of PCI address space can be defined. Table 1–8 shows the PCI to CPU address translation.

Note that within a given PCI space (memory or I/O), devices must not be configured to overlap.

| Window Size | CPU Address                        | Translation_Base Register<br>Unused Bits MBZ |

|-------------|------------------------------------|----------------------------------------------|

| 1 Mbyte     | Trans_Base<33:20> : PCI_ADDR<19:0> | Trans_Base<19:9>                             |

| 2 Mbyte     | Trans_Base<33:21> : PCI_ADDR<20:0> | Trans_Base<20:9>                             |

| 4 Mbyte     | Trans_Base<33:22> : PCI_ADDR<21:0> | Trans_Base<21:9>                             |

| 8 Mbyte     | Trans_Base<33:23> : PCI_ADDR<22:0> | Trans_Base<22:9>                             |

| 16 Mbyte    | Trans_Base<33:24> : PCI_ADDR<23:0> | Trans_Base<23:9>                             |

| 32 Mbyte    | Trans_Base<33:25> : PCI_ADDR<24:0> | Trans_Base<24:9>                             |

| 64 Mbyte    | Trans_Base<33:26> : PCI_ADDR<25:0> | Trans_Base<25:9>                             |

| 128 Mbyte   | Trans_Base<33:27> : PCI_ADDR<26:0> | Trans_Base<26:9>                             |

| All others  | Not supported by AXPvme            |                                              |

Table 1–8 PCI to CPU Address Translation

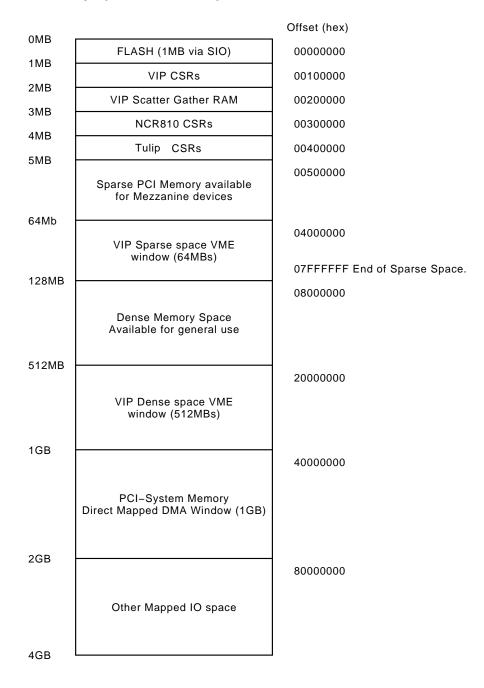

#### 1.4.5.1 PCI Memory Space

The flash ROM is fixed in the PCI Memory space. It takes up the first 1 Mbyte of the address map, from 00000000h to 000FFFFFh.

DC7407 Control and Status registers (including VIC64 registers) will be located starting at address 00100000h.

VME interface S/G RAM is defined to reside in PCI memory. This should be programmed to some convenient, naturally aligned 128-Kbyte block. This base address will be initialized by firmware and should not be altered thereafter. The recommended base address is 00200000h.

The 53C810 allows its register space to be accessed with PCI Memory space cycles. This register region is 128 bytes in extent. This base address will be initialized by firmware and should not be altered thereafter. The recommended base address is 00300000h.

The DECchip 21040-AA Control and Status registers are accessible through both PCI Memory and PCI I/O address space. The recommended base address in PCI Memory space is 00400000h.

The address space between 00500000h and 03FFFFFFh is defined as Sparse space available for PCI Mezzanine devices (approximately 59 Mbytes).

The remainder of LCA Sparse space, 04000000h through 07FFFFFh, is defined as the DC7407 Sparse space VME window (64 Mbytes).

Address 08000000h defines the start of 384 Mbytes of Dense Memory space available for general use.

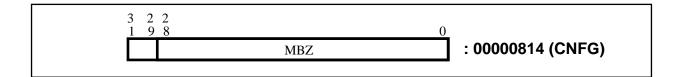

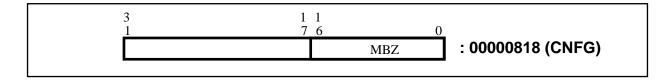

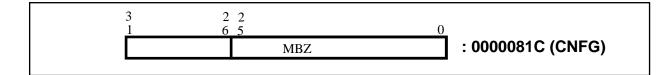

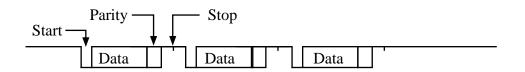

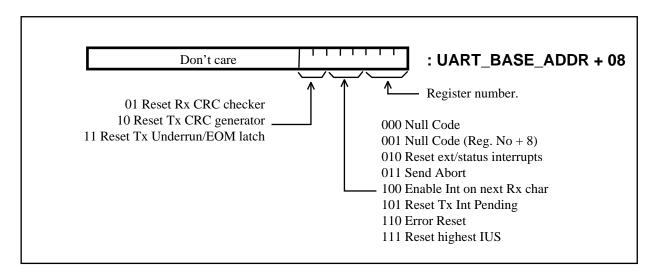

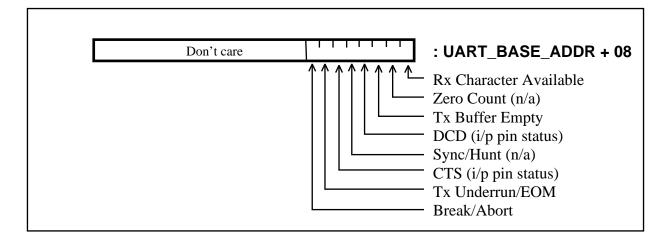

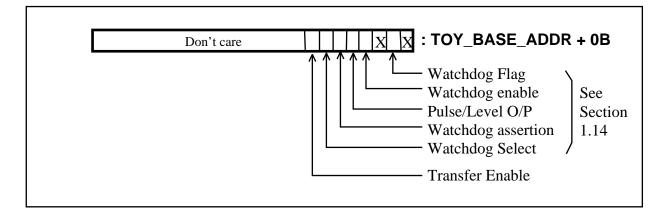

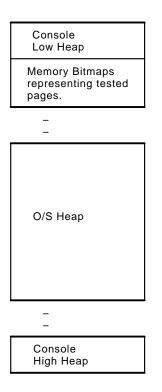

Address 2000000h defines the start of a 512 Mbyte DC7407 Dense Space VME window.