# AlphaServer 8200/8400 System Technical Manual Supplement: Memory

Order Number: EK-MS7CC-TS. A01

This document is a supplement to the *AlphaServer 8200/8400 System Technical Manual*. It discusses the specific features of the 4-Gbyte MS7CC-GA memory module. A maximum of seven MS7CC-GA memory modules can be configured in a system, offering a total memory capacity of 28 gigabytes.

digital equipment corporation maynard, massachusetts

#### First Printing, March 1997

Digital Equipment Corporation makes no representations that the use of its products in the manner described in this publication will not infringe on existing or future patent rights, nor do the descriptions contained in this publication imply the granting of licenses to make, use, or sell equipment or software in accordance with the description.

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation.

Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software, if any, described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license. No responsibility is assumed for the use or reliability of software or equipment that is not supplied by Digital Equipment Corporation or its affiliated companies.

Copyright © 1997 by Digital Equipment Corporation.

All Rights Reserved. Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation: AlphaServer, DEC LANcontroller, OpenVMS, StorageWorks, VAX, and the DIGITAL logo.

MEMORY CHANNEL is a trademark of Encore Computer Corporation.

**FCC NOTICE:** The equipment described in this manual generates, uses, and may emit radio frequency energy. The equipment has been type tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such radio frequency interference when operated in a commercial environment. Operation of this equipment in a residential area may cause interference, in which case the user at his own expense may be required to take measures to correct the interference.

# Contents

| Preface | . v |

|---------|-----|

|---------|-----|

## Chapter 1 Introduction

| 1.1   | Features                  | 1-1 |

|-------|---------------------------|-----|

| 1.2   | Major Sections            | 1-2 |

| 1.2.1 | Control Address Interface | 1-3 |

| 1.2.2 | Memory Data Interface     | 1-3 |

| 1.2.3 | DRAM Arrays               | 1-4 |

| 1.3   | Memory Organization       |     |

| 1.4   | Memory Interleave         | 1-5 |

| 1.5   | Refresh                   | 1-6 |

# Chapter 2 Registers

| 2-3<br>2-3 |

|------------|

| 2-3        |

|            |

|            |

| 2-6        |

| 2-10       |

| 2-13       |

| 2-15       |

| 2-17       |

| 2-20       |

| 2-21       |

| 2-23       |

| 2-26       |

| 2-28       |

| 2-30       |

| 2-34       |

| 2-35       |

| 2-38       |

|            |

# Chapter 3 Self-Test

| 3.1 | Self-Test Versions        | 3-1 |

|-----|---------------------------|-----|

| 3.2 | Self-Test Modes           | 3-1 |

| 3.3 | Self-Test Error Reporting | 3-2 |

|     | Self-Test Operation       |     |

|     |                           |     |

| 3.5 | Self-Test Performance | . 3-3 |

|-----|-----------------------|-------|

|     |                       |       |

# Figures

| 1-1 | MS7CC-GA Memory Module Block Diagram       | 1-2 |

|-----|--------------------------------------------|-----|

| 1-2 | Interleaving Different Size Memory Modules |     |

# Tables

| 1    | DIGITAL AlphaServer 8200 and 8400 Documentationvi                 |

|------|-------------------------------------------------------------------|

| 2    | Related Documents viii                                            |

| 1-1  | Memory Array Capacity1-5                                          |

| 2-1  | TLSB Node Space Base Addresses                                    |

| 2-2  | TLSB Required Memory Registers                                    |

| 2-3  | Memory-Specific Registers                                         |

| 2-4  | TLDEV Register Bit Definitions                                    |

| 2-5  | TLBER Register Bit Definitions                                    |

| 2-6  | TLCNR Register Bit Definitions                                    |

| 2-7  | TLVID Register Bit Definitions                                    |

| 2-8  | TLFADRn Register Bit Definitions                                  |

| 2-9  | TLESRn Register Bit Definitions                                   |

| 2-10 | SECR Register Bit Definitions                                     |

| 2-11 | MIR Register Bit Definitions                                      |

| 2-12 | MCR Register Bit Definitions                                      |

| 2-13 | STAIR Register Bit Definitions                                    |

| 2-14 | STAIR Register Bit Correspondence of Memory Address Segments 2-27 |

| 2-15 | STER Register Bit Definitions                                     |

| 2-16 | MDRA Register Bit Definitions                                     |

| 2-17 | MDRB Register Bit Definitions                                     |

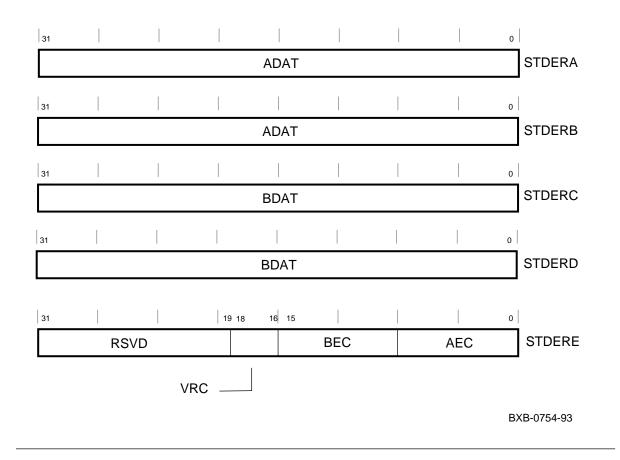

| 2-18 | STDER A, B, C, D Register Bit Definitions 2-36                    |

| 2-19 | STDERE Register Bit Definitions                                   |

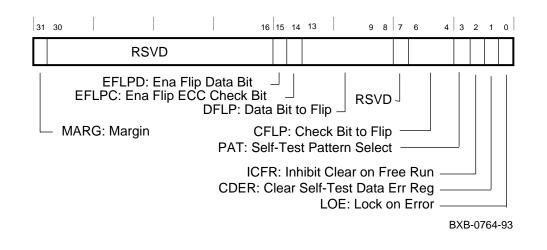

| 2-20 | DDRn Register Bit Definitions                                     |

| 3-1  | Self-Test Error Registers                                         |

| 3-2  | Self-Test Times: Normal Mode                                      |

| 3-3  | Self-Test Times: Moving Inversion, No Errors Found 3-4            |

### **Intended Audience**

This manual describes the MS7CC-GA 4-gigabyte memory module designed for use in AlphaServer 8200 and 8400 systems. It provides an overview of the operations of the memory module and gives detailed information on the subsystem registers. The manual is intended for technical professionals such as operating system programmers and customer service engineers.

### **Document Structure**

This manual has three chapters:

- **Chapter 1, Introduction,** gives an overview of the MS7CC-GA memory module.

- **Chapter 2, Registers,** describes in detail the TLSB required and memory-specific registers.

- **Chapter 3, Self-Test,** gives a general discussion of the self-test of the MS7CC-GA memory module.

## **Documentation Titles**

Table 1 lists the books in the DIGITAL AlphaServer 8200 and 8400 documentation set. Table 2 lists other documents that you may find useful.

| Table 1 | DIGITAL | AlphaServer | 8200 and | 8400 | Documentation |

|---------|---------|-------------|----------|------|---------------|

|---------|---------|-------------|----------|------|---------------|

| Title                                         | Order Number                              |

|-----------------------------------------------|-------------------------------------------|

| Hardware User Information and Installation    |                                           |

| Operations Manual                             | EK-T8030-OP                               |

| Site Preparation Guide                        | EK-T8030-SP                               |

| AlphaServer 8200 Installation Guide           | EK-T8230-IN                               |

| AlphaServer 8400 Installation Guide           | EK-T8430-IN                               |

| Service Information Kit                       | QZ-00RAC-GC                               |

| Service Manual (hard copy)                    | EK-T8030-SV                               |

| <i>Service Manual</i> (diskettes)             | AK–QKNFA–CA<br>AK–QUW7A–CA<br>AK–QUW6A–CA |

| Reference Manuals                             |                                           |

| System Technical Manual                       | EK-T8030-TM                               |

| System Technical Manual Supplement: CPU       | EK-T8030-TS                               |

| System Technical Manual Supplement: Memory    | EK-MS7CC-TS                               |

| DWLPA/DWLPB PCI Adapter Technical Manual      | EK-DWLPX-TM                               |

| Upgrade Manuals for Both Systems              |                                           |

| KN7CC CPU Installation Card                   | EK-KN7CC-IN                               |

| KN7CD CPU Installation Card                   | EK-KN7CD-IN                               |

| KN7CE CPU Installation Card                   | EK-KN7CE-IN                               |

| MS7CC Memory Installation Card                | EK-MS7CC-IN                               |

| KFTHA System I/O Module Installation Card     | EK-KFTHA-IN                               |

| KFTIA Integrated I/O Module Installation Card | EK-KFTIA-IN                               |

| Title                                           | Order Number |

|-------------------------------------------------|--------------|

| Upgrade Manuals: 8400 System Only               |              |

| AlphaServer 8400 Upgrade Manual                 | EK-T8430-UI  |

| BA654 DSSI Disk PIU Installation Guide          | EK-BA654-IN  |

| BA655 SCSI Disk and Tape PIU Installation Guide | EK-BA655-IN  |

| DWLAA Futurebus+ PIU Installation Guide         | EK-DWLAA-IN  |

| DWLMA XMI PIU Installation Guide                | EK-DWLMA-IN  |

| DWLPA/DWLPB PCI PIU Installation Guide          | EK-DWL84-IN  |

| H7237 Battery PIU Installation Guide            | EK-H7237-IN  |

| H7263 Power Regulator Installation Card         | EK-H7263-IN  |

| KFMSB Adapter Installation Guide                | EK-KFMSB-IN  |

| KZMSA Adapter Installation Guide                | EK-KXMSX-IN  |

| RRDCD Installation Guide                        | EK-RRDRX-IN  |

| Upgrade Manuals: 8200 System Only               |              |

| DWLPA/DWLPB PCI Shelf Installation Guide        | EK-DWL82-IN  |

| H7266 Power Regulator Installation Card         | EK-H7266-IN  |

| H7267 Battery Backup Installation Card          | EK-H7267-IN  |

Table 1 DIGITAL AlphaServer 8200 and 8400 Documentation (Continued)

### Table 2 Related Documents

| Title                                                                                | Order Number |

|--------------------------------------------------------------------------------------|--------------|

| General Site Preparation                                                             |              |

| Site Environmental Preparation Guide                                                 | EK-CSEPG-MA  |

| System I/O Options                                                                   |              |

| BA350 Modular Storage Shelf Subsystem<br>Configuration Guide                         | EK-BA350-CG  |

| BA350 Modular Storage Shelf Subsystem<br>User's Guide                                | EK-BA350-UG  |

| BA350-LA Modular Storage Shelf User's Guide                                          | EK-350LA-UG  |

| CIXCD Interface User Guide                                                           | EK-CIXCD-UG  |

| DEC FDDIcontroller 400 Installation/Problem Solving                                  | EK-DEMFA-IP  |

| DEC FDDIcontroller/Futurebus+ Installation Guide                                     | EK-DEFAA-IN  |

| DEC FDDIcontroller/PCI User Information                                              | EK-DEFPA-IN  |

| DEC LANcontroller 400 Installation Guide                                             | EK-DEMNA-IN  |

| DSSI VAXcluster Installation/Troubleshooting Manual                                  | EK-410AA-MG  |

| EtherWORKS Turbo PCI User Information                                                | EK-DE435-OM  |

| KZPSA PCI-to-SCSI Storage Adapter User's Guide                                       | EK-KZPSA-UG  |

| RF Series Integrated Storage Element User Guide                                      | EK-RF72D-UG  |

| StorageWorks RAID Array 200 Subsystem Family<br>Installation and Configuration Guide | EK-SWRA2-IG  |

| Architecture Reference Manual                                                        |              |

| Alpha Architecture Reference Manual                                                  | EY-L520E-DP  |

| MEMORY CHANNEL Manuals                                                               |              |

| Memory Channel User's Guide                                                          | EK-PCIRM-UG  |

| Memory Channel Service Information                                                   | EK-PCIRM-SV  |

# Chapter 1

# Introduction

The MS7CC-GA is a single-capacity memory module that provides 4 gigabytes of dynamic random access memory (DRAM) to the CPU. A subsystem can be configured on an AlphaServer 8400 with a maximum of seven MS7CC-GA modules providing a total memory capacity of 28 Gbytes.

### 1.1 Features

The MS7CC-GA memory modules feature the following:

- 4 Gbytes of memory capacity divided across four separate banks. Each bank is 1 Gbyte in size.

- 1 Gbit SIMM based on 16-Mbit deep x 4-bit wide DRAM components

- Incremental configuration to a maximum of seven modules implemented on extended-hex +1" size boards in a dual-processor AlphaServer 8400 system

- Up to 16-way interleaving of memory banks

- 64-byte block transfers, executed in two 32-byte transfers over two contiguous data cycles

- Read and write data wrapping on 32-byte naturally aligned boundaries

- Quadword ECC protection that allows single-bit error detection and correction, and double-bit error detection.

The MS7CC-GA modules can coexist in the same system with all other TLSB compatible memory modules. They run synchronously with the TLSB, so that no additional synchronization logic or clocks are required.

Memory modules are responders only. Memory transactions are initiated by commanders (CPUs or I/O nodes) on the command/address bus. Memory data transfers are initiated over a separate 256-bit data bus. All transactions on the data bus are retired in the order in which they were received on the command/address bus.

TLSB systems can support a maximum of 16 memory banks. Seven MS7CC-GA memory modules, however, may have up to 28 separate memory banks. This would make it impossible to build a maximally configured memory system with MS7CC-GA memory modules.

This architectural constraint is resolved with the implementation of a configuration mode that allows two memory banks to be configured as one bank. In this configuration mode, each MS7CC-GA has two memory banks, 2 gigabytes per bank. This mode allows one the maximum configuration of seven memory modules (16 memory banks, with one module having four banks) to be installed on a single TLSB.

During memory writes, TLSB memory modules store write data and ECC check bits as they are received off the TLSB. A minor modification of the ECC check bits is done before they are written to the DRAMs to allow for the addition of a row parity bit and a column parity bit to provide additional data integrity protection. During memory reads, memory modules strip off the encoded Row/Col parity bits from the ECC check bits prior to asserting the read data and check bits onto the TLSB.

### 1.2 Major Sections

A TLSB memory module consists of three major sections:

- Control address interface (CTL4)

- Memory data interface (MDI4)

- DRAM arrays

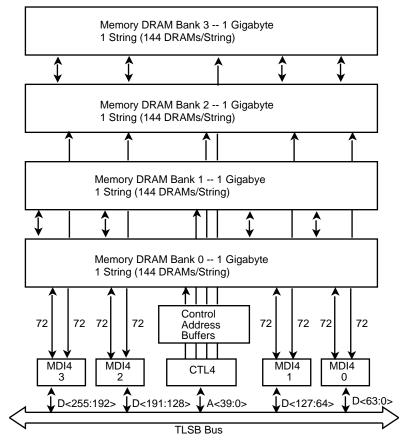

The major sections communicate with each other through internal buses. Figure 1-1 shows a block diagram of the MS7CC-GA memory module.

#### Figure 1-1 MS7CC-GA Memory Module Block Diagram

BXB0858.AI

### 1.2.1 Control Address Interface

The control address interface (CTL4) is a single gate array. It provides the interface to the TLSB, controls DRAM timing and refresh, runs memory self-test, and contains some of the TLSB and memory-specific registers.

CTL4 decodes the TLSB command and memory bank in the case of memory reads and writes, or the TLSB address during CSR operations to determine if it is selected for this transaction. In addition, command/address parity is checked to determine if a command/address parity error has occurred.

CTL4 contains the TLSB control sequencers responsible for the TLSB protocol.

CTL4 provides separate copies of Row/Column address, RAS, CAS, and WE signals for each of the four DRAM banks.

CTL4 controls the operation of the serial EEPROM on the memory module. The EEPROM contains the following information:

- The serial number of the module. This is entered into the EEPROM by manufacturing during module build.

- The module revision. This is entered into the EEPROM by manufacturing during module build. It is updated, as appropriate, anytime the module's revision changes.

- Self-test failures. If self-test fails, the console logs self-test failure data in the EEPROM.

- Memory module error logging data. This information is used to help diagnose and isolate failures on modules returned to a repair depot.

CTL4 interfaces to the TLSB command/address bus, which is independent from the data bus.

Internally, CTL4 consists of the following major functional areas:

- TLSB interface logic—command/address decode

- DRAM address generation logic for memory banks 0 through 3

- DRAM control signal timing logic for memory banks 0 through 3

- DRAM refresh control logic for memory banks 0 through 3

- CSRs

- Self-test address generation logic

- TLSB state machine control logic

- EEPROM control logic

- Control interface to the four MDI4 ASICs

### 1.2.2 Memory Data Interface

Each memory module has four memory data interface (MDI4) ASICs. Each MDI4 has a 72-bit interface to the TLSB and two 72-bit data interfaces to the DRAM arrays. The MDI4 includes data buffers, ECC checking logic, self-test data generation and checking logic, and CSRs. MDI4 forwards two 72-bit TLSB transfers to the DRAMs during memory writes. During memory reads, two 72-bit transfers from the DRAMs are issued onto the TLSB.

For memory writes, each MDI4 contains four 144-bit write data buffers that are used to:

- Temporarily store the first data cycle (72 bits) from the TLSB until the second arrives and the write can be completed.

- Store all 144 bits, so that write data can be accepted off the TLSB independent of refresh or read operations to the other three banks, which may result in delaying the completion of the write from the memory's perspective.

For memory reads, each MDI4 contains four separate read buffers, one for each memory bank. Each read buffer can store 144 bits of read data. The read buffers perform several functions:

- Temporarily store the second TLSB data cycle for each memory bank, while the first is being output onto the TLSB bus.

- Store either one through four banks worth of read data, which is necessary if TLSB\_HOLD is asserted, or if TLSB is very busy. Once RAS is asserted, the transaction MUST be completed.

- Contain "data-muxing" used to select between memory "fast-path" data, read buffer data, or CSR read data.

MDI4 contains the ECC checking logic that is used to check memory write data and memory read data to aid in system fault isolation. The ECC check bits are slightly modified before that data is written into the DRAMs by the addition of a Row and a Column parity bit. The purpose is to boost system data integrity in case of a single-bit Row or Column address failure. During memory reads, the modified ECC check bits are stripped of the Row/Column parity bits before data and check bits are driven onto the TLSB.

### 1.2.3 DRAM Arrays

The DRAM arrays consist of DRAMs, control signal, and address buffer components. The 4-Gbyte MS7CC-GA DRAM arrays are organized into four strings. Each string requires 144 DRAMs and is equivalent to one bank. The four 1-Gbyte banks are independently accessible. The MS7CC-GA memory modules use 16-Mbit deep x 4-bit wide DRAMs that are protected by a single-error correct, double-error detect quadword ECC code.

### 1.3 Memory Organization

The physical memory composed of a single or multiple memory modules can be organized in various ways to optimize memory access.

Memory can be configured with any mix of modules ranging in capacity from 128 Mbytes to the 4-Gbyte MS7CC-GA. The only restriction is that the total number of memory banks cannot exceed 16. Note that except for the MS7CC-GA, which has four memory banks but can be made to operate in a two-bank mode through a selection in the TLCNR register, all other memory modules have two banks of DRAM arrays. Table 1-1 lists the TLSB memory modules of various capacities.

### Table 1-1 Memory Array Capacity

| DRAM Type<br>(Mbits) | Number of<br>Strings | Memory Capacity<br>(Mbytes) |

|----------------------|----------------------|-----------------------------|

| 4x1                  | 2                    | 128 (MS7CC-BA)              |

| 4x1                  | 4                    | 256 (MS7CC-CA)              |

| 4x1                  | 8                    | 512 (MS7CC-DA)              |

| 4x4                  | 4                    | 1024 (MS7CC-EA)             |

| 4x4                  | 8                    | 2048 (MS7CC-FA)             |

| 16x4                 | 4                    | 4096 (MS7CC-GA)             |

### 1.4 Memory Interleave

Memory performance is improved by interleaving the physical memory. Interleaving can be done at two levels: module and system.

MS7CC-GA memory modules support 4-way interleaving.

A memory configuration on the TLSB consisting of 16 memory banks across '*n*' number of memory modules supports a maximum of 16-way interleaving.

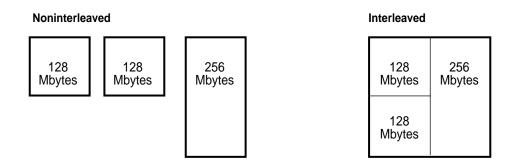

Memory modules of different capacities can be interleaved as a set with modules of another capacity. For example, two 128-Mbyte modules can be interleaved with a single 256-Mbyte module as one set that is 4-way interleaved. This type of configuration yields 2-way module interleaving and 4way system-level interleaving as shown in Figure 1-2. This same set can also be interleaved into a "pseudo 8-way" interleave set that will further boost system performance.

*NOTE:* For such a memory module set, the console configures memory to the "pseudo 8-way" interleave.

### Figure 1-2 Interleaving Different Size Memory Modules

BXB-0389A-92

Interleaving of memory modules is set up by initialization software through mapping registers in TLSB commanders and in each memory module. When memory modules are interleaved, each interleaved set is addressed on a 64-byte block boundary. In multiple interleaved modules, each consecutive 64-byte address targets the next memory module in the interleaved set. This is done because accessing multiple banks in one memory module can result in reduced system throughput due to common data path contention between the two banks.

### 1.5 Refresh

Each module implements CBR (CAS Before Ras) DRAM refresh. All memory modules refresh at the same time providing that a module is not servicing a TLSB memory transaction at the time when a refresh is requested. If a refresh request is asserted after a TLSB transaction has begun in a given memory bank, the TLSB transaction is completed and is followed immediately by the refresh operation.

In addition to refresh cycles during normal system operation, the MS7CC-GA refresh is initiated under power-up and system reset. Upon the deassertion of TLSB\_RESET, the MS7CC-GA module initiates a start-up procedure that consists of:

- At least eight DRAM refresh cycles to initialize the DRAMS.

- All CSRs and required internal logic are set to a known initialized state.

- Self-test is initiated and run to completion.

# Chapter 2

# Registers

The MS7CC-GA registers are divided into two main groups:

- TLSB required registers

- Memory-specific registers

TLSB required registers are used for internode communications and transactions over the TLSB bus. Memory-specific registers implement functions related to the operation of the module.

All registers are located in node spaces and are accessed using CSR read or write commands. Nodes respond to all addresses within the node space. If a read is performed to a valid node, but to a CSR that is not implemented, the return data is Unpredictable.

### 2.1 Register Conventions

Certain conventions are followed in register descriptions and in references to bits and bit fields:

- Registers are referred to by their mnemonics, such as **TLCNR register.** The full name of a register (for example, **Memory Configuration Register**) is spelled out only at the top of the register description page, or when the register is first introduced.

- Bits and fields are enclosed in angle brackets. For example, **bit** <**31**> and **bits** <**31:16**>. For clarity of reference, bits are usually specified by their numbers or names enclosed in angle brackets adjacent to the register mnemonic, such as **TLBER**<**16**> or **TLBER**<**UDE**>, which are equivalent designations.

- When the value of a bit position is given explicitly in a register diagram, the information conveyed is as follows:

| Bit Value<br>Designation | Meaning                                                                                           |

|--------------------------|---------------------------------------------------------------------------------------------------|

| 0                        | Reads as zero; ignored on writes.                                                                 |

| 1                        | Reads as one; ignored on writes.                                                                  |

| Х                        | Does not exist in hardware. The value of the bit is Unpredictable on reads and ignored on writes. |

- The entry in the **type** column of a register description table may include the initialization value of the bits. For example, entry "R/W, 0" indicates a read/write bit that is initialized to 0.

- Acronyms are used throughout register descriptions to indicate the access type of the bit(s) as follows:

| Acronym | Access Type                                                           |

|---------|-----------------------------------------------------------------------|

| R       | Read only; writes ignored.                                            |

| R0      | Read as zero.                                                         |

| R/W     | Read/write.                                                           |

| U       | Undefined                                                             |

| W       | Write only.                                                           |

| W1C     | Read/write one to clear; unaltered by a write of zero.                |

| W1S     | Write one to set; self-cleared; cannot be cleared by a write of zero. |

### 2.2 Register Address Mapping

CSRs are mapped to a node space as offsets from a base address that is assigned to the node (slot on the TLSB backplane). The base address is implemented in hardware and depends on the node ID of the module, which is determined by the TLSB slot occupied by the module.

Table 2-1 gives the physical base addresses of nodes on the TLSB bus. Some registers are mapped to the broadcast space. The broadcast space base address (BSB) is common to all nodes and is FF 8E00 0000.

Table 2-1 TLSB Node Space Base Addresses

| Node            | Module           | Physical Base Address (BB)<br>Address Field <39:0><br>34-Bit Range |

|-----------------|------------------|--------------------------------------------------------------------|

| 0               | CPU, Memory      | FF 8800 0000                                                       |

| 1               | CPU, Memory      | FF 8840 0000                                                       |

| 2               | CPU, Memory      | FF 8880 0000                                                       |

| 3               | CPU, Memory      | FF 88C0 0000                                                       |

| 4               | CPU, Memory, I/O | FF 8900 0000                                                       |

| 5               | CPU, Memory, I/O | FF 8940 0000                                                       |

| 6               | CPU, Memory, I/O | FF 8980 0000                                                       |

| 7               | CPU, Memory, I/O | FF 89C0 0000                                                       |

| 8               | I/O              | FF 8A00 0000                                                       |

| Broadcast Space |                  | FF 8E00 0000                                                       |

### 2.3 TLSB Required Registers Implemented by Memory

Table 2-2 lists the TLSB registers implemented by memory. TLSB required CSR space spans a range of BB+0000–BB+0FC0.

### Table 2-2 TLSB Required Memory Registers

| Mnemonic | Name                            | Address        | Implemented by |

|----------|---------------------------------|----------------|----------------|

| TLDEV    | Device Register                 | BB+0000        | CTL4           |

| TLBER    | Bus Error Register              | <b>BB+0040</b> | CTL4           |

| TLCNR    | Configuration Register          | <b>BB+0080</b> | CTL4           |

| TLVID    | Virtual ID Register             | BB+00C0        | CTL4           |

| TLFADR0  | TLSB Failing Address Register 0 | <b>BB+0600</b> | CTL4           |

| TLFADR1  | TLSB Failing Address Register 1 | <b>BB+0640</b> | CTL4           |

| TLESR0   | TLSB Error Syndrome Register 0  | <b>BB+0680</b> | MDI4_0         |

| TLESR1   | TLSB Error Syndrome Register 1  | BB+06C0        | MDI4_1         |

| TLESR2   | TLSB Error Syndrome Register 2  | <b>BB+0700</b> | MDI4_2         |

| TLESR3   | TLSB Error Syndrome Register 3  | BB+0740        | MDI4_3         |

### 2.4 Memory-Specific Registers

Table 2-3 lists the memory-specific registers. Memory-specific CSR space is reserved as follows:

- In CTL4: from BB+01800 to BB+0FFC0

- In MDI4\_0: from BB+10000 to BB+13FC0

- In MDI4\_1: from BB+14000 to BB+17FC0

- In MDI4\_2: from BB+18000 to BB+1BFC0

- In MDI4\_3: from BB+1C000 to BB+1FFC0

| Mnemonic                             | Register Name                                                       | Address<br>(Byte Offset) |

|--------------------------------------|---------------------------------------------------------------------|--------------------------|

| <b>Registers in CTL4</b>             |                                                                     |                          |

| SECR                                 | Serial EEPROM Control/Data Register                                 | $BB^{1} + 01800$         |

| MIR                                  | Memory Interleave Register                                          | BB + 01840               |

| MCR                                  | Memory Configuration Register                                       | BB + 01880               |

| MCR                                  | Memory Configuration Register                                       | $BSB^{2} + 01880$        |

| STAIR                                | Self-Test Address Isolation Register                                | BB + 018C0               |

| STER                                 | Self-Test Error Register                                            | BB + 01900               |

| MDRA                                 | Memory Diagnostic Register A                                        | BB + 01980               |

| MDRB                                 | Memory Diagnostic Register B                                        | BB + 019C0               |

| Registers in MDI4                    | _0                                                                  |                          |

| STDERA_0                             | Self-Test Data Error Register A_0                                   | <b>BB</b> + 10000        |

| STDERB_0                             | Self-Test Data Error Register B_0                                   | BB + 10040               |

| STDERC_0                             | Self-Test Data Error Register C_0                                   | BB + 10080               |

| STDERD_0                             | Self-Test Data Error Register D_0                                   | BB + 100C0               |

| STDERE_0                             | Self-Test Data Error Register E_0                                   | BB + 10100               |

| DDR0                                 | Data Diagnostic Register 0                                          | BB + 10140               |

| Registers in MDI4                    | _1                                                                  |                          |

| STDERA_1                             | Self-Test Data Error Register A_1                                   | BB + 14000               |

| STDERA_1<br>STDERB_1                 | Self-Test Data Error Register B_1                                   | BB + 14000<br>BB + 14040 |

| STDERC_1                             | Self-Test Data Error Register C_1                                   | BB + 14040<br>BB + 14080 |

| STDERC_1<br>STDERD_1                 | Self-Test Data Error Register D_1                                   | BB + 14080<br>BB + 140C0 |

| STDERE_1                             | Self-Test Data Error Register E_1                                   | BB + 14000<br>BB + 14100 |

| DDR1                                 | Data Diagnostic Register 1                                          | BB + 14100<br>BB + 14140 |

| <b>Registers in MDI4</b>             | 2                                                                   |                          |

| -                                    |                                                                     | DD 10000                 |

| STDERA_2                             | Self-Test Data Error Register A_2                                   | BB + 18000               |

| STDERB_2                             | Self-Test Data Error Register B_2                                   | BB + 18040               |

| STDERC_2                             | Self-Test Data Error Register C_2                                   | BB + 18080               |

| STDERD_2                             | Self-Test Data Error Register D_2                                   | BB + 180C0               |

| STDERE_2<br>DDR2                     | Self-Test Data Error Register E_2<br>Data Diagnostic Register 2     | BB + 18100<br>BB + 18140 |

| Registers in MDI4                    |                                                                     |                          |

| -                                    |                                                                     | DD + 1C000               |

| STDERA_3                             | Self-Test Data Error Register A_3                                   | BB + 1C000               |

| STDERB_3                             | Self-Test Data Error Register B_3                                   | BB + 1C040               |

| STDERC_3                             | Self-Test Data Error Register C_3                                   | BB + 1C080               |

| STDERD_3                             | Self-Test Data Error Register D_3                                   | BB + 1C0C0               |

| STDERE_3                             | Self-Test Data Error Register E_3                                   | BB + 1C100               |

| DDR3                                 | Data Diagnostic Register 3                                          | BB + 1C140               |

| <sup>1</sup> BB is the node space ba | ise address of the memory module in hex.                            |                          |

| <sup>2</sup> BSB is the broadcast sr | pace base address, which is FF 8E00 0000. This register is write or | nly.                     |

## Table 2-3 Memory-Specific Registers

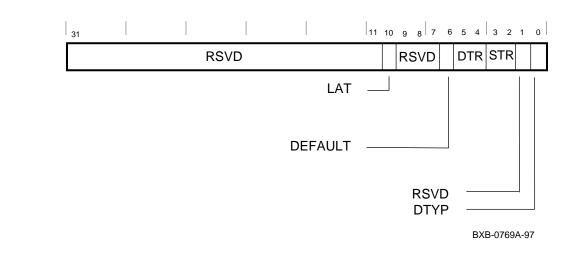

# **TLDEV—Device Register**

| Address | BB + 0000 |

|---------|-----------|

| Access  | R/W       |

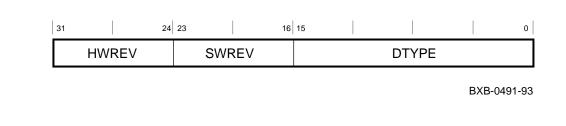

The TLDEV register is loaded during initialization with information that identifies a node. A zero value indicates an uninitialized node.

### Table 2-4 TLDEV Register Bit Definitions

| Name  | Bit(s)  | Туре   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HWREV | <31:24> | R/W, 0 | <b>Hardware Revision.</b> Identifies the hardware revision level of a TLSB node. The value will be loaded by console firmware from information contained in the serial EEPROM. Bits <31:28> specify a major revision number and bits <27:24> specify a minor revision number to be displayed by the console in the format 0.0 through 15.15.                                                                                                     |

| SWREV | <23:16> | R/W, 0 | <b>Software Revision.</b> Identifies the software (or firmware) revision level of a TLSB node. The value will be loaded by console firmware from information contained in the serial EEPROM. Bits <23:20> specify a major revision number and bits <19:16> specify a minor revision number to be displayed by the console in the format 0.0 through 15.15. These bits shall be zero if a software revision level is not applicable to this node. |

| DTYPE | <15:0>  | R/W, 0 | <b>Device Type.</b> Identifies the type of node.<br>Memory hardware loads a value of 5800 (hex)<br>into this field upon power-up or reset.                                                                                                                                                                                                                                                                                                       |

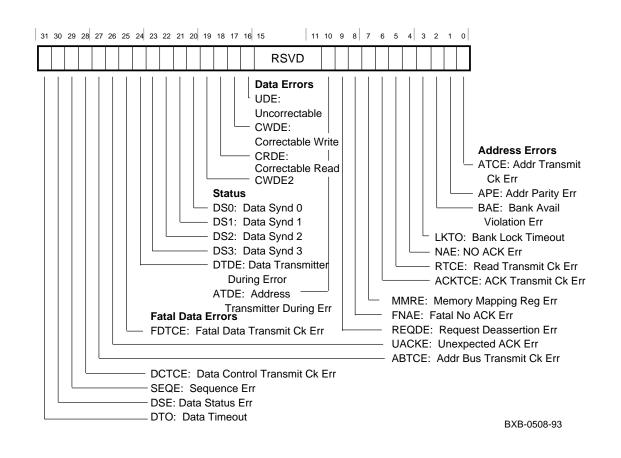

## **TLBER—Bus Error Register**

AddressBB + 0040AccessR/W

The TLBER register contains bits that are set when a TLSB node detects errors in the TLSB system. The entire register is locked when the first error bit gets set in this register if TLCNR<LOFE> is set. All bits except the four DSn bits cause the register to be locked. When the register is locked, no bits change value until all bits are cleared by software or TLCNR<LOFE> is cleared. Locking the register is intended only for diagnostics. Not intended for use in normal operation.

| Name  | Bit(s) | Туре   | Function                                                                                                                                                                                                                                                                        |

|-------|--------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DTO   | <31>   | W1C, 0 | Data Timeout.                                                                                                                                                                                                                                                                   |

|       |        |        | Memory: Not implemented.                                                                                                                                                                                                                                                        |

| DSE   | <30>   | W1C, 0 | <b>Data Status Error.</b> Set when<br>TLSB_STATCHK does not match the logical OR<br>of TLSB_SHARED and TLSB_DIRTY. This is a<br>system fatal error that asserts TLSB_FAULT.                                                                                                     |

| SEQE  | <29>   | W1C, 0 | <b>Sequence Error.</b> Set when an unexpected value of TLSB_SEQ<3:0> is received. This is a system fatal error that asserts TLSB_FAULT.                                                                                                                                         |

| DCTCE | <28>   | W1C, 0 | <b>Data Control Transmit Check Error.</b> Set<br>when a transmit check error is detected on<br>TLSB_SEND_DATA, TLSB_SEQ<3:0>,<br>TLSB_SHARED, TLSB_DIRTY, TLSB_HOLD,<br>TLSB_STATCHK, or TLSB_DATA_ERROR sig-<br>nals. This is a system fatal error that asserts<br>TLSB_FAULT. |

| ABTCE | <27>   | W1C, 0 | <b>Address Bus Transmit Check Error.</b> Set<br>when a transmit check error is detected on<br>TLSB_ARB_SUP, TLSB_LOCKOUT, or<br>TLSB_BANK_AVL<15:0> signals. This is a sys-<br>tem fatal error that asserts TLSB_FAULT.                                                         |

| UACKE | <26>   | W1C, 0 | <b>Unexpected Acknowledge.</b> Set if a node receives unexpected TLSB_CMD_ACK. This is a system fatal error that asserts TLSB_FAULT.                                                                                                                                            |

| FDTCE | <25>   | W1C, 0 | <b>Fatal Data Transmit Check Error.</b> Set when<br>a node detects a data transmit check error and<br>does NOT detect any ECC error. This is a sys-<br>tem fatal error that asserts TLSB_FAULT.                                                                                 |

| DTDE  | <24>   | W1C, 0 | <b>Data Transmitter During Error.</b> A status bit<br>set on receipt of TLSB_DATA_ERROR if node<br>was the transmitter of the data during data bus<br>transaction.                                                                                                              |

| DS3   | <23>   | R, U   | <b>Data Syndrome 3.</b> A status bit set when the TLESR3 register contains status relative to the current data error. This bit is undefined when CRDE, CWDE, and UDE are zero. It is overwritten on a second error of higher significance.                                      |

## Table 2-5 TLBER Register Bit Definitions

| Name  | Bit(s)  | Туре   | Function                                                                                                                                                                                                                                   |

|-------|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DS2   | <22>    | R, U   | <b>Data Syndrome 2.</b> A status bit set when the TLESR2 register contains status relative to the current data error. This bit is undefined when CRDE, CWDE, and UDE are zero. It is overwritten on a second error of higher significance. |

| DS1   | <21>    | R, U   | <b>Data Syndrome 1.</b> A status bit set when the TLESR1 register contains status relative to the current data error. This bit is undefined when CRDE, CWDE, and UDE are zero. It is overwritten on a second error of higher significance. |

| DS0   | <20>    | R, U   | <b>Data Syndrome 0.</b> A status bit set when the TLESR0 register contains status relative to the current data error. This bit is undefined when CRDE, CWDE, and UDE are zero. It is overwritten on a second error of higher significance. |

| CWDE2 | <19>    | W1C, 0 | <b>Second Correctable Write Data Error.</b> Set<br>when a second CWDE error is received when<br><cwde> is still set from the first error.</cwde>                                                                                           |

| CRDE  | <18>    | W1C, 0 | <b>Correctable Read Data Error.</b> Set when a CRECC error is set in any TLESRn register. This is a soft error that asserts TLSB_DATA_ERROR if CRDD is not set in the TLCNR register.                                                      |

| CWDE  | <17>    | W1C, 0 | <b>Correctable Write Data Error.</b> Set when a CWECC error is set in any TLESRn register. This is a soft error that asserts TLSB_DATA_ERROR if CWDD is not set in the TLCNR register.                                                     |

| UDE   | <16>    | W1C, 0 | <b>Uncorrectable Data Error.</b> Set when <uecc> is set in any TLESRn register. This is a hard error that asserts TLSB_DATA_ ERROR.</uecc>                                                                                                 |

| RSVD  | <15:11> | R0     | <b>Reserved.</b> Read as zero.                                                                                                                                                                                                             |

| ATDE  | <10>    | W1C, 0 | Address Transmitter During Error.                                                                                                                                                                                                          |

|       |         |        | Memory: Not implemented.                                                                                                                                                                                                                   |

| REQDE | <9>     | W1C, 0 | <b>Request Deassertion Error.</b>                                                                                                                                                                                                          |

|       |         |        | Memory: Not implemented.                                                                                                                                                                                                                   |

## Table 2-5 TLBER Register Bit Definitions (Continued)

| Name   | Bit(s) | Туре   | Function                                                                                                                                                                                                                                                                                                                                                    |

|--------|--------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FNAE   | <8>    | W1C, 0 | Fatal No Acknowledge Error.                                                                                                                                                                                                                                                                                                                                 |

|        |        |        | Memory: Not implemented.                                                                                                                                                                                                                                                                                                                                    |

| MMRE   | <7>    | W1C, 0 | Memory Mapping Register Error.                                                                                                                                                                                                                                                                                                                              |

|        |        |        | Memory: Not implemented.                                                                                                                                                                                                                                                                                                                                    |

| ACKTCE | <6>    | W1C, 0 | <b>Acknowledge Transmit Check Error.</b> Set<br>when a transmit check error is detected on the<br>TLSB_CMD_ACK signal. This is a system fatal<br>error that asserts TLSB_FAULT.                                                                                                                                                                             |

| RTCE   | <5>    | W1C, 0 | Request Transmit Check Error.                                                                                                                                                                                                                                                                                                                               |

|        |        |        | Memory: Not implemented.                                                                                                                                                                                                                                                                                                                                    |

| NAE    | <4>    | W1C, 0 | No Acknowledge Error.                                                                                                                                                                                                                                                                                                                                       |

|        |        |        | Memory: Not implemented.                                                                                                                                                                                                                                                                                                                                    |

| LKTO   | <3>    | W1C, 0 | <b>Bank Lock Timeout.</b> Set when a memory node<br>times out waiting for a Write Bank Unlock com-<br>mand after processing a Read Bank Lock com-<br>mand. This is a hard error. The memory node<br>asserts TLSB_BANK_AVL upon setting<br><lkto>. This error is disabled if LKTOD is set<br/>in the TLCNR register.</lkto>                                  |

| BAE    | <2>    | W1C, 0 | <b>Bank Available Violation Error.</b> Set when a<br>memory bank is addressed by a memory access<br>command while the memory bank is busy and<br>has a TLSB_BANK_AVL signal asserted. Also<br>set when any node detects a CSR access com-<br>mand while a CSR command is already in pro-<br>gress. This is a system fatal error that asserts<br>TLSB_FAULT. |

| APE    | <1>    | W1C, 0 | <b>Address Parity Error.</b> Set when a node detects even parity on the TLSB_ADR<30:5> and TLSB_ADR_PAR signals, or on the TLSB_ADR<39:31>, TLSB_ADR<4:3>, TLSB_BANK_NUM<3:0>, TLSB_CMD<2:0>, and TLSB_CMD_PAR signals. This is a system fatal error that asserts TLSB_FAULT.                                                                               |

| ATCE   | <0>    | W1C, 0 | Address Transmit Check Error.                                                                                                                                                                                                                                                                                                                               |

|        |        |        | Memory: Not implemented.                                                                                                                                                                                                                                                                                                                                    |

## Table 2-5 TLBER Register Bit Definitions (Continued)

# **TLCNR—Configuration Register**

AddressBB + 0080AccessR/W

The TLCNR register contains the TLSB system configuration setup and status information. Node-specific configuration information exists in node-specific registers.

| Name  | Bit(s)  | Туре   | Function                                                                                                                                                                                                                                                                                                                                                       |

|-------|---------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LOFE  | <31>    | R/W, 0 | <b>Lock on First Error.</b> If set, the node locks the TLBER and TLFADR registers when the first error bit is set in the TLBER register.                                                                                                                                                                                                                       |

| NRST  | <30>    | W, 0   | <b>Node Reset.</b> When set, CSRs are reset to their initial states. Any transactions pending may be lost or left incomplete. Memory self-test halts if running and does NOT restart. An internally generated reset signal remains asserted for 32 TLSB bus cycles, which is sufficient to reset memory state and clear <nrst>.</nrst>                         |

| RSVD  | <29:20> | R0     | <b>Reserved.</b> Read as zero.                                                                                                                                                                                                                                                                                                                                 |

| RSVD  | <19:16> | R1     | <b>Reserved.</b> Read as ones.                                                                                                                                                                                                                                                                                                                                 |

| STF_D | <15>    | R/W, 1 | <b>Self-Test Fail D.</b> When set, indicates that<br>memory has not yet completed self-test. Memory<br>clears this bit if self-test executes to completion<br><b>regardless of whether errors were found</b><br><b>within the DRAM array.</b> When this bit is<br>clear, the self-test LED will be lit, indicating<br>that the module completed the self-test. |

| STF_C | <14>    | R/W, 1 | <b>Self-Test Fail C.</b> When set, indicates that<br>memory has not yet completed self-test. Memory<br>clears this bit if self-test executes to completion<br><b>regardless of whether errors were found</b><br><b>within the DRAM array.</b> When this bit is<br>clear, the self-test LED will be lit, indicating<br>that the module completed the self-test. |

| STF_B | <13>    | R/W, 1 | <b>Self-Test Fail B.</b> When set, indicates that<br>memory has not yet completed self-test. Memory<br>clears this bit if self-test executes to completion<br><b>regardless of whether errors were found</b><br><b>within the DRAM array.</b> When this bit is<br>clear, the self-test LED will be lit, indicating<br>that the module completed the self-test. |

| STF_A | <12>    | R/W, 1 | <b>Self-Test Fail A.</b> When set, indicates that<br>memory has not yet completed self-test. Memory<br>clears this bit if self-test executes to completion<br><b>regardless of whether errors were found</b><br><b>within the DRAM array.</b> When this bit is<br>clear, the self-test LED will be lit, indicating<br>that the module completed the self-test. |

## Table 2-6 TLCNR Register Bit Definitions

| Name    | Bit(s) | Туре   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|--------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCNT    | <11:8> | R/W, 4 | <b>Virtual Unit Count.</b> This field indicates the number of memory banks for which the MC7CC-GA is configured:                                                                                                                                                                                                                                                                                                                                                                                                    |

|         |        |        | VCNT = 4 (4 memory banks, 1 Gbyte each)<br>VCNT = 2 (2 memory banks, 2 Gbytes each)                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         |        |        | The default mode is four memory banks, each one gigabyte in size (VCNT = 4).                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         |        |        | The TLSB can support a maximum of 16 mem-<br>ory banks. Seven MS7CC-GA memory modules,<br>however, may have up to 28 separate memory<br>banks. This would make it impossible to build a<br>maximally configured memory system with<br>MS7CC-GA memory modules. Writing a 2 hex<br>in this field configures the MS7CC-GA memory<br>module to two memory banks, each 2 Gbytes in<br>size. In this configuration a maximum of seven<br>MS7CC-GA memory modules (14 memory banks)<br>may be installed on a single TLSB. |

|         |        |        | The <vcnt> field should not be changed from<br/>the value set at system initialization when other<br/>bits in this register are modified.</vcnt>                                                                                                                                                                                                                                                                                                                                                                    |

| NODE_ID | <7:4>  | R, ID  | <b>Node ID.</b> This field reflects the physical node ID as presented to the node by TLSB_NID<2:0>.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RSVD    | <3>    | R0     | <b>Reserved.</b> Must be zero.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| LKTOD   | <2>    | R/W, 0 | <b>Bank Lock Timeout Disable.</b> When set, a<br>memory node disables the timeout counter wait-<br>ing for a Bank Unlock Write command after<br>processing a Read Bank Lock command. The<br><lkto> error bit in the TLBER register will not<br/>set.</lkto>                                                                                                                                                                                                                                                         |

| CRDD    | <1>    | R/W, 0 | <b>Correctable Read Data Error Interrupt Dis-<br/>able.</b> When set, TLSB_DATA_ERROR is not<br>asserted on detection of a single-bit data error<br>during a read command. Setting CRDD in all<br>nodes disables correctable read data error inter-<br>rupts.                                                                                                                                                                                                                                                       |

| CWDD    | <0>    | R/W, 0 | <b>Correctable Write Data Error Interrupt</b><br><b>Disable.</b> When set, TLSB_DATA_ERROR is not<br>asserted on detection of a single-bit data error<br>during a write command. Setting CWDD in all<br>nodes disables correctable write data error inter-<br>rupts.                                                                                                                                                                                                                                                |

Table 2-6 TLCNR Register Bit Definitions (Continued)

# **TLVID—Virtual ID Register**

| Address | BB + 00C0 |

|---------|-----------|

| Access  | R/W       |

The TLVID register contains the TLSB virtual identifiers assigned to a physical node. The virtual units can be CPUs or memory banks. The number of these units is presented in TLCNR<VCNT>. The units are addressed using virtual IDs that are assigned by writing the TLVID register.

CAUTION: This register must be loaded with a unique value for the virtual ID number of each memory bank, that is, no two of the VID\_D, VID\_C, VID\_B, and VID\_A fields are to be written with the same value. Otherwise, results of memory transactions will be unpredictable.

| 31 |      | 16 | 15 1  | 2 11 | 8   | 7 4   | 3 0   |

|----|------|----|-------|------|-----|-------|-------|

|    | RSVD |    | VID_D | VI   | D_C | VID_B | VID_A |

BXB-0493A-96

| Name  | Bit(s)  | Туре   | Function                                                                                                                                                                                                                                                                                                |

|-------|---------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RSVD  | <31:16> | R, 0   | <b>Reserved.</b> Read as zero.                                                                                                                                                                                                                                                                          |

| VID_D | <15:12> | R/W, 0 | <b>Virtual ID D.</b> <i>Memory:</i> Contains the virtual ID number for memory bank 3. Console loads this field at initialization time. The contents of this register are compared to TLSB_BANK_NUM <3:0> during a memory space command/address cycle to determine if bank 3 of this module is selected. |

|       |         |        | This field must have a value different from any other VID_X field.                                                                                                                                                                                                                                      |

| VID_C | <11:8>  | R/W, 0 | <b>Virtual ID C.</b> <i>Memory:</i> Contains the virtual ID number for memory bank 2. Console loads this field at initialization time. The contents of this register are compared to TLSB_BANK_NUM <3:0> during a memory space command/address cycle to determine if bank 1 of this module is selected. |

|       |         |        | This field must have a value different from any other VID_X field.                                                                                                                                                                                                                                      |

| VID_B | <7:4>   | R/W, 0 | <b>Virtual ID B.</b> <i>Memory:</i> Contains the virtual ID number for memory bank 1. Console loads this field at initialization time. The contents of this register are compared to TLSB_BANK_NUM <3:0> during a memory space command/address cycle to determine if bank 1 of this module is selected. |

|       |         |        | This field must have a value different from any other VID_X field.                                                                                                                                                                                                                                      |

| VID_A | <3:0>   | R/W, 0 | <b>Virtual ID A.</b> <i>Memory:</i> Contains the virtual ID number for memory bank 0. Console loads this field at initialization time. The contents of this register are compared to TLSB_BANK_NUM <3:0> during a memory space command/address cycle to determine if bank 0 of this module is selected. |

|       |         |        | This field must have a value different from any other VID_X field.                                                                                                                                                                                                                                      |

## Table 2-7 TLVID Register Bit Definitions

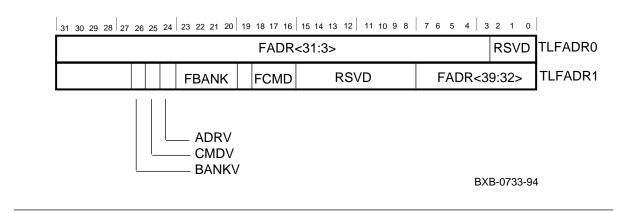

## **TLFADRn—Failing Address Registers**

| Address | BB + 0600, 0640 |

|---------|-----------------|

| Access  | R/W             |

The TLFADRn registers contain status information associated with an error condition. Some nodes may not preserve this information for all error types. Therefore, field valid bits are used to indicate which fields contain data.

### Table 2-8 TLFADRn Register Bit Definitions

| Name    | Bit(s)  | Туре   | Function                                                                                                                                            |

|---------|---------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| TLFADR0 |         |        |                                                                                                                                                     |

| FADR    | <31:3>  | R, U   | <b>Failing Address&lt;31:3</b> >. The address field from the command that resulted in an error. This field is Undefined when <adrv> is zero.</adrv> |

| RSVD    | <2:0>   | R0     | <b>Reserved.</b> Must be zero.                                                                                                                      |

| TLFADR1 |         |        |                                                                                                                                                     |

| RSVD    | <31:27> | R0     | <b>Reserved.</b> Must be zero.                                                                                                                      |

| BANKV   | <26>    | W1C, 0 | <b>Bank Valid.</b> Set when <fbank> contains a valid bank number from a bus transaction.</fbank>                                                    |

| CMDV    | <25>    | W1C, 0 | <b>Command Valid.</b> Set when <fcmd> contains a valid command code from a bus transaction.</fcmd>                                                  |

| Name    | Bit(s)  | Туре   | Function                                                                                                                                                                   |

|---------|---------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TLFADR1 |         |        |                                                                                                                                                                            |

| ADRV    | <24>    | W1C, 0 | <b>Address Valid.</b> Set when <fadr> contains a valid address from a bus transaction.</fadr>                                                                              |

| FBANK   | <23:20> | R, U   | <b>Failing Bank Number.</b> The bank number field from the command that resulted in an error. This field is Undefined when <bankv> is zero.</bankv>                        |

| RSVD    | <19>    | R0     | <b>Reserved.</b> Reads as zero.                                                                                                                                            |

| FCMD    | <18:16> | R, U   | <b>Failing Command Code.</b> The command code field from the command that resulted in an error. This field is Undefined when <cmdv> is zero.</cmdv>                        |

| RSVD    | <15:8>  | R0     | <b>Reserved.</b> Read as zero.                                                                                                                                             |

| FADR    | <7:0>   | R, U   | <b>Failing Address</b> < <b>39:32</b> >. The high-order address field bits from the command that resulted in an error. This field is Undefined when <adrv> is zero.</adrv> |

Table 2-8 TLFADRn Register Bit Definitions (Continued)

The TLFADRn registers are updated on the following conditions, listed in decreasing priority:

- 1. <APE>, <ATCE>, or TLBER<BAE> set in TLBER register

- 2. <UDE> sets in TLBER register

- 3. <CWDE> sets in TLBER register

- 4. <CRDE> sets in TLBER register

If any of the bits <ADRV>, <CMDV>, or <BANKV> are set, the registers are considered to be latched. A second occurrence of the same update condition does not overwrite latched status. However, latched status is overwritten if an update condition of higher priority occurs. The priority of each update condition is denoted by the number in the above list. A priority of 1 is the highest priority. When latched status is overwritten by a higher priority condition, all fields are updated, even if the update results in clearing <ADRV>, <CMDV>, or <BANKV>.

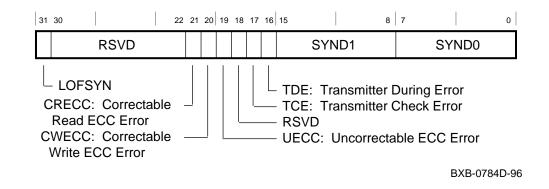

## **TLESRn—Error Syndrome Registers**

AddressBB + 0680 through 0740AccessR/W

The TLESRn registers contain the status information on a data error within a 64-bit slice of the data.

TLESR0 contains the error syndrome and status derived from TLSB\_D<63:0> and TLSB\_ECC<7:0>.

TLESR1 contains the error syndrome and status derived from TLSB\_D<127:64> and TLSB\_ECC<15:8>.

TLESR2 contains the error syndrome and status derived from TLSB\_D<191:128> and TLSB\_ECC<23:16>.

TLESR3 contains the error syndrome and status derived from TLSB\_D<255:192> and TLSB\_ECC<31:24>.

| Name   | Bit(s)  | Туре   | Function                                                                                                                                                                                                                                                             |

|--------|---------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LOFSYN | <31>    | R/W, 0 | <b>Lock on First Syndrome.</b> When set, the TLESR register locks on the first error.                                                                                                                                                                                |

| RSVD   | <30:22> | R0     | <b>Reserved.</b> Read as zero.                                                                                                                                                                                                                                       |

| CRECC  | <21>    | W1C, 0 | <b>Correctable Read ECC Error.</b> Set when an error occurs during a read command. This is a soft error.                                                                                                                                                             |

| CWECC  | <20>    | W1C, 0 | <b>Correctable Write ECC Error.</b> Set when an error occurs during a write command. This is a soft error.                                                                                                                                                           |

| UECC   | <19>    | W1C, 0 | <b>Uncorrectable ECC Error.</b> Set when an uncorrectable syndrome is detected, or if a correctable syndrome is detected on receipt of CSR data which the node is unable to correct. This is a hard error.                                                           |

| RSVD   | <18>    | R0     | <b>Reserved.</b> Reads as zero.                                                                                                                                                                                                                                      |

| TCE    | <17>    | W1C, 0 | <b>Transmit Check Error.</b> Set when a transmit<br>check error is detected on the TLSB_D or<br>TLSB_ECC signals covered by the TLESRn register.<br>This is a system fatal error if not accompanied by<br>another error in this register (CRECC, CWECC, or<br>UECC). |

| TDE    | <16>    | W1C, 0 | <b>Transmitter During Error.</b> A status bit set when data transmitted by a node results in error. This bit is Undefined when <crecc>, <cwecc>, and <uecc> are zero.</uecc></cwecc></crecc>                                                                         |

| SYND1  | <15:8>  | R, U   | <b>Syndrome 1.</b> Latched error syndrome from second data cycle. This field is Undefined when <crecc>, <cwecc>, and <uecc> are zero.</uecc></cwecc></crecc>                                                                                                         |

| SYND0  | <7:0>   | R, U   | <b>Syndrome 0.</b> Latched error syndrome from first data cycle. This field is Undefined when <crecc>, <cwecc>, and <uecc> are zero.</uecc></cwecc></crecc>                                                                                                          |

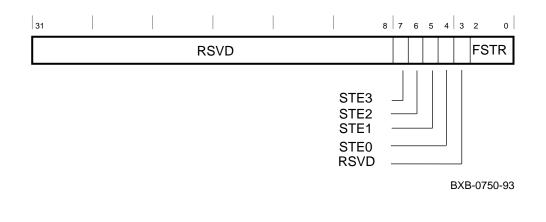

#### Table 2-9 TLESRn Register Bit Definitions

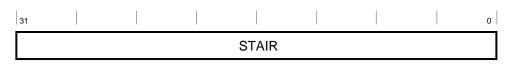

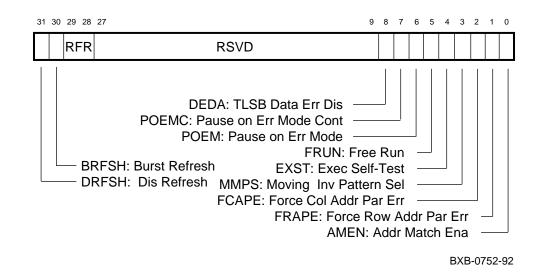

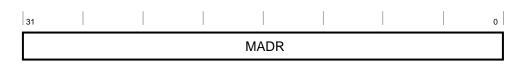

The four TLESRn registers are independent of each other. Each register displays error and status information on one 64-bit slice of data. Two consecutive data cycles of the 64-bit data slice constitute one data transaction. When an error is detected on the data bus, error bits may set in one or more TLESRn registers.