# Digital AlphaStation 200/400 Series

# **Technical Information**

Part Number: EK-PCDSA-TI. A01

Digital Equipment Corporation Maynard, Massachusetts

#### April 1995

Digital Equipment Corporation makes no representations that the use of its products in the manner described in this publication will not infringe on existing or future patent rights, nor do the descriptions contained in this publication imply the granting of licenses to make, use, or sell equipment or software in accordance with the description.

Possession, use, or copying of the software described in this publication is authorized only pursuant to a valid written license from Digital or an authorized sublicensor.

© Digital Equipment Corporation 1995. All rights reserved.

The postpaid Reader's Comments form at the end of this document requests your critical evaluation to assist in preparing future documentation.

The following are trademarks of Digital Equipment Corporation: AlphaGeneration, AlphaServer, AlphaStation, DECchip, the DIGITAL logo, and OpenVMS.

The following are third-party trademarks:

Ethernet is a trademark of Xerox Corporation; IBM PC/AT is a trademark of International Business Machines; SIMM is a trademark of Molex Corporation; UNIX is a registered trademark in the United States and other countries licensed exclusively through X/Open Company, Ltd.; Windows NT is a trademark of Microsoft Corporation; and Windows Sound System is a trademark of Microsoft Corporation.

All other trademarks and registered trademarks are the property of their respective holders.

# Contents

### Preface

| ntended Audience xv      |  |

|--------------------------|--|

| Document Contentsxv      |  |

| Associated Documents xvi |  |

| Conventions xvii         |  |

| Abbreviationsxvii        |  |

### 1 Digital AlphaStation System Descriptions

| Overview                             |      |

|--------------------------------------|------|

| System Features                      |      |

| System Unit                          |      |

| AlphaStation 200 Series System       |      |

| Desktop Enclosure                    |      |

| Controls, Indicators, and Connectors |      |

| AlphaStation 400 Series System       |      |

| Deskside Enclosure                   |      |

| Controls Indicators, and Connectors  |      |

| System Architecture                  |      |

| Features                             |      |

| СРU                                  |      |

| Core Logic                           | 1-14 |

| Cache and Memory Control             |      |

| Data Path                            |      |

| PCI Bridge                           | 1-15 |

| Secondary Cache (Bcache)             | 1-16 |

| Memory System                        |      |

| Main Memory                          |      |

| ROM Interface                        |      |

| NVRAM                                              | 1-17 |

|----------------------------------------------------|------|

| FlashROM Memory                                    | 1-17 |

| DROM                                               |      |

| Diagnostic LEDs                                    | 1-17 |

| PCI                                                | 1-18 |

| SCSI                                               | 1-18 |

| Ethernet LAN Controller (DECchip 21040)            | 1-18 |

| ISA Bridge                                         | 1-19 |

| ISA Bus                                            | 1-19 |

| Serial I/O                                         |      |

| Keyboard/Mouse                                     | 1-19 |

| TOY Clock                                          | 1-19 |

| Floppy Disk Controller (FDC)                       | 1-20 |

| Sound Card: Digital AlphaStation 200 Series System |      |

| · ·                                                |      |

### 2 Configuring Your AlphaStation System

| Overview                                                       |      |

|----------------------------------------------------------------|------|

| System Configurations                                          |      |

| Memory                                                         |      |

| Mass Storage Expansion                                         |      |

| Internal Bay Availability: AlphaStation 200 Series Systems     |      |

| Internal Bay Availability: AlphaStation 400 Series Systems     |      |

| External SCSI Bus Expansion                                    |      |

| SCSI Termination                                               |      |

| AlphaStation 200 Series System SCSI Termination                |      |

| AlphaStation 400 Series System SCSI Termination                |      |

| SCSI IDs                                                       |      |

| PCI Expansion                                                  |      |

| PCI IDSEL Assignments                                          |      |

| Ethernet LAN Controller Chip                                   |      |

| Ethernet Identification SROM                                   |      |

| ISA Expansion                                                  |      |

| Jumpers                                                        |      |

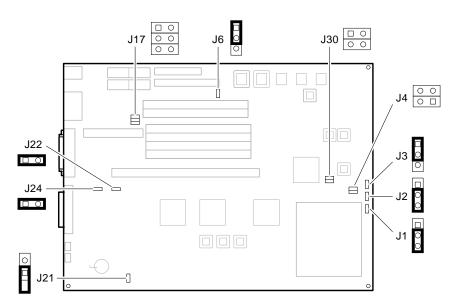

| AlphaStation 200 Series System                                 |      |

| Motherboard                                                    |      |

| Figure 2-4. AlphaStation 200 Series System Motherboard Jumpers | 2-14 |

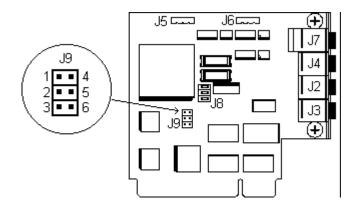

| Sound Card                                                     |      |

| AlphaStation 400 Series System                                 |      |

| Motherboard                                                    |      |

| CPU Module                                                     |      |

### 3 Addressing

| Overview                                          |      |

|---------------------------------------------------|------|

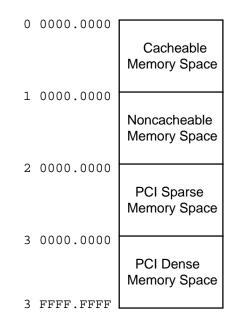

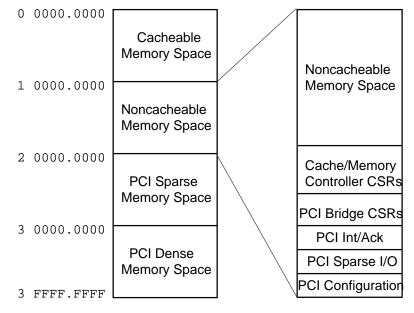

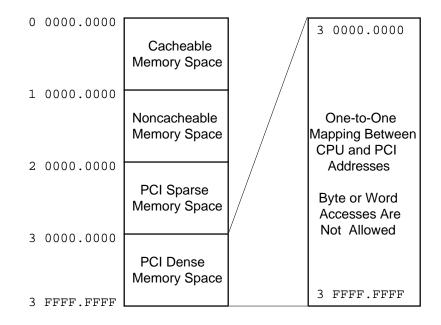

| Address Diagram                                   |      |

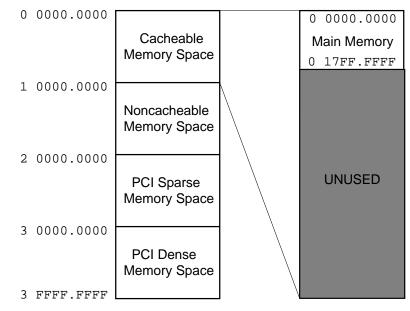

| Cacheable Memory Space: 0 0000.0000-0 FFFF.FFFF   |      |

| Noncacheable Memory Space:1 0000.0000-1 FFFF.FFFF | 3-4  |

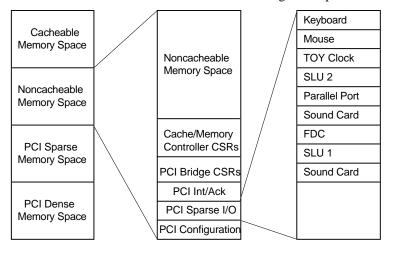

| First Two GBytes of Noncacheable Space            | 3-4  |

| Cache/Memory Controller                           |      |

| PCI Bridge Registers                              |      |

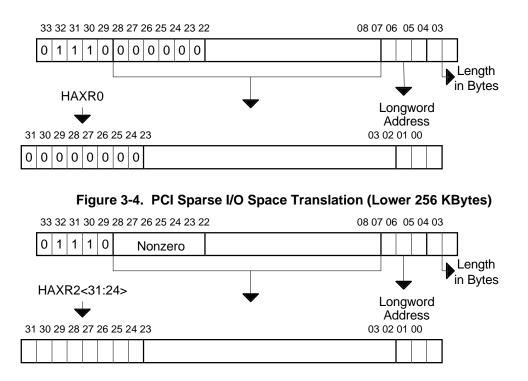

| PCI Sparse I/O Space                              |      |

| Embedded ISA Device Addresses                     |      |

| AlphaStation 200 Series System Sound Card         | 3-14 |

| Configuration Cycles                              |      |

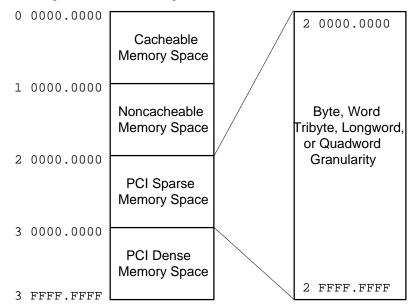

| PCI Sparse Memory Space                           | 3-16 |

| PCI Dense Memory Space                            |      |

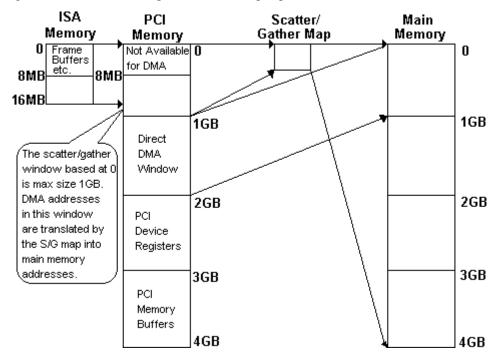

| I/O Device View of I/O Space                      |      |

### 4 I/O Programming

### 5 DMA

| Overview         | . 5- | -1 |

|------------------|------|----|

| ISA DMA Channels | . 5- | -1 |

### 6 Hardware Interrupts

| Overview                          |  |

|-----------------------------------|--|

| Interrupts                        |  |

| IRQ0: CPU Bus and Parity Errors   |  |

| IRQ2: Device Interrupts           |  |

| IRQ3: NMI (Nonmaskable Interrupt) |  |

| IRQ4: Interval Timer Interrupt    |  |

| IRQ5: HALTREQ                     |  |

| Interrupt Inputs                  |  |

|                                   |  |

| PCI Interrupts |

|----------------|

|----------------|

### 7 System Power-Up and Initialization

| Overview                                  | 7-1 |

|-------------------------------------------|-----|

| Power-Up Sequence                         | 7-1 |

| Power Supply and Input Power Requirements |     |

| AlphaStation 200 Series System            | 7-2 |

| AlphaStation 400 Series System            |     |

### 8 AlphaStation Firmware

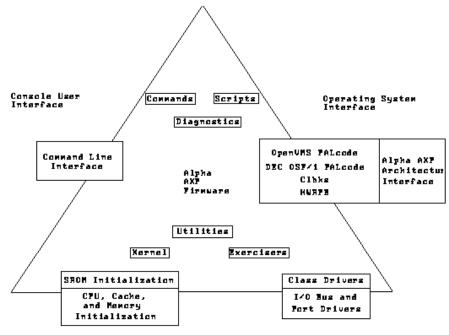

| Overview                                               | 8-1  |

|--------------------------------------------------------|------|

| Firmware Components                                    | 8-1  |

| Initialization                                         |      |

| SROM Features                                          | 8-3  |

| Loading the SROM Code                                  | 8-3  |

| SROM LED Codes                                         | 8-3  |

| SROM Beep Codes                                        | 8-5  |

| Leaving the SROM Code                                  | 8-5  |

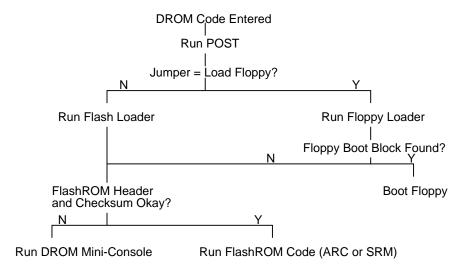

| DROM Features                                          | 8-5  |

| Loading the DROM code                                  | 8-6  |

| DROM LED Codes                                         | 8-6  |

| DROM Beep Codes                                        | 8-7  |

| Leaving the DROM Code                                  | 8-7  |

| ARC Console Features                                   | 8-9  |

| ARC Console LED Codes                                  | 8-9  |

| SRM Console Features                                   | 8-10 |

| SRM Console LED Codes                                  | 8-10 |

| ISA Configuration Utility                              | 8-12 |

| Command Format                                         | 8-12 |

| Adding ISA Options to OpenVMS and Digital UNIX Systems | 8-14 |

| ISACFG Command Examples                                |      |

| SRM Scripts                                            | 8-15 |

|                                                        |      |

### 9 Fault Management

| Overview             | . 9-1 |

|----------------------|-------|

| Control Signal Codes | . 9-2 |

| PCI Cycle Codes      |       |

| Cycle Acknowledgment |       |

| Cycle Request        |       |

| - 5                  |       |

| IO Commands                                                     |      |

|-----------------------------------------------------------------|------|

| Summary of Errors                                               |      |

| Machine Check ID                                                |      |

| Machine Check Logout Frame                                      |      |

| Error Registers                                                 |      |

| PALcode and Operating System Responsibilities                   |      |

| Error Format                                                    | 9-10 |

| SCB 660 Fatal Machine Checks                                    | 9-11 |

| Machine Check Code 0x201, Retry Timeout Error                   | 9-11 |

| Machine Check Code 0x202, DMA Data Parity Error                 | 9-11 |

| Machine Check Code 0x203, I/O Parity Error                      | 9-12 |

| Machine Check Code 0x204, Target Abort                          | 9-12 |

| Machine Check Code 0x205, No Device                             | 9-14 |

| Machine Check Code 0x206, Correctable Memory Error              | 9-14 |

| Machine Check Code 0x207, Uncorrectable Memory Error            | 9-15 |

| Machine Check Code 0x208, Invalid Page Table Lookup             | 9-15 |

| Machine Check Code 0x209, Memory Error                          | 9-16 |

| Machine Check Code 0x20A, Bcache Tag Address Parity Error       | 9-17 |

| Machine Check Code 0x20B, Bcache Tag Control Parity Error       | 9-17 |

| Machine Check Code 0x20C, Nonexistent Memory Error              | 9-18 |

| Machine Check Code 0x20D, I/O Bus Error                         | 9-18 |

| Machine Check Code 0x80, Bcache Tag Parity Error                | 9-19 |

| Machine Check Code 0x82, Bcache Tag Control Parity Error        | 9-20 |

| SCB 670 PROCESSOR FATAL MACHINE CHECKS                          | 9-21 |

| Machine Check Code 0x84, Hard Error                             | 9-21 |

| Machine Check Code 0x86, Correctable ECC                        | 9-21 |

| Machine Check Code 0x88, Noncorrectable ECC                     | 9-22 |

| Machine Check Code 0x8A, Unknown Error                          | 9-22 |

| Machine Check Code 0x8C, Soft Error                             | 9-23 |

| Machine Check Code 0x8E, Bugcheck                               | 9-23 |

| Machine Check Code 0x90, OS Bugcheck                            | 9-24 |

| Machine Check Code 0x92, Primary Cache Data Fill Error (Dcache) | 9-24 |

| Machine Check Code 0x94, Primary Cache Data Fill Error (Icache) | 9-25 |

| Primary Cache Fill ECC Error                                    | 9-25 |

| ADDITIONAL ERRORS                                               | 9-26 |

| Bcache Multiple Error                                           |      |

| Lost Error                                                      | 9-26 |

| Primary Cache Multiple Error                                    | 9-27 |

### **10 Connector and Cable Information**

| AlphaStation 200 Series System Internal Connectors 10-1 |  |

|---------------------------------------------------------|--|

| Motherboard10-1                                         |  |

| Serial Diagnostic Port 10-1                             |  |

| Speaker Connector 10-2                                  |  |

| Floppy Disk Controller 10-3                             |  |

| Sound Card Connector                                    |  |

| Front-Panel Lights and Switches Connector 10-4          |  |

| Internal SCSI Bus Connector J15 10-5                    |  |

| Power Connectors                                        |  |

| Fan Connector                                           |  |

| Riser Card 10-6                                         |  |

| Sound Card 10-7                                         |  |

| AlphaStation 400 Series System Connectors and Cables    |  |

| Motherboard                                             |  |

| Floppy                                                  |  |

| Front-Panel Lights and Switches Connector 10-8          |  |

| CPU Module: Serial Diagnostic Port 10-9                 |  |

| PCI Slots                                               |  |

| ISA Expansion Slots                                     |  |

| External Connectors                                     |  |

| Parallel Port                                           |  |

| Serial Line Units                                       |  |

| COM1/2 Pinouts                                          |  |

| SCSI                                                    |  |

| Connector Pinouts                                       |  |

| Keyboard/Mouse                                          |  |

| Internal Cables                                         |  |

| Sound Card                                              |  |

| Sound Calu10-23                                         |  |

### 11 Registers

| Overview                                                                          |

|-----------------------------------------------------------------------------------|

| CPU Registers                                                                     |

| Translation Buffer Tag (TB_TAG) Register 11-2                                     |

| Instruction Translation Buffer Page Table Entry (ITB_PTE) Register 11-2           |

| Instruction Cache Control and Status Register (ICCSR) 11-2                        |

| Instruction Translation Buffer Page Table Entry Temp (ITB_PTE_TEMP) Register 11-3 |

| Exceptions Address (EXC_ADDR) Register 11-3                                       |

| Clear Serial Line Interrupt Register (SL_CLR) 11-3                                |

| Serial Line Receive (SL_RCV) Register 11-3                                        |

| Instruction Translation Buffer ZAP (ITBZAP) Register 11-3                         |

| Instruction Translation Buffer ASM (ITBASM) Register 11-3                         |

|     | Instruction Translation Buffer IS (ITBIS) Register                         | . 11-3 |

|-----|----------------------------------------------------------------------------|--------|

|     | Processor Status (PS) Register                                             |        |

|     | Exception Summary (EXC_SUM) Register                                       | . 11-4 |

|     | PAL Base Address (PAL_BASE) Register                                       | . 11-4 |

|     | Hardware Interrupt Request Register (HIRR)                                 | . 11-4 |

|     | Software Interrupt Request Register (SIRR)                                 | . 11-5 |

|     | Asynchronous Trap Request Register (ASTRR)                                 | . 11-5 |

|     | Hardware Interrupt Enable Register (HIER)                                  | . 11-5 |

|     | Software Interrupt Enable Register (SIER)                                  | . 11-6 |

|     | AST Interrupt Enable Register (ASTER)                                      | . 11-6 |

|     | Serial Line Transmit Register (SL_XMIT)                                    | . 11-6 |

|     | Translation Buffer Control (TB_CTL) Register                               |        |

|     | Data Translation Buffer Page Table Entry Register (DTB_PTE)                | . 11-7 |

|     | Data Translation Buffer Page Table Entry Temporary (DTB_PTE_TEMP) Register | . 11-7 |

|     | Memory Management Control and Status Register (MM_CSR)                     | . 11-7 |

|     | Virtual Address (VA) Register                                              | . 11-7 |

|     | Data Translation Buffer ZAP (DTBZAP) Register                              | . 11-7 |

|     | Data Translation Buffer ASM (DTBASM) Register                              |        |

|     | Data Translation Buffer Invalidate Single (DTBIS) Register                 |        |

|     | Flush Instruction Cache (FLUSH_IC) Register                                |        |

|     | Flush Instruction Cache ASM (FLUSH_IC_ASM) Register                        |        |

|     | Abox Control Register                                                      |        |

|     | Alternate Processor Mode (ALT_MODE) Register                               |        |

|     | Cycle Counter (CC) Register                                                |        |

|     | Cycle Counter Control (CC_CTL) Register                                    |        |

|     | Bus Interface Unit Control (BIU_CTL) Register                              |        |

|     | Data Cache Status (DC_STAT) Register                                       |        |

|     | Cache Status (C_STAT) Register                                             |        |

|     | Bus Interface Unit Status (BIU_STAT) Register                              |        |

|     | Bus Interface Unit Address (BIU_ADDR) Register                             |        |

|     | Fill Address (FILL_ADDR) Register                                          |        |

|     | Fill Syndrome (FILL_SYNDROME) Register                                     |        |

|     | Backup Cache Tag (BC_TAG) Register                                         |        |

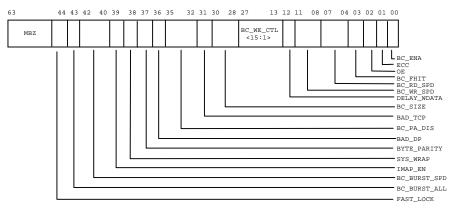

| Cac | che and Memory Control CSRs                                                |        |

|     | General Control Register                                                   |        |

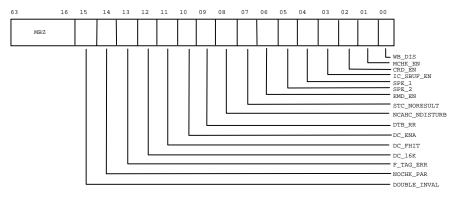

|     | Error and Diagnostic Status Register                                       |        |

|     | Tag Enable Register                                                        |        |

|     | Error Low Address Register                                                 |        |

|     | Error High Address Register                                                |        |

|     | LDxL Low Address Register                                                  |        |

|     | LDxL High Address Register                                                 |        |

|     | Bankset 0-8 Base Address Registers                                         |        |

|     | Bankset 0-7 Configuration Registers                                        | 11-14  |

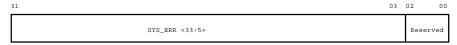

| PCI Bus Bridge CSRs                    | 11-15 |

|----------------------------------------|-------|

| Diagnostic Control and Status Register | 11-15 |

| PCI Error Address Register             | 11-15 |

| Sysbus Error Address Register          | 11-15 |

| Translated Base Registers              | 11-16 |

| PCI Base Registers                     | 11-16 |

| PCI Mask Registers                     | 11-16 |

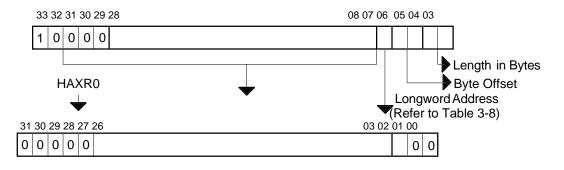

| Host Address Extension Register 0      | 11-16 |

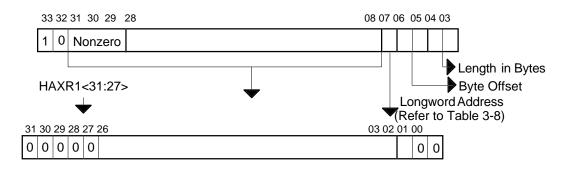

| Host Address Extension Register 1      | 11-17 |

| Host Address Extension Register 2      | 11-17 |

| Master Latency Timer Register          | 11-17 |

| TLB Tag Registers 0-7                  | 11-17 |

| TLB Data Registers 0-7                 | 11-18 |

| I/O Registers                          | 11-18 |

| PCI Bus Device Registers               | 11-18 |

| Ethernet Controller Registers          | 11-18 |

| SCSI Controller Registers              | 11-19 |

| ISA Bus Device Registers               | 11-20 |

| Keyboard and Mouse Registers           | 11-20 |

| TOY Clock Registers                    | 11-20 |

| Serial Port Registers                  | 11-20 |

| Parallel Port Registers                | 11-20 |

| Floppy Disk Controller Registers       | 11-20 |

| Sound Card Registers                   | 11-21 |

| Audio Command Register                 | 11-22 |

| Audio ID and Status Register           | 11-22 |

|                                        |       |

### Index

### Figures

| 1-1 | AlphaStation 200 Series Control and Indicators     |      |

|-----|----------------------------------------------------|------|

| 1-2 | AlphaStation 200 Series Rear Connectors            |      |

| 1-3 | AlphaStation 400 Series Control and Indicators     |      |

| 1-4 | AlphaStation 400 Series Rear Connectors            |      |

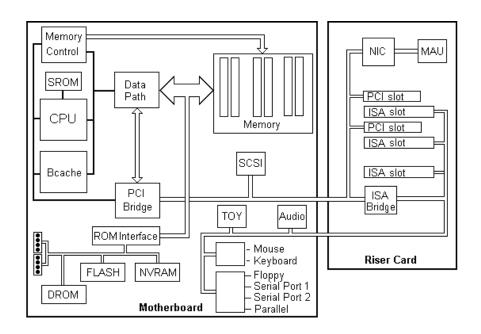

| 1-5 | AlphaStation 200 Series System Architecture        | 1-12 |

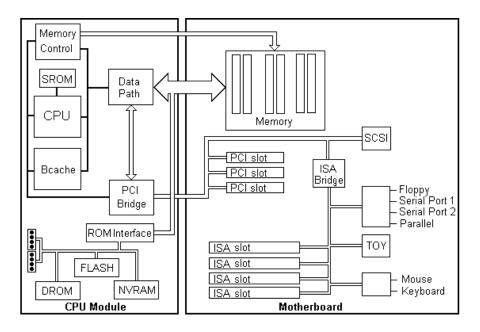

| 1-6 | AlphaStation 400 Series System Architecture        | 1-13 |

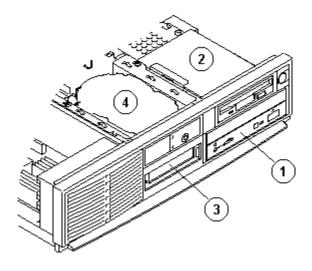

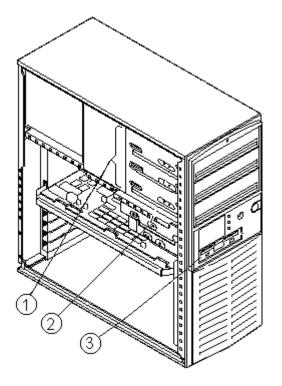

| 2-1 | Internal Bays - AlphaStation 200 Series System     |      |

| 2-2 | Internal Bays - AlphaStation 400 Series Systems    |      |

| 2-3 | PCI Configuration Header Region                    |      |

| 2-4 | AlphaStation 200 Series System Motherboard Jumpers |      |

|     |                                                    |      |

| 2-5  | AlphaStation 200 Series Sound Card Jumpers                  |       |

|------|-------------------------------------------------------------|-------|

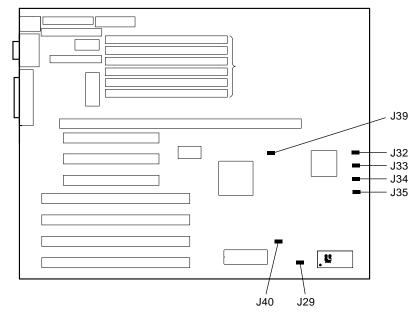

| 2-6  | AlphaStation 400 Series Motherboard Jumpers                 |       |

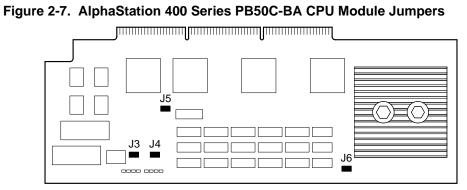

| 2-7  | AlphaStation 400 Series PB50C-BA CPU Module Jumpers         |       |

| 3-1  | Physical Address Space                                      |       |

| 3-2  | Cacheable Memory Space                                      |       |

| 3-3  | Noncacheable Address Space                                  |       |

| 3-4  | PCI Sparse I/O Space Translation (Lower 256 KByte)          |       |

| 3-5  | PCI Sparse I/O Address Translation (Remaining 16 MBytes)    |       |

| 3-6  | PCI Sparse Address Space                                    |       |

| 3-7  | PCI Sparse Memory Space                                     |       |

| 3-8  | PCI Memory Space Address Translation (Lower 16 MBytes)      | 3-17  |

| 3-9  | PCI Memory Space Address Translation (Remaining 112 MBytes) |       |

| 3-10 | PCI Dense Memory Space                                      |       |

| 3-11 | Address Space from the I/O Perspective                      |       |

| 4-1  | Flashbus Index Register                                     |       |

| 4-2  | Flashbus Data Register                                      |       |

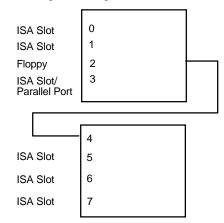

| 5-1  | DMA Channel Assignments                                     |       |

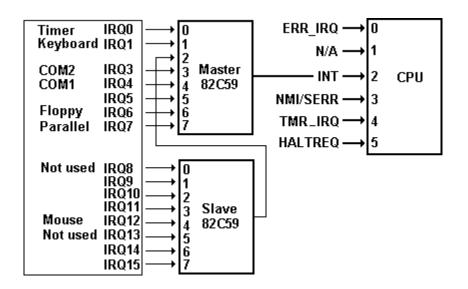

| 6-1  | Interrupt System Block Diagram                              |       |

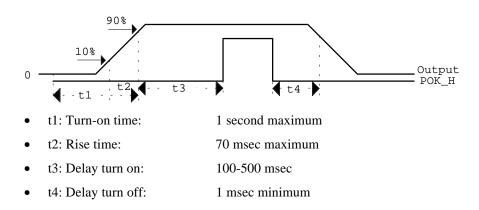

| 7-1  | Power Supply Timing                                         |       |

| 8-1  | AlphaStation Interface Relationships                        |       |

| 8-2  | Possible DROM Code Actions                                  |       |

| 10-1 | AlphaStation 200 Series System Rear Connectors              | 10-14 |

| 10-2 | AlphaStation 400 Series System Rear Connectors              | 10-16 |

|      |                                                             |       |

### Tables

| 1-1  | Distinctive Features of the Digital AlphaStation 200 and 400 Series Systems | 1-2  |

|------|-----------------------------------------------------------------------------|------|

| 1-2  | AlphaStation Series Front Controls and Indicators                           | 1-4  |

| 1-3  | AlphaStation 200 Series Rear Connectors                                     | 1-5  |

| 1-4  | AlphaStation 400 Series Controls and Indicators                             | 1-8  |

| 1-5  | AlphaStation 400 Series Rear Connectors                                     | 1-10 |

| 2-1  | Typical Digital AlphaStation System Configurations                          | 2-2  |

| 2-2  | Supported SIMMs for the Digital AlphaStation                                | 2-3  |

| 2-3  | Description of the AlphaStation 200 Series Internal Bays                    | 2-4  |

| 2-4  | Description of the AlphaStation 400 Series System Internal Bays             | 2-6  |

| 2-5  | AlphaStation 200 Series System SCSI ID Assignments                          | 2-8  |

| 2-6  | AlphaStation PCI Expansion Tasks                                            | 2-9  |

| 2-7  | AlphaStation 200 Series System: PCI AD <n> to IDSEL# Assignments</n>        | 2-10 |

| 2-8  | Procedure for Adding ISA Options                                            | 2-13 |

| 2-9  | AlphaStation 200 Series Motherboard Jumper Locations                        | 2-15 |

| 2-10 | AlphaStation 200 Series System Sound Card Jumper Descriptions               | 2-17 |

| 2-11 | AlphaStation 400 Series Motherboard Jumpers                                 | 2-19 |

| 2-12 | AlphaStation 400 Series PB50C-BA CPU Module Jumper Descriptions | 2-21 |

|------|-----------------------------------------------------------------|------|

| 3-1  | Noncacheable Memory: The First Two GByte                        | 3-4  |

| 3-2  | Cache Memory Controller Registers                               | 3-5  |

| 3-3  | PCI Bridge Register Addresses                                   |      |

| 3-4  | PCI Sparse I/O Space Byte Selection                             | 3-10 |

| 3-5  | Embedded ISA Device Addresses                                   |      |

| 3-6  | AlphaStation 200 Series System Sound Card I/O Addresses         | 3-14 |

| 3-7  | PCI Configuration Cycle Byte Selection                          | 3-15 |

| 3-8  | PCI Sparse Memory Space Byte Selection                          | 3-17 |

| 4-1  | Flashbus Index Register Bit Descriptions                        | 4-2  |

| 4-2  | Flashbus Data Register Bit Descriptions                         | 4-2  |

| 4-3  | Flashbus Device Offset Addresses                                | 4-3  |

| 6-1  | CPU Interrupt Inputs                                            |      |

| 6-2  | AlphaStation Interrupt Assignments                              | 6-4  |

| 6-3  | PCI Interrupt Assignments                                       |      |

| 7-1  | AlphaStation Series System AC Input Characteristics             |      |

| 7-2  | AlphaStation 400 Series System AC Input Characteristics         |      |

| 8-1  | AlphaStation Series System SROM Code Actions                    | 8-4  |

| 8-2  | AlphaStation SROM Beep Codes                                    | 8-5  |

| 8-3  | AlphaStation DROM POST Actions and LED Codes                    | 8-6  |

| 8-4  | AlphaStation DROM Beep Codes                                    | 8-7  |

| 8-5  | ARC Console LED Codes                                           | 8-9  |

| 8-6  | SRM Console LED Codes                                           | 8-10 |

| 8-7  | SRM ISACFG Command Options                                      | 8-12 |

| 8-8  | Adding Options to OpenVMS or Digital UNIX Systems               | 8-14 |

| 9-1  | PCI Cycle Codes                                                 |      |

| 9-2  | PCI cAck Cycle Codes                                            |      |

| 9-3  | PCI cReq Cycle Codes                                            |      |

| 9-4  | PCI IO Commands                                                 |      |

| 9-5  | Machine Check ID Codes                                          |      |

| 9-6  | Machine Check Logout Frame                                      |      |

| 9-7  | Error Registers                                                 |      |

| 9-8  | Error Format                                                    |      |

| 9-9  | Error: Retry Timeout                                            |      |

| 9-10 | Error: DMA Data Parity Error                                    |      |

| 9-11 | Error: I/O Parity                                               |      |

| 9-12 | Target Abort                                                    |      |

| 9-13 | No Device                                                       |      |

| 9-14 | Error: Correctable Memory                                       |      |

| 9-15 | Error: Uncorrectable Memory                                     |      |

| 9-16 | Invalid Page Table Lookup                                       |      |

| 9-17 | Memory Error                                                    |      |

| 9-18 | Bcache Tag Address Parity Error                                 |      |

|      |                                                                 |      |

| 9-19  | Bcache Tag Control Parity Error                                    |       |

|-------|--------------------------------------------------------------------|-------|

| 9-20  | Nonexistent Memory Error                                           | 9-18  |

| 9-21  | I/O Bus Error                                                      |       |

| 9-22  | Bcache Tag Parity Error                                            | 9-19  |

| 9-23  | Bcache Tag Control Parity Error                                    | 9-20  |

| 9-24  | Hard Error                                                         | 9-21  |

| 9-25  | Correctable ECC                                                    | 9-21  |

| 9-26  | Noncorrectable ECC                                                 | 9-22  |

| 9-27  | Unknown Error                                                      | 9-22  |

| 9-28  | Soft Error                                                         | 9-23  |

| 9-29  | Bugcheck                                                           | 9-23  |

| 9-30  | OS Bugcheck                                                        | 9-24  |

| 9-31  | Primary Cache Data Fill Error (Dcache)                             | 9-24  |

| 9-32  | Primary Cache Data Fill Error (Icache)                             |       |

| 9-33  | Primary Cache Fill ECC Error                                       | 9-25  |

| 9-34  | Bcache Multiple Error                                              | 9-26  |

| 9-35  | Lost Error                                                         | 9-26  |

| 9-36  | Primary Cache Multiple Error                                       | 9-27  |

| 10-1  | Serial Diagnostic Port Connector Pinout                            |       |

| 10-2  | AlphaStation 200 Series System Audio Connector Pinout              | 10-2  |

| 10-3  | Floppy Device Controller Connector Pinouts                         | 10-3  |

| 10-4  | AlphaStation 200 Series System Front-Panel Connectors              | 10-4  |

| 10-5  | Internal SCSI Bus Connector                                        |       |

| 10-6  | AlphaStation 200 Series System Motherboard Power Connectors        |       |

| 10-7  | Media Adapter Unit AUI Pinouts                                     | 10-7  |

| 10-8  | AlphaStation 200 Series System Sound Card Connectors               | 10-7  |

| 10-9  | Floppy Device Controller Connector Pinouts                         | 10-8  |

| 10-10 | AlphaStation 400 Series System Front-Panel Connector Pinouts (J31) |       |

|       | Serial Diagnostic Port Connector Pinout                            |       |

| 10-12 | PCI Slot Connector Pinouts                                         | 10-10 |

|       | ISA Slot Connector Pinouts                                         |       |

|       | AlphaStation 200 Series System Rear Connectors                     |       |

|       | AlphaStation 400 Series System Rear Connectors                     |       |

|       | AlphaStation 400 Series System External Connectors                 |       |

|       | Parallel Port Connector Pinout                                     |       |

|       | COM1 and COM 2 Connector Pinouts                                   |       |

|       | SCSI Connector Pinouts                                             |       |

|       | Keyboard Connector Pinouts                                         |       |

|       | Mouse Connector Pinouts                                            |       |

|       | AlphaStation 200 Series System Internal Cables                     |       |

|       | AlphaStation 200 Series System Sound Card Connectors               |       |

| 10-24 | AlphaStation 400 Series System Internal Cables                     |       |

| 11-1  | SCSI Chip Register Map                                             | 11-19 |

|       |                                                                    |       |

| 11-2 | ISA Device Addresses                                         |  |

|------|--------------------------------------------------------------|--|

| 11-3 | Audio Register Offsets                                       |  |

| 11-4 | Audio IRQ Selection                                          |  |

| 11-5 | AlphaStation 200 Series system Audio DMA Channel Selection . |  |

### **Intended Audience**

This information is intended for VARs (value-added resellers), ISVs, and other system users or service providers who are configuring their own systems or adding features to existing AlphaStation 200/400 Series systems.

### **Document Contents**

This information covers the following general topics (see the Table of Contents for a detailed listing of the material mentioned here):

- Distinctive system features of the Digital AlphaStation 200 Series and 400 Series systems

- Steps in system configuration

- Addressing

- I/O programming

- Direct memory access (DMA)

- Hardware exceptions and interrupts

- System power-up and initialization

- AlphaStation firmware

- Errors and machine checks

- Connector and cable information

- Console commands

- Registers

### **Associated Documents**

For additional information on the Digital AlphaStation 200/400 Series systems, refer to the following information sources:

- Digital AlphaStation 400 Series User Information (EK-PCDSA-UI)

- Digital AlphaStation 400 Series Installation Information (EK-PCDSA-II)

- Digital AlphaStation 200 Series User Information (EK-PCDTA-UI)

- Digital AlphaStation 200 Series Installation Information (EK-PCDTA-II)

Refer to the following additional sources for technical information:

- System I/O (SIO) 82378IB chip, Intel

- PC87332 (Super I/O III) chip, National Semiconductor

- Alpha Architecture Handbook (EC-H1689-10), Digital Equipment Corporation

- DECchip 21064 and DECchip 21064A Microprocessor Hardware Reference Manual, order number EC-Q9ZUA-TE, Digital Equipment Corporation

- *DECchip 2107/21072 Core Chip Sets Data Sheet,* order number EC-N0648-72, Digital Equipment Corporation

- *DECchip 21040 Ethernet LAN Controller for PCI Hardware Reference Manual* (EC-N0752-72), Digital Equipment Corporation

- 53C810 SCSI I/O Processor Data Manual, NCR

- 53C720 SCSI I/O Processor Programmer's Guide, NCR

- BQ4285 Time-of-Year/NVR chip (TOY), Brooktree

- *PCI Local Bus Specification, Revision 2.0, PCI Special Interest Grove, Order Number 281446-001*

- ISA Bus Specification, IEEE Standards Office

- 8242 Keyboard Controller Specification, Intel, PHOENIX Technologies, Ltd.

For information on the error logger within operating systems, write to Intel Corporation, Literature Sales, P.O. Box 7641, Mt. Prospect, Il 60056-7641. Request the following item: 82420/82430 PCIset ISA and EISA Bridges, Order Number 290483-001.

### Conventions

| Convention Example     | Description                                                                                                                                                           |  |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| [Enter]                | Square brackets around text represent a key on the keyboard.                                                                                                          |  |

| c:\windows             | Monospaced text indicates file names, path names,<br>addresses, directories, or screen text. Each operating<br>system has its own specific syntax.                    |  |

| bold text              | <b>Bold</b> text is used occasionally to set off material.                                                                                                            |  |

| <i>italicized</i> text | <i>Italicized</i> text is used for commands that you enter,<br>buttons that you press, and so forth. <i>Italic</i> type is used<br>occasionally for emphasis as well. |  |

| Addresses              | 1 A000 0020                                                                                                                                                           |  |

|                        | Addresses are formatted with spaces (for example, 1 A000 0020h) rather than with commas.                                                                              |  |

This document uses the following conventions:

### Abbreviations

This information uses the following, commonly used abbreviations:

| Abbreviation | Meaning                                                             |

|--------------|---------------------------------------------------------------------|

| ASIC         | application-specific integrated circuit                             |

| KByte        | kilobyte                                                            |

| MByte        | megabyte                                                            |

| AUI          | adapter or attachment unit interface, thickwire Ethernet connection |

| CAS          | column address strobe                                               |

| CPU          | central processing unit                                             |

| DRAM         | dynamic RAM                                                         |

| D-stream     | data stream                                                         |

| ECC          | error correction code                                               |

| EIA          | Electronics Industry Association                                    |

| EID          | Ethernet identification                                             |

| FDC          | floppy disk controller                                              |

| I/O          | input/output                                                        |

#### (continued)

| ISAindustry-standard architectureI-streaminstruction streamkbits1024 bitsKbytes1000 bytes for storage; 1024 bytes for<br>memorykHzkiloHertz, 1000 cycles per secondMAUmedia adapter unitMbits1,048,576 bitsMBytes1,000,000 bytes for storage; 1,048,576<br>bytes for memoryMHzmegaHertz, 1,000,000 cycles per<br>secondNVRAMnonvolatile RAMPCIperipheral component interconnectPLLphase-locked loopRAMrandom access memoryRASrow address strobeRISCreduced instruction set computerROMsingle in-line memory moduleSIMMsingle in-line memory moduleSIOSystem I/O chip, Intel 87378IB<br>PCI-ISA bridge chip or super I/O chip<br>(parallel port, SLU) NCR 97332SRAMstatic RAMTOYtime-of-year clock chipVCOvoltage-controlled oscillatorZIFzero insertion force | (conunuea) |                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------------------------|

| kbits1024 bitskbits1000 bytes for storage; 1024 bytes for<br>memoryKHzkiloHertz, 1000 cycles per secondMAUmedia adapter unitMbits1,048,576 bitsMBytes1,000,000 bytes for storage; 1,048,576<br>bytes for memoryMHzmegaHertz, 1,000,000 cycles per<br>secondNVRAMnonvolatile RAMPCIperipheral component interconnectPLLphase-locked loopRAMrandom access memoryRASrow address strobeRISCreduced instruction set computerROMsingle in-line memory moduleSIOSystem I/O chip, Intel 87378IB<br>PCI-ISA bridge chip or super I/O chip<br>(parallel port, SLU) NCR 97332SRAMstatic RAMTOYtime-of-year clock chipVCOvoltage-controlled oscillator                                                                                                                    | ISA        | industry-standard architecture        |

| KinkFULTIONKbytes1000 bytes for storage; 1024 bytes for<br>memorykHzkiloHertz, 1000 cycles per secondMAUmedia adapter unitMbits1,048,576 bitsMBytes1,000,000 bytes for storage; 1,048,576<br>bytes for memoryMHzmegaHertz, 1,000,000 cycles per<br>secondNVRAMnonvolatile RAMPCIperipheral component interconnectPLLphase-locked loopRAMrandom access memoryRASrow address strobeRISCreduced instruction set computerROMsingle in-line memory moduleSIOSystem I/O chip, Intel 87378IB<br>PCI-ISA bridge chip or super I/O chip<br>(parallel port, SLU) NCR 97332SRAMstatic RAMTOYvoltage-controlled oscillator                                                                                                                                                | I-stream   | instruction stream                    |

| memorykHzkiloHertz, 1000 cycles per secondMAUmedia adapter unitMbits1,048,576 bitsMBytes1,000,000 bytes for storage; 1,048,576<br>bytes for memoryMHzmegaHertz, 1,000,000 cycles per<br>secondNVRAMnonvolatile RAMPCIperipheral component interconnectPLLphase-locked loopRAMrandom access memoryRASrow address strobeRISCreduced instruction set computerROMsingle in-line memory moduleSIMMsingle in-line memory moduleSIOSystem I/O chip, Intel 87378IB<br>PCI-ISA bridge chip or super I/O chip<br>(parallel port, SLU) NCR 97332SRAMstatic RAMTOYvoltage-controlled oscillator                                                                                                                                                                           | kbits      | 1024 bits                             |

| MAUmedia adapter unitMbits1,048,576 bitsMBytes1,000,000 bytes for storage; 1,048,576<br>bytes for memoryMHzmegaHertz, 1,000,000 cycles per<br>secondNVRAMnonvolatile RAMPCIperipheral component interconnectPLLphase-locked loopRAMrandom access memoryRASrow address strobeRISCreduced instruction set computerROMread-only memorySCSIsmall computer system interconnectSIMMsingle in-line memory moduleSIOSystem I/O chip, Intel 87378IB<br>PCI-ISA bridge chip or super I/O chip<br>(parallel port, SLU) NCR 97332SRAMstatic RAMTOYtime-of-year clock chipVCOvoltage-controlled oscillator                                                                                                                                                                 | Kbytes     |                                       |

| Mbits1,048,576 bitsMBytes1,000,000 bytes for storage; 1,048,576<br>bytes for memoryMHzmegaHertz, 1,000,000 cycles per<br>secondNVRAMnonvolatile RAMPCIperipheral component interconnectPLLphase-locked loopRAMrandom access memoryRASrow address strobeRISCreduced instruction set computerROMread-only memorySCSIsmall computer system interconnectSIMMsingle in-line memory moduleSIOSystem I/O chip, Intel 87378IB<br>PCI-ISA bridge chip or super I/O chip<br>(parallel port, SLU) NCR 97332SRAMstatic RAMTOYtime-of-year clock chipVCOvoltage-controlled oscillator                                                                                                                                                                                      | kHz        | kiloHertz, 1000 cycles per second     |

| MBytes1,000,000 bytes for storage; 1,048,576<br>bytes for memoryMHzmegaHertz, 1,000,000 cycles per<br>secondNVRAMnonvolatile RAMPCIperipheral component interconnectPLLphase-locked loopRAMrandom access memoryRASrow address strobeRISCreduced instruction set computerROMread-only memorySCSIsmall computer system interconnectSIMMsingle in-line memory moduleSIOSystem I/O chip, Intel 87378IB<br>PCI-ISA bridge chip or super I/O chip<br>(parallel port, SLU) NCR 97332SRAMstatic RAMTOYtime-of-year clock chipVCOvoltage-controlled oscillator                                                                                                                                                                                                         | MAU        | media adapter unit                    |

| bytes for memoryMHzmegaHertz, 1,000,000 cycles per<br>secondNVRAMnonvolatile RAMPCIperipheral component interconnectPLLphase-locked loopRAMrandom access memoryRASrow address strobeRISCreduced instruction set computerROMread-only memorySCSIsmall computer system interconnectSIMMsingle in-line memory moduleSIOSystem I/O chip, Intel 87378IB<br>PCI-ISA bridge chip or super I/O chip<br>(parallel port, SLU) NCR 97332SRAMstatic RAMTOYtime-of-year clock chipVCOvoltage-controlled oscillator                                                                                                                                                                                                                                                         | Mbits      | 1,048,576 bits                        |

| secondNVRAMnonvolatile RAMPCIperipheral component interconnectPLLphase-locked loopRAMrandom access memoryRASrow address strobeRISCreduced instruction set computerROMread-only memorySCSIsmall computer system interconnectSIMMsingle in-line memory moduleSIOSystem I/O chip, Intel 87378IB<br>PCI-ISA bridge chip or super I/O chip<br>(parallel port, SLU) NCR 97332SRAMstatic RAMTOYtime-of-year clock chipVCOvoltage-controlled oscillator                                                                                                                                                                                                                                                                                                               | MBytes     |                                       |

| PCIperipheral component interconnectPLLphase-locked loopRAMrandom access memoryRASrow address strobeRISCreduced instruction set computerROMread-only memorySCSIsmall computer system interconnectSIMMsingle in-line memory moduleSIOSystem I/O chip, Intel 87378IB<br>PCI-ISA bridge chip or super I/O chip<br>(parallel port, SLU) NCR 97332SRAMstatic RAMTOYtime-of-year clock chipVCOvoltage-controlled oscillator                                                                                                                                                                                                                                                                                                                                         | MHz        |                                       |

| PLLphase-locked loopRAMrandom access memoryRASrow address strobeRISCreduced instruction set computerROMread-only memorySCSIsmall computer system interconnectSIMMsingle in-line memory moduleSIOSystem I/O chip, Intel 87378IB<br>PCI-ISA bridge chip or super I/O chip<br>(parallel port, SLU) NCR 97332SRAMstatic RAMTOYtime-of-year clock chipVCOvoltage-controlled oscillator                                                                                                                                                                                                                                                                                                                                                                             | NVRAM      | nonvolatile RAM                       |

| RAMrandom access memoryRASrow address strobeRISCreduced instruction set computerROMread-only memorySCSIsmall computer system interconnectSIMMsingle in-line memory moduleSIOSystem I/O chip, Intel 87378IB<br>PCI-ISA bridge chip or super I/O chip<br>(parallel port, SLU) NCR 97332SRAMstatic RAMTOYtime-of-year clock chipVCOvoltage-controlled oscillator                                                                                                                                                                                                                                                                                                                                                                                                 | PCI        | peripheral component interconnect     |

| RASrow address strobeRISCreduced instruction set computerROMread-only memorySCSIsmall computer system interconnectSIMMsingle in-line memory moduleSIOSystem I/O chip, Intel 87378IB<br>PCI-ISA bridge chip or super I/O chip<br>(parallel port, SLU) NCR 97332SRAMstatic RAMTOYtime-of-year clock chipVCOvoltage-controlled oscillator                                                                                                                                                                                                                                                                                                                                                                                                                        | PLL        | phase-locked loop                     |

| RISCreduced instruction set computerROMread-only memorySCSIsmall computer system interconnectSIMMsingle in-line memory moduleSIOSystem I/O chip, Intel 87378IB<br>PCI-ISA bridge chip or super I/O chip<br>(parallel port, SLU) NCR 97332SRAMstatic RAMTOYtime-of-year clock chipVCOvoltage-controlled oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                             | RAM        | random access memory                  |

| ROMread-only memorySCSIsmall computer system interconnectSIMMsingle in-line memory moduleSIOSystem I/O chip, Intel 87378IB<br>PCI-ISA bridge chip or super I/O chip<br>(parallel port, SLU) NCR 97332SRAMstatic RAMTOYtime-of-year clock chipVCOvoltage-controlled oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RAS        | row address strobe                    |

| SCSIsmall computer system interconnectSIMMsingle in-line memory moduleSIOSystem I/O chip, Intel 87378IB<br>PCI-ISA bridge chip or super I/O chip<br>(parallel port, SLU) NCR 97332SRAMstatic RAMTOYtime-of-year clock chipVCOvoltage-controlled oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | RISC       | reduced instruction set computer      |

| SIMMsingle in-line memory moduleSIOSystem I/O chip, Intel 87378IB<br>PCI-ISA bridge chip or super I/O chip<br>(parallel port, SLU) NCR 97332SRAMstatic RAMTOYtime-of-year clock chipVCOvoltage-controlled oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ROM        | read-only memory                      |

| SIOSystem I/O chip, Intel 87378IB<br>PCI-ISA bridge chip or super I/O chip<br>(parallel port, SLU) NCR 97332SRAMstatic RAMTOYtime-of-year clock chipVCOvoltage-controlled oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SCSI       | small computer system interconnect    |

| PCI-ISA bridge chip or super I/O chip<br>(parallel port, SLU) NCR 97332SRAMstatic RAMTOYtime-of-year clock chipVCOvoltage-controlled oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SIMM       | single in-line memory module          |

| TOY     time-of-year clock chip       VCO     voltage-controlled oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SIO        | PCI-ISA bridge chip or super I/O chip |

| VCO voltage-controlled oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SRAM       | static RAM                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | TOY        | time-of-year clock chip               |

| ZIF zero insertion force                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | VCO        | voltage-controlled oscillator         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ZIF        | zero insertion force                  |

# 1

# Digital AlphaStation System Descriptions

### Overview

Digital AlphaStation 200 Series and 400 Series systems are state-of-the-art workstations that incorporate some of the fastest microprocessors available on the market today. This chapter covers the following general topics:

- System features

- System architecture

### **System Features**

The Digital AlphaStation 200 Series and 400 Series systems share the following characteristics:

- DECchip 21064 or 21064A Alpha architecture CPU

- DECchip 21071-AA (core logic chipset) consisting of:

- Cache/memory controller (one 21071-CA chip)

- PCI interface (one 21071-DA chip)

- Data path (two 21071-BA chips)

- 512 Kbytes of on-board secondary cache (15 ns SRAM)

- From 8 to 384 MBytes of RAM (70 ns DRAM), in three pairs of 128-MByte SIMM sockets

- One MByte of erasable/rewriteable nonvolatile memory (flashROM)

- 8 Kbytes of NVRAM

- Keyboard and mouse ports

- Two serial ports

- Bi-directional enhanced parallel port

- TOY clock

- Fast SCSI-2 controller for internal and external devices

- FDC for floppies and tapes

- PCI and ISA expansion slots

Table 1-1 outlines several distinctions between the AlphaStation 200 and 400 Series systems.

| Feature AlphaStation 200<br>Series System                    |                                        | AlphaStation 400<br>Series System |

|--------------------------------------------------------------|----------------------------------------|-----------------------------------|

| Enclosure                                                    | Slimline desktop                       | Mini-tower deskside               |

| PCI-only slots                                               | 1                                      | 2                                 |

| ISA-only slots                                               | 1<br>(half-height options only)        | 3                                 |

| PCI/ISA combination slots                                    | 1*                                     | 1                                 |

| Drive bays:<br>• 3.5-inch expansion<br>• 5.25-inch expansion | 3 (one nonaccessible)<br>1             | 2 (one nonaccessible)<br>3        |

| Ethernet LAN controller<br>(embedded)                        | Yes (on riser with a socketed EID ROM) | No                                |

| Logic to support dynamic power management                    | Yes                                    | No                                |

| Dedicated custom slot for<br>16-bit stereo audio             | Yes                                    | No                                |

# Table 1-1. Distinctive Features of the Digital AlphaStation 200 and400 Series Systems

\* Some versions of the AlphaStation 200 Series systems have two PCI/ISA slots.

### System Unit

#### AlphaStation 200 Series System

#### **Desktop Enclosure**

The Digital AlphaStation 200 Series system's corporate slimline desktop low-profile enclosure houses the motherboard, I/O riser card, power supply, audio, and Ethernet options and internal peripherals.

#### **Controls, Indicators, and Connectors**

The front of the system enclosure has a small control panel featuring a reset button and two status LEDs. The reset button causes either a CPU halt or a system reset, depending on the system module jumper's (J3) setting. The status LEDs indicate power-on and disk activity.

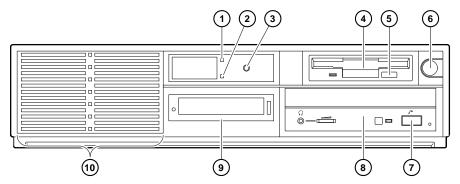

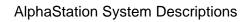

Figures 1-1 and 1-2 and Tables 1-2 and 1-3 show and describe the front and rear views, respectively, of the Digital AlphaStation 200 Series system.

The motherboard includes eight diagnostic LEDs, which are visible through ports at the rear of the system. (These viewing ports are intended for diagnostic use by manufacturing, service personnel, and repair sites.) A stake-pin connector on the motherboard provides for an internal speaker. When a sound card is present, the internal speaker is connected to it.

Figure 1-1. AlphaStation 200 Series Control and Indicators

| Figure<br>Legend | Control or Indicator    | Function                                                                   |

|------------------|-------------------------|----------------------------------------------------------------------------|

| 1                | Power indicator         | Power. Lights when the system is on.                                       |

| 2                | Disk activity indicator | Hard disk drive. Lights when a hard disk drive is in use.                  |

| 3                | Reset button            | This button resets the system and causes the self test to run.             |

| 4                | Floppy drive            | Location of 3.5-inch diskette drive.                                       |

| 5                | Floppy eject button     | Push to eject the floppy disk.                                             |

| 6                | Power on/off button     | Turns AC power on and off.                                                 |

| 7                | CD-ROM eject button     | Opens the CD loading drawer.                                               |

| 8                | CD drive (optional)     | 5.25-inch half-height front-accessible drive bay.                          |

| 9                | HDD drive               | 3.5-inch low-profile front-accessible drive bay.                           |

| 10               | Louvered air intake     | Passageway for cooling air to enter the system. (Do not block air intake.) |

Table 1-2. AlphaStation 200 Series Front Controls and Indicators

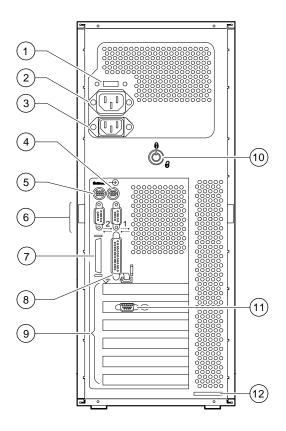

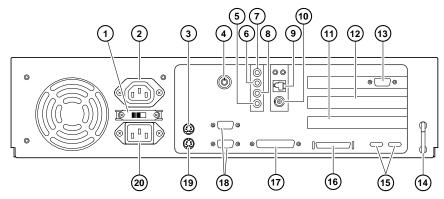

Figure 1-2. AlphaStation 200 Series Rear Connectors

| Table 1-3. AlphaStation 200 Series Rear Connectors | Table 1-3. | AlphaStation | 200 Series | s Rear Connectors | 5 |

|----------------------------------------------------|------------|--------------|------------|-------------------|---|

|----------------------------------------------------|------------|--------------|------------|-------------------|---|

| Figure<br>Legend | Connector                     | Function                                                                                                                                                                                                                            |

|------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | Voltage selector switch       | Allows you to set your system to work with 115-<br>Volt or 230-Volt AC power.                                                                                                                                                       |

| 2                | Monitor power connector       | Use to connect a monitor to AC power. <i>If your monitor consumes more than 2 Amps at 115 Volts(1 Amp at 230 Volts), connect it directly to your wall outlet.</i> This connector may be missing from future versions of the system. |

| 3                | Keyboard connector            | Use to connect a 101- or 102-key keyboard.                                                                                                                                                                                          |

| 4                | System (chassis) lock         | Locks top cover.                                                                                                                                                                                                                    |

| 5                | Sound card line in connector  | Brings audio signals into the card (for example, from a stereo amplifier).                                                                                                                                                          |

| 6                | Sound card line out connector | Routes audio signals to an external amplifier.                                                                                                                                                                                      |

| 7                | Sound card headphone jack     | Connector for the headphones or amplified speakers.                                                                                                                                                                                 |

| 8                | Sound card microphone jack    | Connector for the microphone.                                                                                                                                                                                                       |

| 9                | Twisted pair connector        | Connection to the embedded Ethernet controller .                                                                                                                                                                                    |

| 10               | ThinWire connector            | Connection to the embedded Ethernet controller .                                                                                                                                                                                    |

|    | -                                    | . ,                                                                                                                                                                                                                              |

|----|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11 | ISA expansion slot                   | Used for half-size ISA expansion options only.                                                                                                                                                                                   |

| 12 | PCI/ISA expansion slot               | Either a PCI or ISA option can use this slot.                                                                                                                                                                                    |

| 13 | PCI expansion slot                   | Used for PCI expansion options. (In earlier<br>systems, this slot was a PCI/ISA combo slot. The<br>slot was changed to PCI only to support two-board<br>PCI options.) In this example, a PCI graphics<br>adapter is in the slot. |

| 14 | Security loop                        | Attaches padlock and security cable.                                                                                                                                                                                             |

| 15 | LED viewing ports                    | Ports for viewing diagnostic LED indicators.                                                                                                                                                                                     |

| 16 | SCSI port                            | Provides the interface between the system unit and external SCSI devices.                                                                                                                                                        |

| 17 | Enhanced bidirectional parallel port | Connects an industry-standard parallel printer or other parallel device.                                                                                                                                                         |

| 18 | Serial port connectors               | Connects serial devices.                                                                                                                                                                                                         |

| 19 | Mouse connector                      | Connects a PS/2-compatible mouse.                                                                                                                                                                                                |

| 20 | AC power connector                   | Connects the system to AC power.                                                                                                                                                                                                 |

#### Table 1-3. AlphaStation 200 Series Rear Connectors (continued)

### AlphaStation 400 Series System

#### **Deskside Enclosure**

The Digital AlphaStation 400 Series system is a workstation system packaged in a minitower deskside enclosure.

#### **Controls Indicators, and Connectors**

The front of the enclosure has a small control panel featuring a reset button and three status LEDs. The reset button causes a system reset. The top two status LEDs indicate power-on and disk activity. The lowermost status LED is unused in this system.

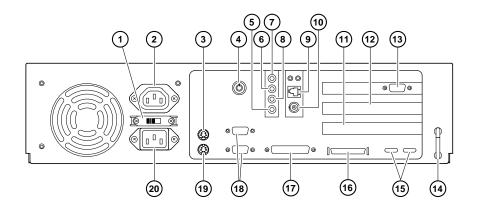

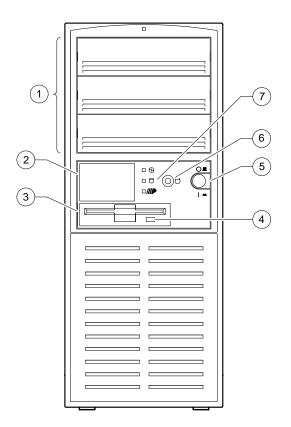

Figures 1-3 and 1-4 and Tables 1-4 and 1-5 show and describe the front and rear views, respectively, of the Digital AlphaStation 400 Series system.

The CPU module contains eight diagnostic LEDs. (These are not visible during normal system operation and are intended for diagnostic use only by manufacturing, service personnel, and repair sites.) A stake-pin connector on the motherboard provides for an internal speaker.

Figure 1-3. AlphaStation 400 Series Control and Indicators

| Figure<br>Legend | Control or Indicator | Function                                                                                                                                                                                                                     |  |

|------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1                | Drive bays           | Location of three upper 5.25-inch drive bays.                                                                                                                                                                                |  |

| 2                | Hard drive           | Location of hidden 3.5-inch drive bay.                                                                                                                                                                                       |  |

| 3                | Floppy drive         | Location of 3.5-inch diskette drive.                                                                                                                                                                                         |  |

| 4                | Floppy eject button  | Releases a 3.25-inch diskette from the floppy diskette drive.                                                                                                                                                                |  |

| 5                | Power On/Off button  | Turns AC power on and off.                                                                                                                                                                                                   |  |

| 6                | Halt/Reset button    | When set to Halt, this button is operating-<br>system-specific. See your operating system<br>documentation. When set to Reset (default),<br>this button resets the system and causes the<br>self test to run.                |  |

| 7                | Indicators           | <ul> <li>Indicators from top to bottom are as follows:</li> <li>Power. Lights when the system is on.</li> <li>Hard disk drive. Lights when a hard disk drive is in use.</li> <li>The lower indicator is not used.</li> </ul> |  |

Table 1-4. AlphaStation 400 Series Controls and Indicators

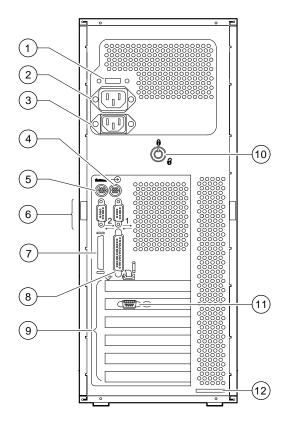

Figure 1-4. AlphaStation 400 Series Rear Connectors

| Figure<br>Legend | Connector                     | Function                                                                                                                                                            |

|------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | Voltage selector switch       | Allows you to set your system to work with 115-<br>Volt or 230-Volt AC power.                                                                                       |

| 2                | Monitor power connector       | Use to connect a monitor to AC power. If your<br>monitor consumes more than 2 Amps at 115<br>Volts(1 Amp at 230 Volts), connect it directly to<br>your wall outlet. |

| 3                | AC power connector            | Use to connect the system to AC power.                                                                                                                              |

| 4                | Mouse connector               | Use to connect a PS/2-compatible mouse.                                                                                                                             |