# DWLPA and DWLPB PCI Adapter Technical Manual

Order Number: EK-DWLPX-TM. A01

DWLPA and DWLPB are PCI adapters (PCIA) developed for the AlphaServer I/O subsystems. The adapters include a PCI to EISA bridge that generates an EISA bus from the PCIA. The PCIA connects to TLSB based systems through an I/O port module.

digital equipment corporation maynard, massachusetts

#### **First Printing, July 1996**

Digital Equipment Corporation makes no representations that the use of its products in the manner described in this publication will not infringe on existing or future patent rights, nor do the descriptions contained in this publication imply the granting of licenses to make, use, or sell equipment or software in accordance with the description.

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation.

Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software, if any, described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license. No responsibility is assumed for the use or reliability of software or equipment that is not supplied by Digital Equipment Corporation or its affiliated companies.

Copyright © 1996 by Digital Equipment Corporation.

All Rights Reserved. Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation: AlphaGeneration, AlphaServer, DEC, DECchip, DEC LANcontroller, OpenVMS, StorageWorks, VAX, the AlphaGeneration logo, and the DIGITAL logo.

MEMORY CHANNEL is a trademark of Encore Computer Corporation.

**FCC NOTICE:** The equipment described in this manual generates, uses, and may emit radio frequency energy. The equipment has been type tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such radio frequency interference when operated in a commercial environment. Operation of this equipment in a residential area may cause interference, in which case the user at his own expense may be required to take measures to correct the interference.

# Contents

| Preface | ix |

|---------|----|

|---------|----|

## Chapter 1 Overview

| Applicable Documents         | 1-1                                                                                                                                                            |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Features                     | 1-1                                                                                                                                                            |

| TLSB I/O General Description | 1-2                                                                                                                                                            |

| PCIA General Description     |                                                                                                                                                                |

| Communication Overview       | 1-5                                                                                                                                                            |

| DMA Transactions             | 1-5                                                                                                                                                            |

| Mailbox Transactions         | 1-6                                                                                                                                                            |

| CSR Transactions             | 1-6                                                                                                                                                            |

| Interrupt Transactions       | 1-7                                                                                                                                                            |

|                              | Features<br>TLSB I/O General Description<br>PCIA General Description<br>Communication Overview<br>DMA Transactions<br>Mailbox Transactions<br>CSR Transactions |

## Chapter 2 Addressing

| 2.1     | TLSB System Addressing         |  |

|---------|--------------------------------|--|

| 2.2     | System Bus to PCI Addressing   |  |

| 2.2.1   | PCI Memory Space               |  |

| 2.2.1.1 | Dense Mapping                  |  |

| 2.2.1.2 | Sparse Mapping                 |  |

| 2.2.2   | PCI I/O Space                  |  |

| 2.2.3   | PCI Configuration Space        |  |

| 2.2.3.1 | PCIA CSR and Map RAM Space     |  |

| 2.2.3.2 | EISA Subtractive Decode Window |  |

| 2.2.3.3 | PCIA Reserved Addresses        |  |

| 2.3     | PCI to System Bus Addressing   |  |

| 2.3.1   | PC Compatibility Holes         |  |

| 2.3.2   | DMA Address Windows            |  |

|         |                                |  |

## Chapter 3 Registers

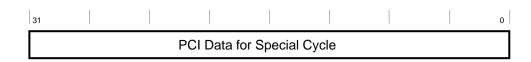

| SCYCLE — PCIA Special Cycle Register                                                                                                                                                              | 3-5  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

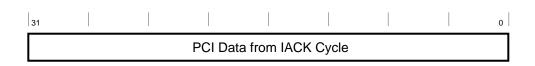

| IACK — PCIA Interrupt Acknowledge Register                                                                                                                                                        | 3-6  |

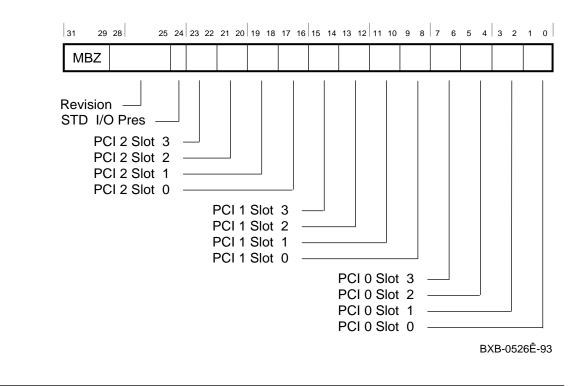

| PRESENT — PCIA Slot Present Register                                                                                                                                                              | 3-7  |

|                                                                                                                                                                                                   |      |

| MCTL — PCIA Module Control Register                                                                                                                                                               |      |

| IBR — PCIA Information Base Repair Register                                                                                                                                                       | 3-12 |

| CTLx — PCIx Bus Control Register                                                                                                                                                                  | 3-13 |

| MRETRYx — PCIx Master Retry Limit Register                                                                                                                                                        | 3-16 |

| GPRx — PCIx General Purpose Register                                                                                                                                                              | 3-17 |

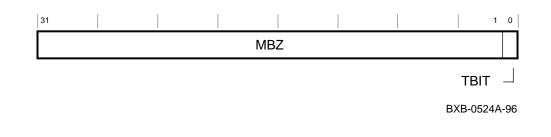

| TBIT — PCIA TBIT Register<br>MCTL — PCIA Module Control Register<br>IBR — PCIA Information Base Repair Register<br>CTLx — PCIx Bus Control Register<br>MRETRYx — PCIx Master Retry Limit Register |      |

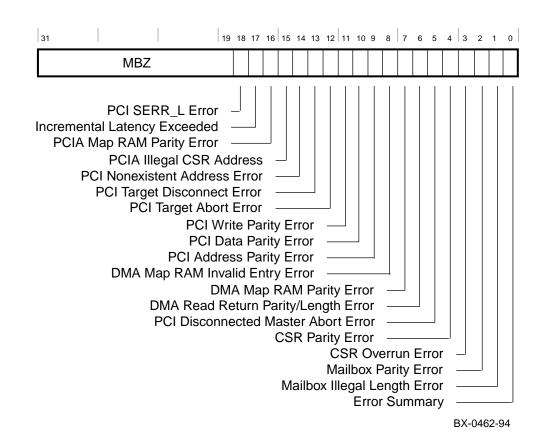

| ERRx — PCIx Error Summary Register             |

|------------------------------------------------|

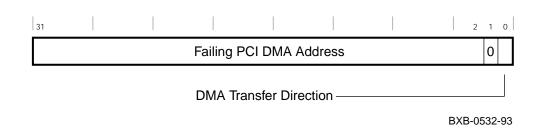

| FADRx — PCIx Failing Address Register          |

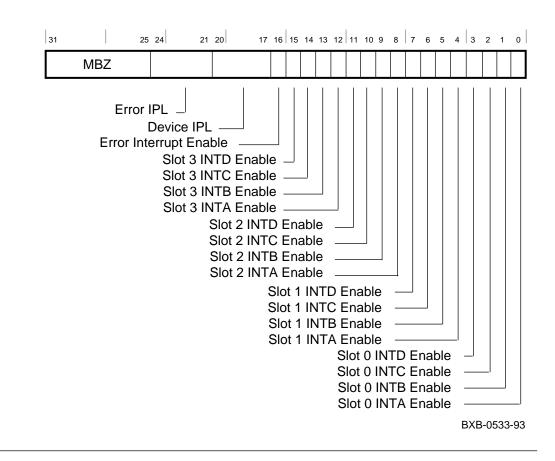

| IMASKx — PCIx Interrupt Mask Register          |

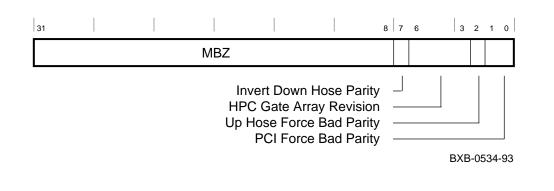

| DIAGx — PCIx Diagnostic Register               |

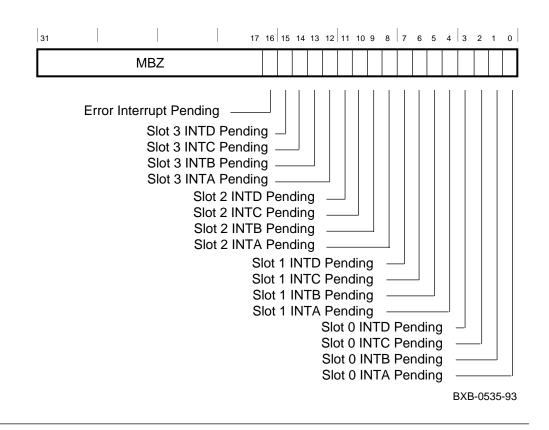

| IPENDx — PCIx Interrupt Pending Register       |

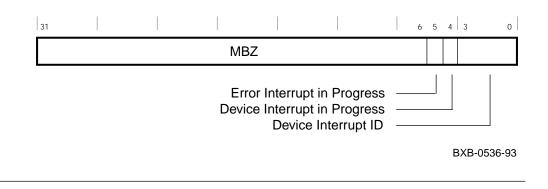

| IPROGx — PCIx Interrupt in Progress Register   |

| WMASK_xx — PCIx Window Mask Registers          |

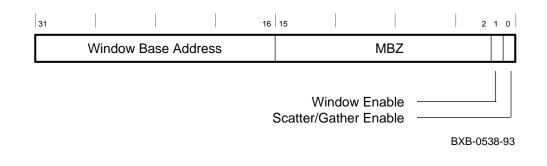

| WBASE_xx — PCIx Window Base Registers          |

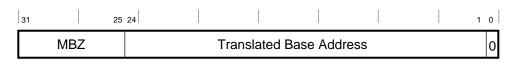

| TBASE_xx — PCIx Translated Base Registers      |

| ERRVEC - PCIx Error Interrupt Vector Registers |

| Scatter/Gather RAM Map Entry Format            |

# Chapter 4 Functional Description

| 4.1      | PCI Interface                                           |

|----------|---------------------------------------------------------|

| 4.1.1    | CPU-Initiated PCI Cycles 4-1                            |

| 4.1.1.1  | CPU-Initiated PCI Commands 4-1                          |

| 4.1.1.2  | PCI Addressing 4-2                                      |

| 4.1.1.3  | CPU Command Decode 4-4                                  |

| 4.1.1.4  | CPU Request Queue 4-4                                   |

| 4.1.1.5  | Requesting PCI Bus 4-4                                  |

| 4.1.1.6  | Default Bus Parking 4-5                                 |

| 4.1.1.7  | Address Phase 4-5                                       |

| 4.1.1.8  | Data Phase                                              |

| 4.1.1.9  | Transaction Termination 4-6                             |

| 4.1.1.10 | Exclusive Access Support 4-7                            |

| 4.1.2    | Device-Initiated PCI Cycles 4-7                         |

| 4.1.2.1  | Device-Initiated PCI Commands 4-7                       |

| 4.1.2.2  | PCI Memory Read Multiple Command 4-8                    |

| 4.1.2.3  | PCI Address Decode 4-9                                  |

| 4.1.2.4  | PCI Address Translation 4-9                             |

| 4.1.2.5  | Address Queuing 4-10                                    |

| 4.1.2.6  | Address Phase 4-10                                      |

| 4.1.2.7  | Address Burst Order 4-11                                |

| 4.1.2.8  | Memory Block Boundary 4-11                              |

| 4.1.2.9  | Address Parity Errors 4-11                              |

| 4.1.2.10 | Write Data Transfers 4-11                               |

| 4.1.2.11 | Read Data Transfers                                     |

| 4.1.2.12 | PCI Target Latency Timeout 4-13                         |

| 4.1.2.13 | Device-Initiated Exclusive Access 4-13                  |

| 4.2      | Hose Interface                                          |

| 4.2.1    | Down Hose 4-14                                          |

| 4.2.1.1  | Down Hose Commands 4-14                                 |

| 4.2.1.2  | Down Hose to PCI Synchronization 4-14                   |

| 4.2.1.3  | Down Hose Signals4-15                                   |

| 4.2.2    | Up Hose                                                 |

| 4.2.2.1  | Up Hose Commands 4-15                                   |

| 4.2.2.2  | Up Hose Arbitration                                     |

| 4.2.2.3  | Up Hose Command FIFO 4-17                               |

| 4.2.2.4  | Up Hose Signals 4-18                                    |

| 4.2.2.5  | Map RAM Structure                                       |

| 4.2.2.6  | Special Programming Considerations for the Up Hose 4-19 |

| 4.2.3    | Serial EEPROM                                           |

| 4.2.4    | PCI to EISA Bridge Hardware                             |

| 4.2.5    | CPU-Initiated Transactions                              |

| 4.2.6   | DMA Transactions                |  |

|---------|---------------------------------|--|

| 4.3     | PCIA Interrupts                 |  |

| 4.3.1   | PCI Interrupts                  |  |

| 4.3.1.1 | PCI Device Interrupts           |  |

| 4.3.1.2 | PCI Error Interrupts            |  |

| 4.3.2   | Hose Interrupt Support          |  |

| 4.3.3   | Vectored Interrupts             |  |

| 4.3.3.1 | PCI Device Interrupts           |  |

| 4.3.3.2 | PCI Error Interrupts            |  |

| 4.3.3.3 | Masking PCI Interrupts          |  |

| 4.3.3.4 | EISA Interrupts                 |  |

| 4.3.4   | Diagnostic Features             |  |

| 4.3.4.1 | Interrupt Pending Registers     |  |

| 4.3.4.2 | Interrupt in Progress Registers |  |

|         |                                 |  |

## Chapter 5 Error Handling

| 5.1  | Error Categories                    | 5-1 |

|------|-------------------------------------|-----|

| 5.2  | Down Hose Header Cycle Parity Error | 5-1 |

| 5.3  | Mailbox Errors                      | 5-2 |

| 5.4  | CSR Command Errors                  |     |

| 5.5  | DMA Errors                          | 5-2 |

| 5.6  | PCI Errors                          | 5-4 |

| 5.7  | PCIA Errors                         | 5-5 |

| 5.8  | Up Hose Packet Count Error          | 5-6 |

| 5.9  | PCI Peer-to-Peer Errors             | 5-6 |

| 5.10 | PCI Configuration Errors            | 5-6 |

|      |                                     |     |

## Chapter 6 PCI to EISA Bridge

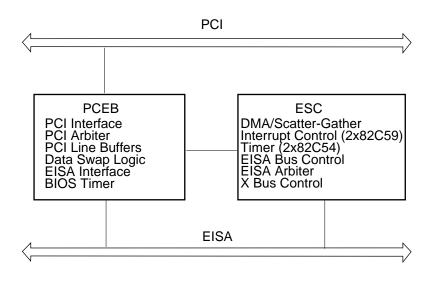

| 6.1   | PCI and EISA Subsystem Block Diagram | 6-1 |

|-------|--------------------------------------|-----|

| 6.2   | PCI-EISA Bridge Chipset              |     |

| 6.3   | Address Mapping                      |     |

| 6.3.1 | PCI to EISA                          |     |

| 6.3.2 | EISA to PCI                          |     |

| 6.4   | Bridge Buffers                       | 6-4 |

| 6.5   | Interrupts                           |     |

| 6.6   | EISA Bus Lock                        | 6-5 |

| 6.7   | Lockout Prevention                   | 6-6 |

| 6.8   | Configuration Rules                  |     |

| 6.9   | EISA Bridge Registers                | 6-7 |

## Appendix A PCIA Supported Hose Packets

| A.1 | Down Hose Packets | A- | 1 |

|-----|-------------------|----|---|

| A.2 | Up Hose Packets   | A- | 8 |

## Figures

| 1-1 | I/O System Block Diagram    | 1-2 |

|-----|-----------------------------|-----|

|     | PCIA Module Physical Layout |     |

|     | PCIA Module Block Diagram   |     |

| 2-1  | CPU View of PCI Addresses                                      | 2-3  |

|------|----------------------------------------------------------------|------|

| 2-2  | CPU to PCI Address Mapping                                     | 2-4  |

| 2-3  | Dense Space Address Mapping                                    | 2-5  |

| 2-4  | Sparse Space Address Mapping (Lower 16 Mbytes)                 |      |

| 2-5  | Sparse Space Address Mapping (Upper 112 Mbytes)                | 2-7  |

| 2-6  | PCI Configuration Space Addressing - Type 0 Addresses          | 2-9  |

| 2-7  | PCI Configuration Space - Type 1 Address Fields                | 2-12 |

| 2-8  | PCI Device View of System Address Space                        |      |

| 2-9  | PCI Memory Space, Including Compatibility Holes                | 2-15 |

|      | Direct DMA Address Translation                                 |      |

| 2-11 | Mapped DMA Address Translation for DWLPA and DWLPB with TBIT=0 | 2-17 |

| 2-12 | Mapped DMA Address Translation for DWLPB with TBIT=1           | 2-18 |

| 4-1  | INTR/IDENT Packet                                              | 4-23 |

| 4-2  | Interrrupt Status Return Packet                                | 4-24 |

| 6-1  | PCI and EISA Subsystem                                         |      |

| 6-2  | PCI-EISA Bridge Chip Function                                  | 6-3  |

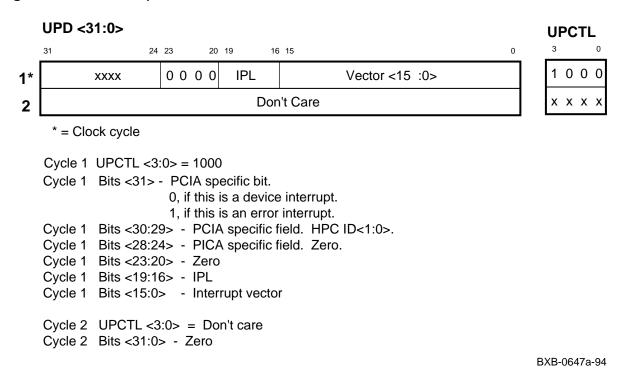

| A-1  | Interrupt Status Return Packet                                 | A-1  |

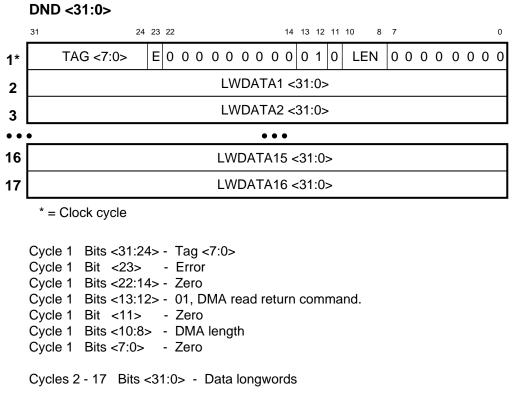

| A-2  | DMA Read Data Return Packet                                    | A-2  |

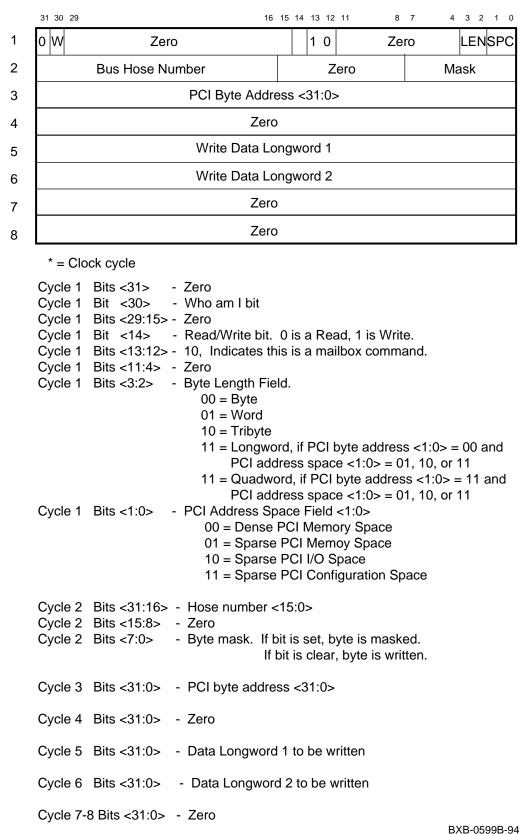

| A-3  | Mailbox Command Packet                                         | A-3  |

| A-4  | CSR Sparse Read Packet                                         | A-4  |

| A-5  | CSR Sparse Write Packet                                        | A-5  |

| A-6  | CSR Dense Read Packet                                          |      |

| A-7  | CSR Dense Write Packet                                         |      |

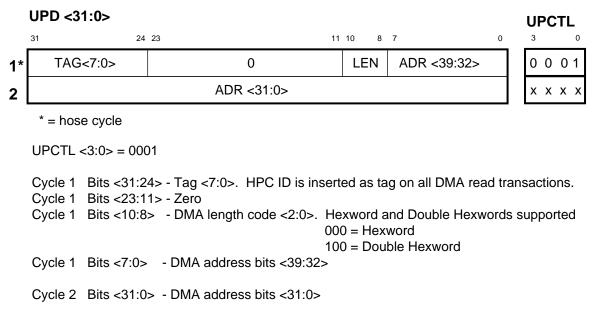

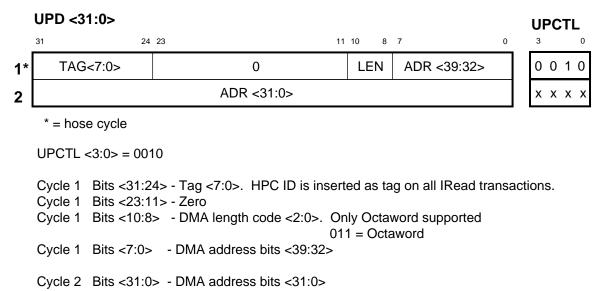

| A-8  | DMA Read Packet                                                |      |

| A-9  | IREAD Packet                                                   |      |

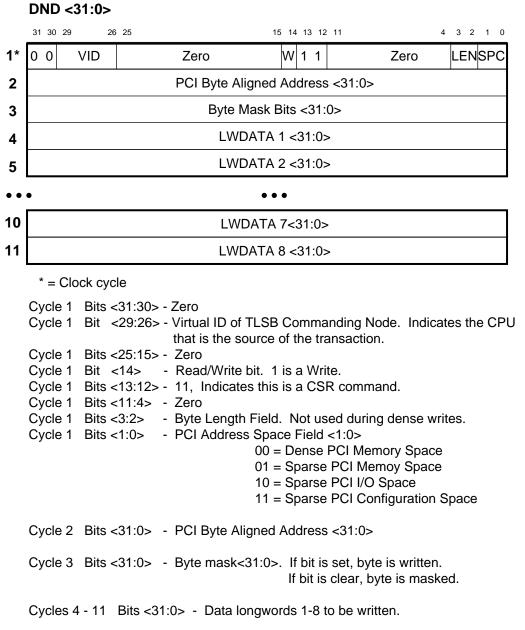

|      | DMA Write Mask Packet                                          |      |

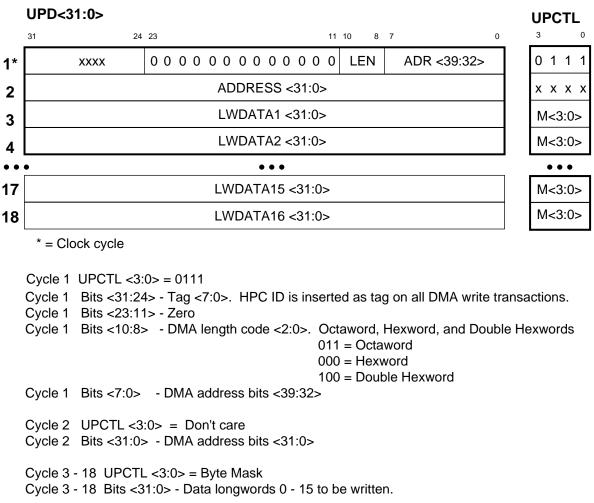

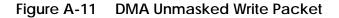

| A-11 | DMA Unmasked Write Packet                                      | A-10 |

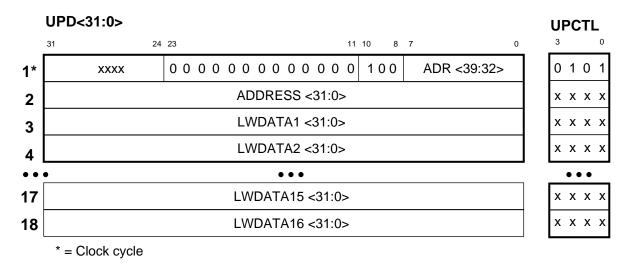

|      | Mailbox Status Return Packet                                   |      |

| A-13 | Interrupt/IDENT Packet                                         | A-11 |

|      | CSR Sparse Read Return Packet                                  |      |

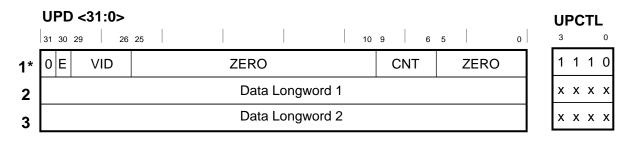

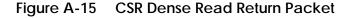

|      | CSR Dense Read Return Packet                                   |      |

| A-16 | CSR Write Status Return Packet                                 | A-13 |

## Tables

| 1    | AlphaServer 8200 and 8400 Documentation                  | X   |

|------|----------------------------------------------------------|-----|

| 2    | Related Documents                                        | xii |

| 2-1  | TLSB Address Map                                         |     |

| 2-2  | I/O Node Space Assignment                                |     |

| 2-3  | CPU to PCI Address Mapping for a Single PCIA             |     |

| 2-4  | Sparse Access Encoding - PCI Memory Space                |     |

| 2-5  | Sparse Access Encoding - PCI I/O Space                   |     |

| 2-6  | PCI Configuration Space - Type 0 Address Fields          |     |

| 2-7  | Type 0 Configuration Space Address Map                   |     |

| 2-8  | PCI Configuration Space Addressing - Type 1 Address Bits |     |

| 2-9  | PCIA CSR and Map RAM Address Space                       |     |

| 2-10 |                                                          |     |

| 3-1  | PCIA Registers                                           |     |

| 3-2  | Register Bit Types                                       |     |

| 3-3  | SCYCLE Register Bit Definitions                          |     |

| 3-4  | IACK Register Bit Definitions                            |     |

| 3-5  | PRESENT Register Bit Definitions                         |     |

| 3-6  | TBIT Register Bit Definitions                            |     |

| 3-7  | MCTL Register Bit Definitions                            |     |

| 3-8  | IBR Register Bit Definitions                             |     |

| 3-9  | CTLx Register Bit Definitions                                   | 3-13 |

|------|-----------------------------------------------------------------|------|

| 3-10 | MRETRYx Register Bit Definitions                                | 3-16 |

| 3-11 | GPRx Register Bit Definitions                                   | 3-17 |

| 3-12 | ERRx Register Bit Definitions                                   | 3-19 |

| 3-13 | FADRx Register Bit Definitions                                  | 3-21 |

| 3-14 | IMASKx Register Bit Definitions                                 | 3-23 |

| 3-15 | DIAGx Register Bit Definitions                                  | 3-25 |

| 3-16 | IPENDx Register Bit Definitions                                 | 3-28 |

| 3-17 | IPROGx Register Bit Definitions                                 | 3-30 |

| 3-18 | WMASK_xx Register Bit Definitions                               | 3-31 |

| 3-19 | WBASE_xx Register Bit Definitions                               | 3-32 |

| 3-20 | TBASE_xx Register Bit Definitions                               | 3-33 |

| 3-21 | ERRVEC Register Bit Definitions                                 | 3-34 |

| 3-22 | PCI Interrupt Vector Offsets                                    | 3-35 |

| 3-23 | Scatter/Gather Map Entry Format                                 | 3-36 |

| 4-1  | Supported PCI Commands                                          | 4-1  |

| 4-2  | CPU Address to PCI Address Conversion                           |      |

| 4-3  | Supported PCI Target Commands                                   | 4-7  |

| 4-4  | Down Hose Commands                                              |      |

| 4-5  | Down Hose Signals                                               | 4-15 |

| 4-6  | Up Hose Commands                                                | 4-15 |

| 4-7  | Up Hose Packet Status                                           | 4-16 |

| 4-8  | Command Signal Assertion                                        | 4-17 |

| 4-9  | Up Hose Signals                                                 | 4-18 |

| 4-10 | Map RAM Logic Command4                                          | 4-19 |

| 4-11 | PCI Interrupt Priority with and without the Standard I/O Module | 4-25 |

|      | Interrupt Pending Register Bit Definitions                      |      |

| 6-1  | PCI to EISA Address Mapping                                     | 6-3  |

| 6-2  | EISA Bridge and Standard I/O Interrupt Connections              |      |

| 6-3  | Standard I/O EISA Interrupt Assignments                         |      |

| 6-4  | Slot Usage with Standard I/O Module Installed                   | 6-6  |

### **Intended Audience**

This manual describes the hardware of the PCI I/O subsystem in AlphaServer 8200 and 8400 systems. It discusses the operations of the DWLPA and DWLPB PCI adapters, and provides detailed information on the subsystem registers. The manual is intended for technical professionals such as operating system programmers and customer service engineers.

### **Document Structure**

This manual has six chapters and one appendix:

- Chapter 1, Overview, gives an overview of the PCIA adapter.

- **Chapter 2**, **Addressing**, describes system to PCI and PCI to system addressing schemes.

- Chapter 3, Registers, describes each register in the PCIA.

- **Chapter 4, Functional Description,** discusses CPU and PCI commands and transactions in detail.

- **Chapter 5, Error Handling,** describes errors caused during subsystem operations.

- Chapter 6, PCI to EISA Bridge, describes the PCI to EISA bridge.

- **Appendix A, PCIA Supported Hose Packets**, shows the supported Up and Down Hose data packets.

## **Documentation Titles**

Table 1 lists the books in the Digital AlphaServer 8200 and 8400 documentation set. Table 2 lists other documents that you may find useful.

| Table 1 | AlphaServer 8200 and 8400 Documentation |

|---------|-----------------------------------------|

|---------|-----------------------------------------|

| Title                                          | Order Number                              |  |  |  |

|------------------------------------------------|-------------------------------------------|--|--|--|

| Hardware User Information and Installation     |                                           |  |  |  |

| Operations Manual                              | EK-T8030-OP                               |  |  |  |

| Site Preparation Guide                         | EK-T8030-SP                               |  |  |  |

| AlphaServer 8200 Installation Guide            | EK-T8230-IN                               |  |  |  |

| AlphaServer 8400 Installation Guide            | EK-T8430-IN                               |  |  |  |

| Service Information Kit                        | QZ-00RAC-GC                               |  |  |  |

| Service Manual (hard copy)                     | EK-T8030-SV                               |  |  |  |

| Service Manual (diskettes)                     | AK–QKNFA–CA<br>AK–QUW7A–CA<br>AK–QUW6A–CA |  |  |  |

| Reference Manuals                              |                                           |  |  |  |

| System Technical Manual                        | ЕК-Т8030-ТМ                               |  |  |  |

| System Technical Manual Supplement             | EK-T8030-TS                               |  |  |  |

| DWLPA/DWLPB PCI Adapter Technical Manual       | EK-DWLPX-TM                               |  |  |  |

| Upgrade Manuals for Both Systems               |                                           |  |  |  |

| KN7CC CPU Installation Card                    | EK-KN7CC-IN                               |  |  |  |

| KN7CD CPU Installation Card                    | EK-KN7CD-IN                               |  |  |  |

| KN7CE CPU Installation Card                    | EK-KN7CE-IN                               |  |  |  |

| MS7CC Memory Installation Card                 | EK-MS7CC-IN                               |  |  |  |

| KFTHA System I/O Module Installation Guide     | EK-KFTHA-IN                               |  |  |  |

| KFTIA Integrated I/O Module Installation Guide | EK-KFTIA-IN                               |  |  |  |

| Title                                           | Order Number |

|-------------------------------------------------|--------------|

| Upgrade Manuals: 8400 System Only               |              |

| AlphaServer 8400 Upgrade Manual                 | EK-T8430-UI  |

| BA654 DSSI Disk PIU Installation Guide          | EK-BA654-IN  |

| BA655 SCSI Disk and Tape PIU Installation Guide | EK-BA655-IN  |

| DWLAA Futurebus+ PIU Installation Guide         | EK-DWLAA-IN  |

| DWLMA XMI PIU Installation Guide                | EK-DWLMA-IN  |

| DWLPA/DWLPB PCI PIU Installation Guide          | EK-DWL84-IN  |

| H7237 Battery PIU Installation Guide            | EK-H7237-IN  |

| H7263 Power Regulator Installation Card         | EK-H7263-IN  |

| KFMSB Adapter Installation Guide                | EK-KFMSB-IN  |

| KZMSA Adapter Installation Guide                | EK-KXMSX-IN  |

| RRDCD Installation Guide                        | EK-RRDRX-IN  |

| Upgrade Manuals: 8200 System Only               |              |

| DWLPA/DWLPB PCI Shelf Installation Guide        | EK-DWL82-IN  |

| H7266 Power Regulator Installation Card         | EK-H7266-IN  |

| H7267 Battery Backup Installation Card          | EK-H7267-IN  |

Table 1 AlphaServer 8200 and 8400 Documentation (Continued)

### Table 2 Related Documents

| Title                                                                                             | Order Number |

|---------------------------------------------------------------------------------------------------|--------------|

| General Site Preparation                                                                          |              |

| Site Environmental Preparation Guide                                                              | EK-CSEPG-MA  |

| System I/O Options                                                                                |              |

| BA350 Modular Storage Shelf Subsystem<br>Configuration Guide                                      | EK-BA350-CG  |

| BA350 Modular Storage Shelf Subsystem<br>User's Guide                                             | EK-BA350-UG  |

| BA350-LA Modular Storage Shelf User's Guide                                                       | EK-350LA-UG  |

| CIXCD Interface User Guide                                                                        | EK-CIXCD-UG  |

| DEC FDDIcontroller 400 Installation/Problem Solving                                               | EK-DEMFA-IP  |

| DEC FDDIcontroller/Futurebus+ Installation Guide                                                  | EK-DEFAA-IN  |

| DEC FDDIcontroller/PCI User Information                                                           | EK-DEFPA-IN  |

| DEC LANcontroller 400 Installation Guide                                                          | EK-DEMNA-IN  |

| DSSI VAXcluster Installation/Troubleshooting Manual                                               | EK-410AA-MG  |

| EtherWORKS Turbo PCI User Information                                                             | EK-DE435-OM  |

| KZPSA PCI-to-SCSI Storage Adapter User's Guide                                                    | EK-KZPSA-UG  |

| RF Series Integrated Storage Element User Guide                                                   | EK-RF72D-UG  |

| StorageWorks RAID Array 200 Subsystem Family<br>Installation and Configuration Guide              | EK-SWRA2-IG  |

| StorageWorks RAID Array 200 Subsystem Family<br>Software User's Guide for OpenVMS AXP             | AA-Q6WVA-TE  |

| <i>StorageWorks RAID Array 200 Subsystem Family</i><br><i>Software User's Guide for DEC OSF/1</i> | AA-Q6TGA-TE  |

| Operating System Manuals                                                                          |              |

| Alpha Architecture Reference Manual                                                               | EY-L520E-DP  |

| DEC OSF/1 Guide to System Administration                                                          | AA-PJU7A-TE  |

| Guide to Installing DEC OSF/1                                                                     | AA-PS2DE-TE  |

| <i>OpenVMS Alpha Version 6.2 Upgrade and Installation Manual</i>                                  | AA-PV6XC-TE  |

| MEMORY CHANNEL Manuals                                                                            |              |

| Memory Channel User's Guide                                                                       | EK-PCIRM-UG  |

| Memory Channel Service Information                                                                | EK-PCIRM-SV  |

# **Chapter 1**

## **Overview**

The PCI adapter (PCIA) module provides a complete PCI and EISA bus subsystem for systems that implement the TLSB I/O hose interface.

### **1.1** Applicable Documents

- Intel 82420/82430 PCIset ISA and EISA Bridges Databook (April 1993)

- AlphaServer 8200 and 8400 documentation

- AlphaServer 2100 documentation

### 1.2 Features

**Software Compatibility** - The PCIA is architecturally compatible with other CPU-PCI, and PCI-EISA bridges, allowing software drivers to run on the TLSB platforms with no modifications.

**Hardware Compatibility** - The PCIA supports the TLSB hose protocol. Direct CSR access to the PCI bus is allowed on the TLSB.

**Configurability** - As seen from the CPU, the three PCI buses on the PCIA share a common I/O address space. Therefore, flexible address space assignments meet varying I/O card address space requirements. There are 12 PCI expansion slots plus one slot for the EISA bridge.

**Scatter/Gather Capability** - The DWLPA supports a 32K entry scatter/gather address map RAM used to translate PCI memory addresses into TLSB main memory addresses. DWLPB supports a 128K entry map RAM.

**Performance** - To improve the individual DMA transaction performance, the PCIA implements an on-chip scatter/gather cache and reads of a full host memory block. To improve overall DMA throughput, the PCIA implements three physically separate PCI buses and allows a DMA operation to be pending simultaneously for each bus.

**EISA Support** - A dedicated slot is used to support a PCI-EISA bus bridge module (KFE70), which provides access to an 8-slot EISA bus. This module is the standard I/O module used on AlphaServer 8200 and 8400 systems. The EISA bridge includes an Intel 8242 keyboard/mouse controller, for operating systems that require an integrated keyboard. The module also provides a PC-style floppy disk port and PCI-based Ethernet.

**Self-Test** - The PCIA does not implement an on-board self-test. However, the host CPU diagnoses the module.

**Cache Coherency** - The PCIA does not support any of the PCI cache coherency mechanisms required to maintain coherency between TLSB main memory and memory located on the PCI.

**Memory Locks** - Since the TLSB system buses do not provide locks, only a single, limited case of PCI locking is supported.

**PCI Addressing** - The PCIA does not support the 64-bit addressing mode or the 64-bit data path of the PCI bus.

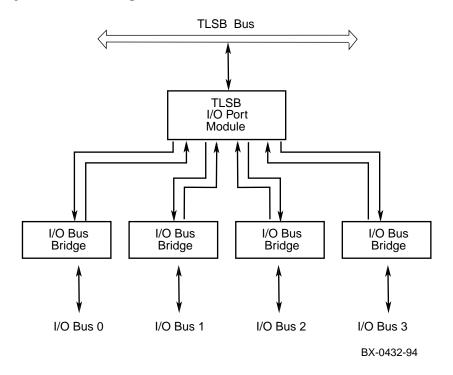

## 1.3 **TLSB I/O General Description**

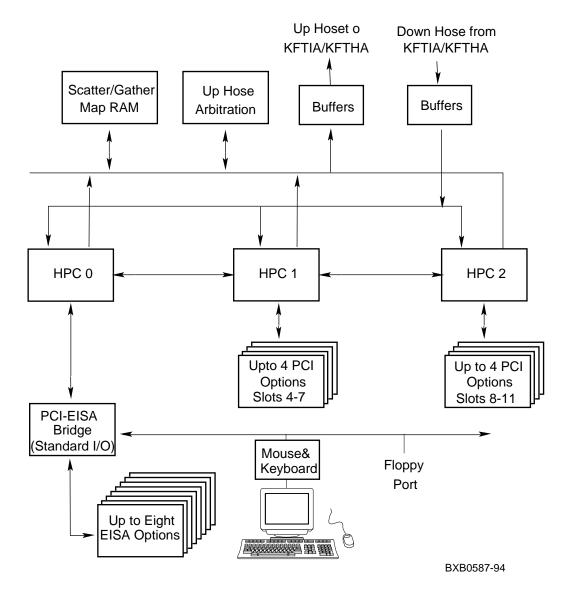

TLSB systems consist of processor modules, memory modules, and I/O port modules, as shown in Figure 1-1. Each I/O module (KFTIA/KFTHA) supports from 1 to 4 bridges to a remote I/O bus such as XMI, Futurebus+, or PCI. The bus bridge, which includes the backplane for the PCI/EISA devices, is housed in a plug-in unit (PIU) in the 8400 or in a PCI shelf in the 8200. The bridge is connected to the I/O port module by a pair of cables called a hose. One cable of the pair carries data and control to the bridge (the Down Hose), and the other carries traffic from the bridge (the Up Hose).

The I/O module converts between transactions on the system bus and hose data packets as interpreted by the I/O bridges. The remote bus address spaces are made visible to the CPU through either I/O mailboxes (XMI and Futurebus+) or as a direct CSR space (PCI). The I/O module does not attempt to maintain coherency between system memory and any memory on its I/O adapters.

Figure 1-1 I/O System Block Diagram

## 1.4 PCIA General Description

The PCI bus bridge is located on the PCIA. From the CPU viewpoint, the PCI side of the bridge appears as a single, logical PCI bus. The bus supports up to 15 PCI devices. Some of these devices can be placed in the 12 PCI expansion slots on the PCIA motherboard. Others are embedded PCI options on the PCI-EISA bridge module (also called the standard I/O module). From the CPU, the logical PCI appears to have one set of address spaces.

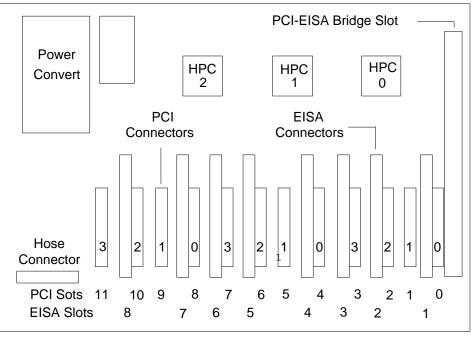

For electrical and performance reasons, the logical PCI is implemented as three physical PCI buses. Adjacent groups of four devices are physically on the same PCI segment and can communicate as peers. The 12 PCI expansion slots are divided evenly, with 4 slots on each physical bus. Each bus operates at 33 MHz and supports a 32-bit data path and 32-bit addresses, for a raw bus bandwidth of 120 Mbytes/sec. Figure 1-2 shows the physical layout of the PCIA module.

The PCI-EISA bridge (standard I/O module) occupies a special slot on one of the physical buses and when installed all of the slots of that physical segment are dedicated to the EISA bus. Eight of the expansion slots include two sets of connectors and can be used for either PCI or EISA modules. The bridge is implemented using the Intel PCEB/ESC (Mercury) chipset and provides a single 33 Mbyte/sec EISA bus using the 8 slots with EISA connectors.

#### Figure 1-2 PCIA Module Physical Layout

BX0433A-95

The PCIA provides access to all three PCI address spaces: memory space, I/O space, and configuration space. All are accessible using sparse address

mapping that allows for byte access. PCI memory space is also accessible by dense mapping that supports cache block sized bursts.

From the system bus side of the PCIA, a single logical PCI with one set of address spaces is seen. This logical view exists only from the CPU. From the PCI side of the PCIA, three physical PCI bus segments exist. Individual PCI bus masters see only the address spaces local to their physical PCI segment. PCI devices on the same physical bus communicate as peers without involving the PCIA. All three segments normally are configured to see the same view of system memory.

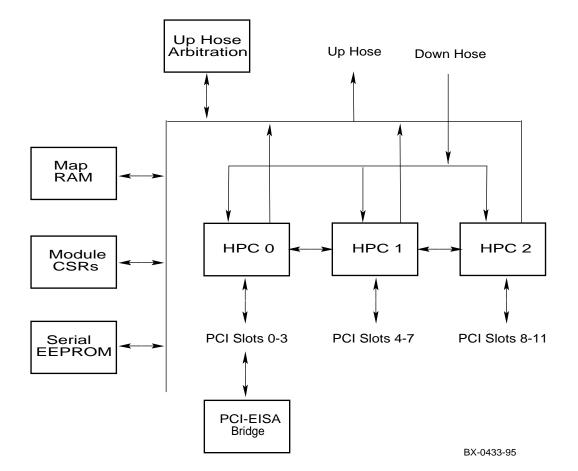

Each of the three physical PCI bus segments is controlled by a PCI bus interface gate array (HPC). Down Hose data from the KFTIA/KFTHA is sent to each of the HPCs in parallel. Up Hose data is driven by each HPC over a tristate bus, UP\_BUS<31:0>, to a driver which transmits the data on to the Up Hose. Each HPC arbitrates for the use of the UP\_BUS when sending packets over the Up Hose. The UP\_BUS also provides access to the scatter/gather map RAM and some module-level control registers. Each HPC has 16 PCI interrupt inputs, which it prioritizes and sends to the KFTIA/KFTHA. Each HPC monitors UP\_BUS transactions to maintain a consistent count of the number of transactions that the PCIA has outstanding. Figure 1-3 shows the PCIA module block diagram.

The EISA bus bridge provides decoding for an 8-bit XBUS, which supports PC-style floppy, keyboard, and mouse ports on an additional connector module. The module also includes an Ethernet port. Support for these peripherals is operating system dependent. Refer to the *AlphaServer 2100 and 2200 I/O Specification* for additional information.

#### Figure 1-3 PCIA Module Block Diagram

The PCIA motherboard and EISA bridge modules, the standard I/O module and the connector module, mount in an enclosure that provides the card cage for the PCI and EISA option modules. The enclosure is the same form factor as a StorageWorks shelf and mounts in a modified version of a plug-in unit or a rackmount shelf.

### **1.5** Communication Overview

The PCIA hardware communicates with the I/O port using four types of transactions: DMA, mailbox, CSR, and interrupt.

#### 1.5.1 DMA Transactions

All DMA transactions access the PCIA as a PCI target. PCI memory transactions are forwarded to the I/O port if they access one of the address ranges specified by a set of DMA window registers. If required, the PCI DMA address is translated to a system memory address by scatter/gather address mapping. The PCIA can generate DMA read and masked/unmasked write transactions to the I/O port. The PCIA responds to multiple PCI memory read transactions by prefetching a programmable number of cache blocks. The PCIA generates an interlocked read transaction to the I/O port in response to a PCI DMA read with PCI lock asserted. DMA write transactions are received from the PCI in a store and forward manner. The PCIA generates masked octaword or hexword writes, or unmasked double hexword writes to the I/O port. Each HPC contains two PCI DMA write buffers allowing one transaction's write data to be transferred over the Up Hose while another PCI DMA command is being received from the PCI bus. All DMA read transactions are the size of the system memory block. Memory block sizes of 32 and 64 bytes are supported. DMA read commands sent to the I/O port are tagged with an HPC ID code. Read return data received over the Down Hose bus is identified by its tag and buffered by the appropriate HPC. Each HPC contains one 64-byte read return buffer. The buffer is filled from the hose until a cut-through threshold is reached, at which point the HPC begins transferring data on the PCI. The PCI transfer proceeds in parallel with the remainder of the hose transfer.

#### 1.5.2 Mailbox Transactions

All mailbox transactions are executed by the PCIA hardware as a PCI master. Mailbox transactions forwarded from the I/O port can access a PCI I/O card on the PCI bus, a PCIA CSR, or the map RAM. Mailbox transactions to PCI memory or I/O space on the PCI bus are sent to all three PCI buses, but only one bus responds to the transaction.

Mailbox transactions are byte, word, tribyte, longword, or quadword in length. A Mailbox Command packet is received by the PCIA on the Down Hose. Each of the HPCs decodes the command although only one will execute it. After executing the mailbox read or write command, the executing HPC returns a Mailbox Status packet to the I/O port over the Up Hose. Data is included in the Up Hose packet if the command was a mailbox read.

Mailbox transactions are used for diagnostic and initialization purposes. Although the PCIA can buffer up to four mailbox transactions, it can execute only one transaction at a time. The I/O port sends one mailbox transaction at a time to the PCIA.

#### 1.5.3 CSR Transactions

All CSR commands are issued by the CPU and the transactions are executed by the PCIA as a PCI master. CSR transactions can access a location on the PCI bus, a PCIA CSR, or the map RAM. CSR transactions to PCI memory or I/O space on the PCI bus are sent to all three PCI buses, with only one bus actually responding to the transaction.

CSR transactions are byte, word, tribyte, longword, quadword, or hexword in length. Byte, word, tribyte, longword, and quadword transfers are supported through a sparse CPU-to-PCI address mapping. Hexword transfers are supported through dense CPU-to-PCI address mapping. Byte, word, tribyte, and longword transfers result in a PCI cycle burst length of one. Quadword transfers result in a PCI cycle burst length of two. Hexword transfers result in a PCI cycle burst length of two. Hexword transfers result in a PCI cycle burst length of eight. See Chapter 2 for a description of PCI sparse and dense address spaces.

Each HPC decodes the CSR command although only one HPC executes it. After executing the CSR read or write command, the HPC returns a CSR status packet to the TIOP over the Up Hose. Data is included in the Up Hose packet if the command was a CSR read.

The DWLPA can buffer four CSR transactions while the DWPLB can buffer six CSR transactions. The buffering reduces the I/O port wait time between the end of one transaction on the PCI bus and the start of the next transaction on the PCI bus.

#### **1.5.4** Interrupt Transactions

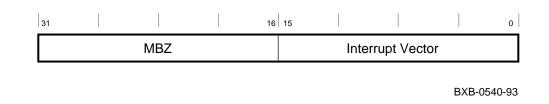

Interrupts are handled by all three of the physical PCI buses. Each HPC accepts 16 PCI device interrupt inputs from the bus it interfaces to. Each HPC has 17 programmable interrupt vector registers. Sixteen of the registers hold hardware device interrupt vectors, and one register holds an error interrupt vector.

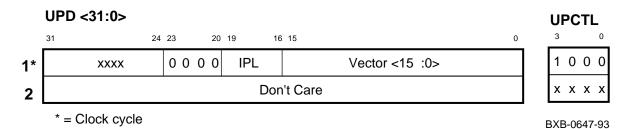

The interrupts are latched and prioritized in the HPC. The HPC generates an INTR/IDENT by accessing the CSR that contains the selected interrupt's vector and merging it with a programmable device IPL. The INTR/IDENT is then sent to the I/O port over the Up Hose.

All PCI device interrupts are issued as INTR/IDENTs at the same interrupt priority level. No prioritization is provided between interrupts generated on different PCI buses. Normal Up Hose arbitration is used to select the order in which HPCs issue INTR/IDENTS to the Up Hose. All HPCs monitor the outstanding INTR/IDENTs and inhibit issuing INTR/IDENTs at the outstanding IPLs until an interrupt status packet for that IPL is returned on the Down Hose.

# Chapter 2

# Addressing

## 2.1 TLSB System Addressing

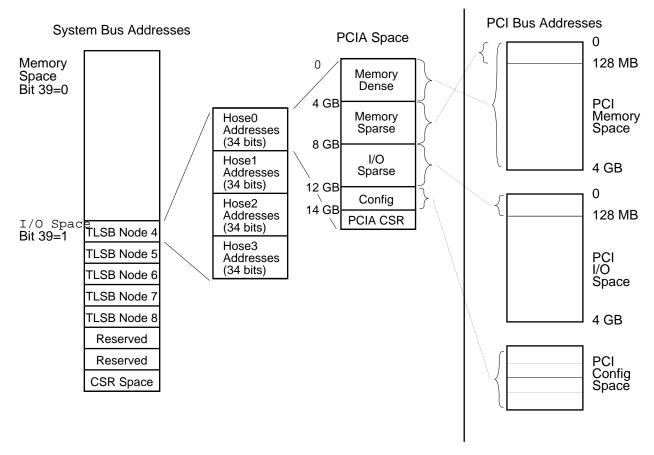

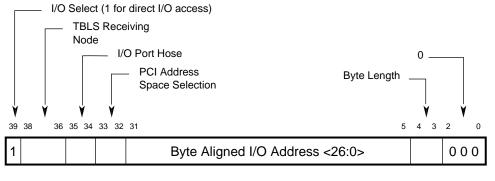

The AlphaServer 8200/8400 system bus (TLSB) supports up to 1 terabyte (40 bits) of physical address space. All system memory resides on the TLSB in the lower 512 gigabytes. The system provides direct I/O space access through the upper 512 gigabytes. Up to three KFTHA I/O modules are supported, although TLSB systems can be configured with as many as five KFTHAs. I/O space is divided among the five TLSB nodes that can contain I/O port modules. Within each node I/O space, the address space is divided among the four I/O port hoses. The various address spaces created by this scheme are known as window spaces. Table 2-1 gives the map of TLSB address space. Table 2-2 shows how each node I/O address space is assigned to four hoses. The System Bus Address portion of Figure 2-1 shows the window space.

Table 2-1TLSB Address Map

| TLSB ADDR<39:0>             | Description                      |

|-----------------------------|----------------------------------|

| 00 0000 0000 - 7F FFFF FFFF | TLSB memory space                |

| 80 0000 0000 - 8F FFFF FFFF | I/O space for node 4             |

| 90 0000 0000 - 9F FFFF FFFF | I/O space for node 5             |

| A0 0000 0000 - AF FFFF FFFF | I/O space for node 6             |

| B0 0000 0000 - BF FFFF FFFF | I/O space for node 7             |

| C0 0000 0000 - CF FFFF FFFF | I/O space for node 8             |

| D0 0000 0000 - DF FFFF FFFF | Reserved                         |

| E0 0000 0000 - EF FFFF FFFF | Reserved                         |

| F0 0000 0000 - FF FFFF FFFF | TLSB CSR space/CPU private space |

#### Table 2-2 I/O Node Space Assignment

| Address Range               | Assignment           |

|-----------------------------|----------------------|

| x0 0000 0000 - x3 FFFF FFFF | I/O space for hose 0 |

| x4 0000 0000 - x7 FFFF FFFF | I/O space for hose 1 |

| x8 0000 0000 - xB FFFF FFFF | I/O space for hose 2 |

| xC 0000 0000 - xF FFFF FFFF | I/O space for hose 3 |

## 2.2 System Bus to PCI Addressing

A PCIA consumes 16 Gbytes (34 bits) of system I/O address space, which it uses to provide four mappings of a single 4-Gbyte PCI address space. Multiple mappings are required because the PCI uses multiple transaction types and sizes which cannot be directly expressed by an Alpha CPU. The cycle types and transaction sizes are encoded in the I/O space addresses generated by the CPU.

Although the PCIA supports three electrically distinct PCI bus segments, it presents a single logical PCI address space. A device can be configured to a given PCI address, independent of which physical PCI bus it is connected to. This provides for a large number of PCI slots, without splitting the available system I/O address space into regions too small to provide useful mappings. Table 2-3 shows CPU to PCI address mapping for one PCIA. The remainder of the chapter provides the details of each mapping.

It is important to note that this section describes the view of a PCI address space *as seen from the CPU*. The view seen by a PCI device is different and is described in Section 2.4. Figure 2-1 shows the view of PCI addresses, as seen by the CPU.

The responsibility for mapping system (CPU) addresses to PCI addresses is shared by the PCIA and the I/O module. This chapter describes the system mapping on AlphaServer 8200/8400 systems. Refer to Chapter 5 and Appendix A for information on how system addresses are encoded in the hose protocol.

#### Figure 2-1 CPU View of PCI Addresses

BX0434-94

#### Table 2-3 CPU to PCI Address Mapping for a Single PCIA

| CPU Address Range                                                                             | PCI Address Range                  | PCI Address Space                         |  |  |

|-----------------------------------------------------------------------------------------------|------------------------------------|-------------------------------------------|--|--|

| x0 0000 0000 -                                                                                | 0000 0000 - FFFF FFFF              | PCI memory space - Dense mapping          |  |  |

| x0 FFFF FFFF                                                                                  |                                    |                                           |  |  |

| x1 0000 0000 -                                                                                | 0000 0000 - 00FF FFFF              | PCI memory space - Sparse mapping (fixed) |  |  |

| x1 1FFF FFFF                                                                                  |                                    |                                           |  |  |

| x1 2000 0000 -                                                                                | 0100 0000 - 07FF FFFF $^1$         | PCI memory space - Sparse mapping (vari-  |  |  |

| x1 FFFF FFFF                                                                                  |                                    | able)                                     |  |  |

| x2 0000 0000 -                                                                                | 0000 0000 - 00FF FFFF              | PCI I/O space - Sparse mapping (fixed)    |  |  |

| x2 1FFF FFFF                                                                                  |                                    |                                           |  |  |

| x2 2000 0000 -                                                                                | 0100 0000 - 07FF FFFF <sup>1</sup> | PCI I/O space - Sparse mapping (variable) |  |  |

| x2 FFFF FFFF                                                                                  | 2                                  |                                           |  |  |

| x3 0000 0000 -                                                                                | 0000 0000 - 0000 00FF $^2$         | PCI configuration space                   |  |  |

| x3 7FFF FFFF                                                                                  |                                    |                                           |  |  |

| x3 8000 0000 -                                                                                | N/A                                | PCIA CSRs and Map RAM                     |  |  |

| x3 FFFF FFFF                                                                                  |                                    |                                           |  |  |

| $^{1}$ Variable under the control of the HAE fields of the CTLx register. Shown for HAEs = 0. |                                    |                                           |  |  |

| <sup>2</sup> For each possible PCI device.                                                    |                                    |                                           |  |  |

| For each possible PCI dev                                                                     | vice.                              |                                           |  |  |

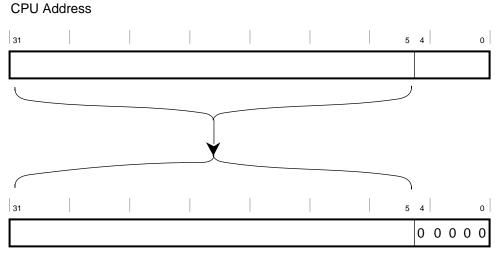

Figure 2-2 shows another view of the CPU to PCI mapping, indicating how the address bits are decoded. Note this is a "software" view of the decoding. It ignores some details of how the low-order address bits are actually passed from the CPU over the system bus to the I/O port.

#### Figure 2-2 CPU to PCI Address Mapping

BXB-0591-94

#### 2.2.1 PCI Memory Space

#### 2.2.1.1 Dense Mapping

Accesses to the first 4 Gbytes of the PCIA address space are mapped oneto-one to the combined PCI memory space. Software can reference only aligned, longword, and quadword PCI data through the dense mapping, since there is no way to encode byte, word, or tribyte references.

On AlphaServer 8200 and 8400 systems, the KFTIA/KFTHA transfers 32byte blocks of data to the PCIA. The blocks result from merging of CSR writes in the CPU's write buffers (32-byte blocks). Each block of write data is accompanied by a mask that indicates which longwords in the block contain valid data.

The PCIA transfers a block by generating a burst on the PCI, referencing each longword within the block and transferring data for the longwords indicated by the mask (enables asserted). Unmasked longwords are written in a cycle with all PCI byte enables deasserted. The following software restriction is therefore forced: software must not reference a PCI memory location through dense space unless all locations of the 32-byte block containing the data exist and can be accessed without side effects.

For CPU reads directed to the PCI, the PCIA generates a burst on the PCI for a 32-byte block. Again, this forces the restriction that all locations of the 32-byte block containing the data exist and are readable without side effects. Although a 32-byte block is read and returned over the system bus, the CPU determines how much data is used. For AlphaServer 8200/8400, the read-merge buffer limits the maximum usable data to two quadwords.

For all dense space transfers, PCI addresses are generated as shown in Figure 2-3.

#### Figure 2-3 Dense Space Address Mapping

PCI Address

BXB-0545-93

#### 2.2.1.2 Sparse Mapping

Accesses to the second 4 Gbytes of the PCIA address space are mapped to the PCI using a sparse addressing scheme. The PCI bus is a longword wide, with four byte enables. Therefore, access to arbitrary groups of bytes within a longword is allowed. The Alpha architecture only provides instructions to access aligned longwords and quadwords. Sparse mapping allows byte, word, tribyte, longword, and quadword accesses to be performed on the PCI, by encoding the size and position of an access in the low-order bits of the CPU address. The PCIA supports the encoding shown in Table 2-4, which is sufficient to produce all the PCI references.

| CPU      | CPU    | Transfer | PCIA  |                         |

|----------|--------|----------|-------|-------------------------|

| A<6:5>   | A<4:3> | Size     | <1:0> | PCI Byte Enables (C/BE) |

| 00       | 00     | Byte     | 00    | 1110 (0 = enabled)      |

| 01       | 00     |          | 00    | 1101                    |

| 10       | 00     |          | 00    | 1011                    |

| 11       | 00     |          | 00    | 0111                    |

| 00       | 01     | Word     | 00    | 1100                    |

| 01       | 01     |          | 00    | 1001                    |

| 10       | 01     |          | 00    | 0011                    |

| 11       | 01     |          | 00    | 0111 <sup>1</sup>       |

| 00       | 10     | Tribyte  | 00    | 1000                    |

| 01       | 10     | Ū        | 00    | 0001                    |

| 10       | 10     |          | 00    | 0011 1                  |

| 11       | 10     |          | 00    | 0111 1                  |

| 00       | 11     | Longword | 00    | 0000                    |

| 01       | 11     | 0        | 00    | 0001 1                  |

| 10       | 11     |          | 00    | 0011 1                  |

| $11^{2}$ | 11     | Quadword | 00    | 0000 (1st cycle)        |

|          |        | v        |       | 0000 (2nd cycle)        |

### Table 2-4 Sparse Access Encoding - PCI Memory Space

<sup>2</sup> For quadwords, CPU A<7> must be zero.

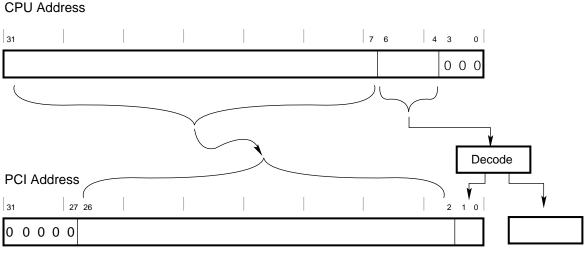

Since five address bits are used by access encoding, a 4-Gbyte range of PCIA address space maps only 128 Mbytes of PCI memory space. The lower 512 Mbytes of CPU sparse address space maps directly to the lower 16 Mbytes of PCI memory space using the translation shown in Figure 2-4.

#### Figure 2-4 Sparse Space Address Mapping (Lower 16 Mbytes)

PCI Byte Enables

BXB-0546-93

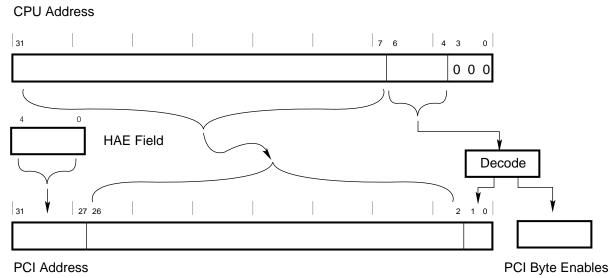

For the upper 3.5 Gbytes of PCIA space (CPU A<31:29> non-zero), the translation is modified by supplying an additional five high-order PCI address bits obtained from the Memory Hardware Address Extension (MHAE) field in the PCIx Control Register (CTLx). This maps an additional 112 Mbytes of PCI address space, with addresses constructed as shown in Figure 2-5.

#### Figure 2-5 Sparse Space Address Mapping (Upper 112 Mbytes)

BXB-0547-93

To perform a byte, word, or tribyte access to PCI memory space, software must issue an LDL or STL instruction to an address created as described above. The longword quantity is transferred from/to the PCI data lines,

without any byte shifting. Software is responsible for positioning the data in the correct byte lanes, corresponding to the byte enables shown in Table 2-4. For quadword transfers, software must issue an LDQ or STQ instruction. The low longword of the quadword will be written to the specified PCI address, and the high longword will be written to the next longword address.

Note that for PCI memory space, the PCI specification requires that PCI A<1:0> encode the address burst order. The PCIA always forces these bits to zero (linear incrementing burst addresses).

#### 2.2.2 PCI I/O Space

Accesses to the third 4 Gbytes of the PCIA address space are sparsely mapped to the PCI I/O space. The mapping is identical to that used for sparse memory space, except for PCI A<1:0>. Table 2-5 shows the mapping for PCI I/O space.

#### Table 2-5 Sparse Access Encoding - PCI I/O Space

| CPU                                                                                                                                                                                                        | CPU    | Transfer | PCIA            |                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------|-----------------|-------------------------------|

| A<6:5>                                                                                                                                                                                                     | A<4:3> | Size     | <1:0>           | PCI Byte Enables (C/BE)       |

| 00                                                                                                                                                                                                         | 00     | Byte     | 00              | 1110 (0 = enabled)            |

| 01                                                                                                                                                                                                         | 00     |          | 01              | 1101                          |

| 10                                                                                                                                                                                                         | 00     |          | 10              | 1011                          |

| 11                                                                                                                                                                                                         | 00     |          | 11              | 0111                          |

| 00                                                                                                                                                                                                         | 01     | Word     | 00              | 1100                          |

| 01                                                                                                                                                                                                         | 01     |          | 01              | 1001                          |

| 10                                                                                                                                                                                                         | 01     |          | 10              | 0011                          |

| 11                                                                                                                                                                                                         | 01     |          | 01 <sup>1</sup> | 0111 <sup>1</sup>             |

| 00                                                                                                                                                                                                         | 10     | Tribyte  | 00              | 1000                          |

| 01                                                                                                                                                                                                         | 10     | -        | 01              | 0001                          |

| 10                                                                                                                                                                                                         | 10     |          | $10^{1}$        | 0011 1                        |

| 11                                                                                                                                                                                                         | 10     |          | 11 <sup>1</sup> | <b>0111</b> <sup>1</sup>      |

| 00                                                                                                                                                                                                         | 11     | Longword | 00              | 0000                          |

| 01                                                                                                                                                                                                         | 11     | 0        | 01 <sup>1</sup> | 0001 1                        |

| 10                                                                                                                                                                                                         | 11     |          | 10 <sup>1</sup> | 0011 1                        |

| 11                                                                                                                                                                                                         | 11     | Quadword | 00              | 0000 (1st cycle PCI A<2> = 0) |

| $0000 \ (2nd \ cycle \ PCI \ A < 2 > = 1)$ <sup>1</sup> Software should consider these combinations of CPU<6:3> as undefined. They are not re-<br>quired to produce the same results on all Alpha systems. |        |          |                 |                               |

For the upper 3.5 Gbytes of PCIA I/O space (CPU A<31:29> non-zero), the I/O Hardware Address Extension (IHAE) field of the PCIx Control Register (CTLx) supplies the upper five bits of the PCI address. All other aspects of sparse I/O space are identical to those of sparse memory space.

#### 2.2.3 PCI Configuration Space

The next 2-Gbyte region of PCIA address space provides access to PCI configuration space. The same sparse mapping used for I/O and memory space is used here, with the following exceptions:

- PCI ADDR<1:0> control the type of configuration cycle being performed. These bits are supplied by bits in the CTLx CSRs.

- PCI ADDR<31:26> are always zero.

Each PCI device has a 256-byte region for its configuration registers. For a PCI device on one of the PCIA's bus segments (that is, not on a bridged bus), the configuration registers are referenced with a Type 0 configuration cycle (PCI ADDR<1:0> = 0), using addresses constructed as shown in Figure 2-6.

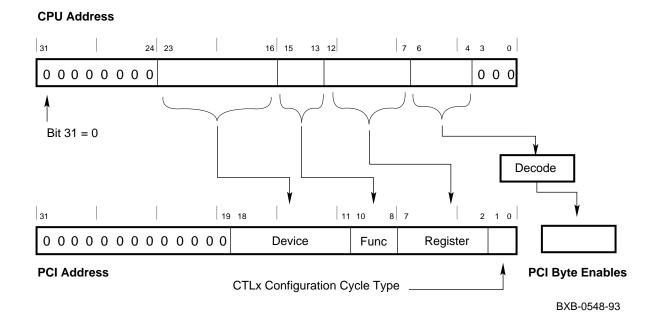

#### Figure 2-6 PCI Configuration Space Addressing - Type 0 Addresses

| CPU Address | PCI Address |                                                                                                   |

|-------------|-------------|---------------------------------------------------------------------------------------------------|

| Bits        | Bits        | Definition                                                                                        |

|             | <31:19>     | Always zero                                                                                       |

| <23:16>     | <18:11>     | PCI device select. Each PCI address line <16:11> is physically tied to one PCI device IDSEL line. |

|             |             | PCI<18:17> identify the HPC.                                                                      |

|             |             | 00 - HPC 0                                                                                        |

|             |             | 01 - HPC 1                                                                                        |

|             |             | 10 - HPC 2                                                                                        |

|             |             | 11 - HPC 3                                                                                        |

|             |             | PCI<16:11> identify the IDSEL line.                                                               |

| <15:13>     | <10:8>      | Device function number                                                                            |

| <12:7>      | <7:2>       | Configuration register                                                                            |

| <6:3>       |             | Sparse space encoding of byte enables                                                             |

| <2:0>       |             | Must be zero.                                                                                     |

|             | <1:0>       | Configuration cycle type from CTLx register; zero for                                             |

|             |             | Type 0 cycles.                                                                                    |

#### Table 2-6 PCI Configuration Space - Type 0 Address Fields

PCI device is selected by PCI Address <18:11>. The resulting memory map is shown in Table 2-7. Each HPC can address up to five PCI devices. This capability is used to access the PCI devices located on the standard I/O module, and when the HPC is used in other products.

No slots of PCI bus 0 can contain PCI modules, if the standard I/O module is installed, because these slots share PCI bus signals with PCI devices on the standard I/O module. Those physical backplane positions can still be used for EISA modules, except for the second slot, which holds the standard I/O connector module.

Type 0 configuration cycles are sent only on the physical PCI bus segment containing the selected device.

| CPU ADDR<31:0>        | Destination Addressed |                               |

|-----------------------|-----------------------|-------------------------------|

|                       | Without Standard I/O  | With Standard I/O             |

| 0000 0000 - 0000 FFFF | Not used              | Not used                      |

| 0001 0000 - 0001 FFFF | Not used              | Standard I/O Ethernet port    |

| 0002 0000 - 0003 FFFF | Not used              | Not used                      |

| 0004 0000 - 0007 FFFF | PCI Bus 0 Slot 0      | Standard I/O EISA bridge chip |

| 0008 0000 - 000F FFFF | PCI Bus 0 Slot 1      | Not used                      |

| 0010 0000 - 001F FFFF | PCI Bus 0 Slot 2      | Not used                      |

| 0020 0000 - 003F FFFF | PCI Bus 0 Slot 3      | Not used                      |

| 0040 0000 - 0040 FFFF | Not used              | Not used                      |

| 0041 0000 - 0041 FFFF | Not used              | Not used                      |

| 0042 0000 - 0043 FFFF | Not used              | Not used                      |

| 0044 0000 - 0047 FFFF | PCI Bus 1 Slot 0      | PCI Bus 1 Slot 0              |

| 0048 0000 - 004F FFFF | PCI Bus 1 Slot 1      | PCI Bus 1 Slot 1              |

| 0050 0000 - 005F FFFF | PCI Bus 1 Slot 2      | PCI Bus 1 Slot 2              |

| 0060 0000 - 007F FFFF | PCI Bus 1 Slot 3      | PCI Bus 1 Slot 3              |

| 0080 0000 - 0080 FFFF | Not used              | Not used                      |

| 0081 0000 - 0081 FFFF | Not used              | Not used                      |

| 0082 0000 - 0083 FFFF | Not used              | Not used                      |

| 0084 0000 - 0087 FFFF | PCI Bus 2 Slot 0      | PCI Bus 2 Slot 0              |

| 0088 0000 - 008F FFFF | PCI Bus 2 Slot 1      | PCI Bus 2 Slot 1              |

| 0090 0000 - 009F FFFF | PCI Bus 2 Slot 2      | PCI Bus 2 Slot 2              |

| 00A0 0000 - 00BF FFFF | PCI Bus 2 Slot 3      | PCI Bus 2 Slot 3              |

| 00C1 0000 - 00FF FFFF | Not used              | Not used                      |

| 0100 0000 - 07FF FFFF | Above 4 sub-regions   | Above 4 sub-regions           |

|                       | Wrapped 7 more times  | Wrapped 7 more times          |

### Table 2-7 Type 0 Configuration Space Address Map

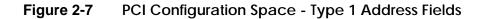

Type 1 configuration cycles (PCI ADDR<1:0>=1) are used to access configuration registers on PCIs bridged from the PCIA. Type 1 accesses are not decoded by the PCIA and are sent to all three PCI buses. Addresses for type 1 cycles are translated as shown in Figure 2-7.

#### Table 2-8 PCI Configuration Space Addressing - Type 1 Address Bits

| CPU Address Bits | PCI Address Bits | Definition                                        |

|------------------|------------------|---------------------------------------------------|

|                  | <31:24>          | Always zero                                       |

| <28:21>          | <23:16>          | PCI bus number                                    |

| <20:16>          | <15:11>          | PCI device select                                 |

| <15:13>          | <10:8>           | PCI device function number                        |

| <12:7>           | <7:2>            | Configuration register                            |

| <6:3>            |                  | Sparse space encoding of byte enables             |

| <2:0>            |                  | Must be zero.                                     |

|                  | <1:0>            | Configuration cycle type from CTLx register - one |

|                  |                  | for Type 1 cycles.                                |

#### 2.2.3.1 PCIA CSR and Map RAM Space

The final 2-Gbyte region of PCIA address space contains the control and status registers for the PCIA and the map RAM used for address translation. References to this region do not result in transactions on the PCI. The PCIA registers reside in each of the HPCs and on the PCIA module. There is one bank of registers for each HPC as shown in Table 2-9. The module registers are addressed through HPC0.

The address translation map RAM consists of 32K longword entries for the DWLPA and 128K longword entries for the DWLPB. These entries are used to perform scatter/gather mapping and to translate 32-bit PCI DMA addresses into 40-bit TLSB system addresses. The CSR and map RAM regions can be read and written using either longword- or quadword-width accesses. Quadword accesses must be aligned on quadword boundaries.

#### Table 2-9 PCIA CSR and Map RAM Address Space

| CPU Address<31:0>     | Destination Addressed                                                                    |

|-----------------------|------------------------------------------------------------------------------------------|

| 8000 0000 - 801F FFFF | HPC 0 CSRs                                                                               |

| 8020 0000 - 803F FFFF | HPC 1 CSRs                                                                               |

| 8040 0000 - 805F FFFF | HPC 2 CSRs                                                                               |

| 8060 0000 - 807F FFFF | Reserved.                                                                                |

|                       | Access causes PCIA Illegal CSR Error                                                     |

| 8080 0000 - 80FF FFFF | Module CSRs. Writes to unused addresses ig-<br>nored, reads return the PRESENT register. |

| 8100 0000 - 81FF FFFF | Map RAM                                                                                  |

| 8200 0000 - 83FF FFFF | Reserved                                                                                 |

| 8400 0000 - FFFF FFFF | Aliased copies of 8000 0000 - 83FF FFFF                                                  |

#### 2.2.3.2 EISA Subtractive Decode Window

The PCI-EISA bridge uses a technique called subtractive decode to determine which PCI addresses to forward to the EISA bus. The PCIA only supports subtractive decode in the first 8 Mbytes of PCI memory. Therefore, all EISA memory space devices must be configured in the first 8 Mbytes of EISA (and therefore PCI) memory space. When the standard I/O module (KFE70) is installed, no PCI devices may be configured in the first 8-Mbyte segment of PCI memory.

### 2.2.3.3 PCIA Reserved Addresses

The preceding sections describe various address ranges as Reserved. Also reserved are addresses in PCI memory, I/O, or configuration space that are not occupied by any device on the PCI bus. If these addresses are accessed by a CPU, an error is reported.

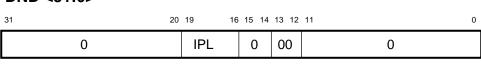

On a read to a nonexistent address, the PCIA will return a hose packet with the error bit set. The result of this is system dependent. On AlphaServer systems, the I/O port responds by writing to the CSR Read Return Error Register in TLSB CSR Broadcast space. This results in a machine check interrupt being delivered to the CPU through vector 0x660. On a write to a nonexistent address, the PCIA reports an interrupt through the PCIA Error Interrupt Vector. Refer to Chapter 5 for details on which HPC determines that an error occurred and what data is captured in the error CSRs.

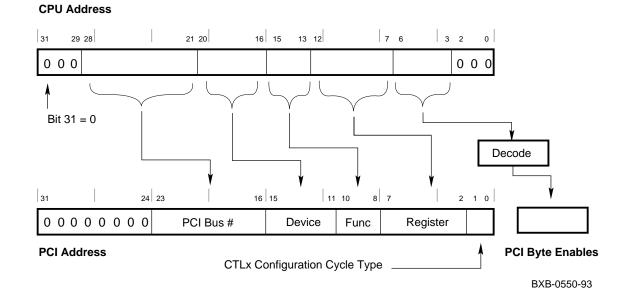

### 2.3 PCI to System Bus Addressing

The PCIA serves as a bridge to allow PCI devices to perform direct memory access (DMA) to system memory. A given PCI device sees a single memory address space, which must contain both system memory and the memory space registers of other PCI devices. The PCIA provides three programmable address windows to make system memory addresses visible from the PCI. Memory space references generated by a PCI bus master that fall within these windows are translated and forwarded up the hose to the system memory bus. Memory references that do not hit in the windows are not forwarded, and may be decoded by another PCI target device on the same physical PCI bus segment. The PCIA does not forward memory references from one PCI bus segment to the other two.

Figure 2-8 shows a possible view of the system address space, as seen by a PCI device. The shaded regions are only accessible by devices on the same PCI physical segment. The unshaded regions indicate where PCI memory space accesses are forwarded to system memory space, either directly or through the scatter/gather address map. The exact mapping of PCI to system memory regions is dependent on the programming of the address window registers. The registers should be programmed identically in each HPC, producing the same mapping from each PCI physical segment.

#### Figure 2-8 PCI Device View of System Address Space

BX-0436-95

#### 2.3.1 PC Compatibility Holes

Certain EISA devices respond to hardwired memory space addresses. PCI memory references to those addresses must not be forwarded to main memory. These nonforwarding regions are called "PC compatibility holes." There is typically one fixed hole covering the range 512 Kbytes to 1 Mbyte, and one variable hole in the range between 1 Mbyte and 16 Mbytes. Software defines the location of the holes by excluding the necessary regions from the DMA address windows. Address regions that do not hit in an address window are ignored by the PCIA and may be responded to by a PCI or EISA device.

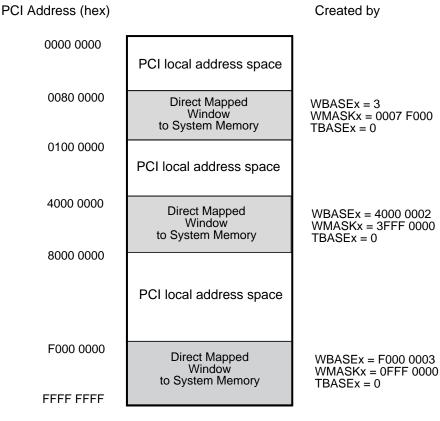

Figure 2-9 shows how the PCI memory space might be programmed. PC compatibility holes are created by placing PCI local address space over the appropriate region. DMA normally takes place through the third (mapped) window to allow all of system memory to be addressed.

#### Figure 2-9 PCI Memory Space, Including Compatibility Holes

BX-0435-94

#### 2.3.2 DMA Address Windows

Each address window is specified by three registers, a Window Base (WBASEx), Window Mask (WMASKx), and a Translated Base (TBASEx) register. Refer to Chapter 3 for the format of these registers. For normal operation, the corresponding registers in each HPC must be programmed identically. This causes system memory to appear at the same address range for every PCI device.

The Window Mask Registers provide a mask that selects the size of the windowed region. The size must be one of the values shown in Table 2-10.

Table 2-10

PCI Window Mask Values

| WMASK<31:0> | Size of Window |

|-------------|----------------|

| 0000 0000   | 64 kilobytes   |

| 0001 0000   | 128 kilobytes  |

| 0003 0000   | 256 kilobytes  |

| 0007 0000   | 512 kilobytes  |

| 000F 0000   | 1 megabyte     |

| 001F 0000   | 2 megabytes    |

| 003F 0000   | 4 megabytes    |

| 007F 0000   | 8 megabytes    |

| 00FF 0000   | 16 megabytes   |

| 01FF 0000   | 32 megabytes   |

| 03FF 0000   | 64 megabytes   |

| 07FF 0000   | 128 megabytes  |

| 0FFF 0000   | 256 megabytes  |

| 1FFF 0000   | 512 megabytes  |

| 3FFF 0000   | 1 gigabyte     |

| 7FFF 0000   | 2 gigabytes    |

| FFFF 0000   | 4 gigabytes    |

The Window Base Registers indicate the starting PCI address of the window. The address must be aligned on a natural boundary for the size of the window. For example, the base address for an 8-Mbyte window must specify an address that is an even multiple of 8 Mbytes. A Window Base Register contains an enable bit that enables translation and forwarding for the corresponding window. The Window Base Register also contains a Scatter/Gather enable bit that controls how the translation is done.

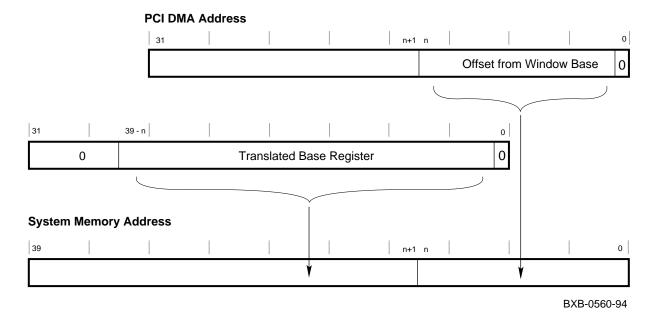

When a PCI address hits in the window, the PCIA generates a translated address using the Translated Base Register. If the Scatter/Gather enable bit is clear, a direct translation is performed using the mapping shown in Figure 2-10. The low-order bit of the Translated Base Register is ignored, and the remaining bits are concatenated with the offset within the window to form a 40-bit system bus address.

In Figure 2-10 the value of *n* is controlled by the Window Mask value. For example, to create a 1-Mbyte window starting at 0010 0000 and ending at 001F FFFF, the following values would be programmed into the registers named:

WMASK value:000F 0000 (n = 19) WBASE value: 0010 0000 TBASE value: 0000 0010

PCI DMA addresses in this range will be forwarded to main memory, translated to the CPU address range 00 0080 0000 to 00 008F FFFF.

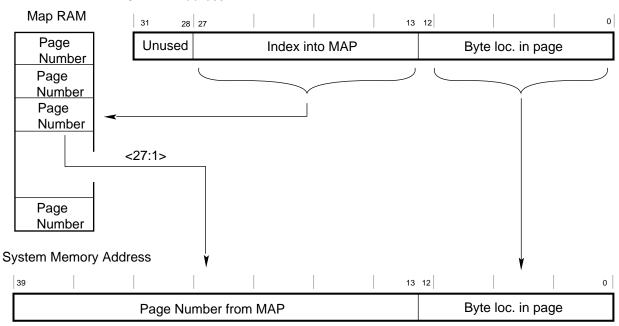

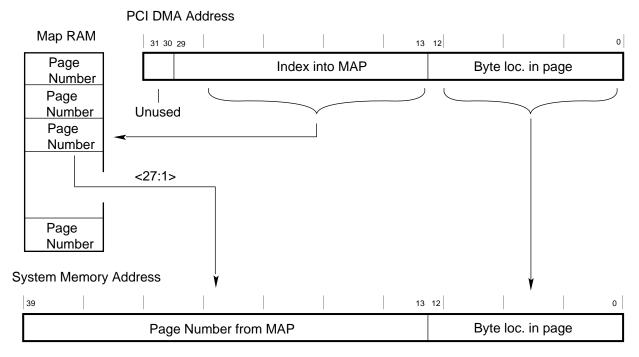

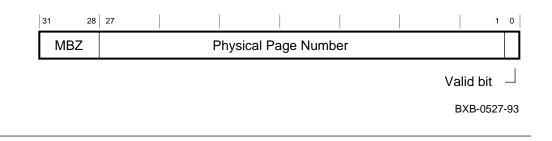

If the Scatter/Gather bit is set, the PCI address is interpreted as a page plus offset address, using an 8-Kbyte page size. The page portion of the address is used to index into the address translation map RAM, which provides a translated page number. The translation is shown in Figure 2-11. If the translation points to map a RAM entry that is marked as invalid, an error is reported.

#### Figure 2-10 Direct DMA Address Translation

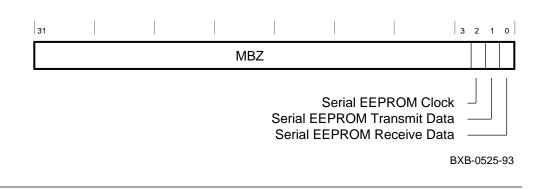

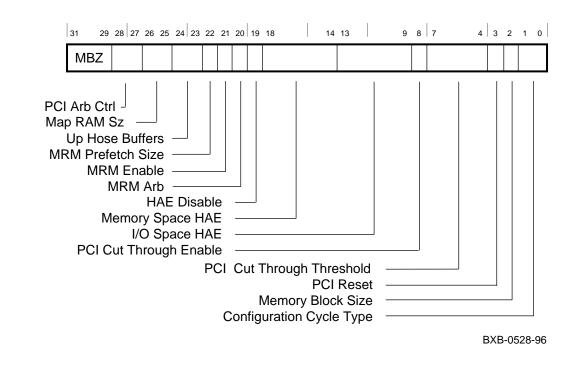

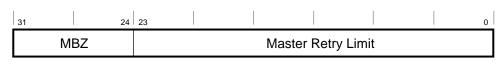

PCI DMA Address