# MS7AA Memory Technical Manual

Order Number EK-MS7AA-TM.001

The MS7AA memory module is designed for computer systems built around the LSB bus. The module can be configured in incremental storage capacities ranging from 64 Mbytes to 2 Gbytes.

digital equipment corporation maynard, massachusetts

#### **First Printing, November 1992**

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation.

Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software, if any, described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license. No responsibility is assumed for the use or reliability of software or equipment that is not supplied by Digital Equipment Corporation or its affiliated companies.

Copyright © 1992 by Digital Equipment Corporation.

All Rights Reserved. Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation:

| Alpha AXP         | DECUS   | VAXBI        |

|-------------------|---------|--------------|

| AXP               | DWMVA   | VAXELN       |

| DEC               | OpenVMS | VMScluster   |

| DECchip           | ULTRIX  | XMI          |

| DEC LANcontroller | UNIBUS  | The AXP logo |

| DECnet            | VAX     | digital      |

OSF/1 is a registered trademark of the Open Software Foundation, Inc.

**FCC NOTICE:** The equipment described in this manual generates, uses, and may emit radio frequency energy. The equipment has been type tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such radio frequency interference when operated in a commercial environment. Operation of this equipment in a residential area may cause interference, in which case the user at his own expense may be required to take measures to correct the interference.

| Preface | . vii |

|---------|-------|

|---------|-------|

# Chapter 1 Overview

| 1.1   | Major Sections              | 1-2 |

|-------|-----------------------------|-----|

| 1.1.1 | Memory Interface Controller | 1-2 |

| 1.1.2 | Memory Data Controller      |     |

| 1.1.3 | DRAM Arrays                 | 1-3 |

| 1.2   | Internal Buses              |     |

| 1.3   | Transactions                | 1-3 |

| 1.4   | Refresh                     | 1-3 |

# Chapter 2 Memory Interface Controller

| 2.1     | Components                      | 2-1 |

|---------|---------------------------------|-----|

| 2.2     | Logic Elements                  | 2-1 |

| 2.2.1   | Command Decode Logic            |     |

| 2.2.2   | Address Decode Logic            | 2-2 |

| 2.2.2.1 | Node Space CSR Transactions     | 2-2 |

| 2.2.2.2 | Memory Space Transactions       |     |

| 2.2.3   | DRAM Address Logic              | 2-3 |

| 2.2.4   | DRAM Control Logic              | 2-3 |

| 2.2.5   | MIC Data Path Logic             | 2-3 |

| 2.2.6   | Data Wrapping                   | 2-4 |

| 2.2.7   | Refresh Logic                   | 2-4 |

| 2.2.8   | Self-Test Logic                 | 2-5 |

| 2.2.9   | LSB State Machine Control Logic | 2-5 |

|         |                                 |     |

# Chapter 3 Memory Data Controller

| 3.1   | MDC Data Paths                       | 3-1 |

|-------|--------------------------------------|-----|

| 3.2   | MDC Transactions                     | 3-1 |

| 3.2.1 | Read and Wrapped Read Transactions   | 3-1 |

| 3.2.2 | Write and Wrapped Write Transactions | 3-2 |

# Chapter 4 Memory Organization

| 4.1 | Memory Capacity     | 4-1 |

|-----|---------------------|-----|

| 4.2 | Memory Banking      | 4-1 |

|     | Memory Interleaving |     |

# Chapter 5 LSB Memory Signals

# Chapter 6 Memory Transactions

| 6.1   | Memory Read Transactions          | 6-1 |

|-------|-----------------------------------|-----|

| 6.1.1 | LSB Stalled Read Transactions     |     |

| 6.1.2 | Module Stalled Read Transactions  | 6-1 |

| 6.2   | Memory Write Transactions         | 6-1 |

| 6.2.1 | LSB Stalled Write Transactions    | 6-2 |

| 6.2.2 | Module Stalled Write Transactions | 6-2 |

| 6.3   | Memory Transaction Ordering       | 6-2 |

| 6.4   | ECC Conversion                    |     |

# Chapter 7 Registers

| 7.1 | Node Space Base Addresses                    |  |

|-----|----------------------------------------------|--|

| 7.2 | Bit Access Type Acronyms                     |  |

| 7.3 | Register Descriptions                        |  |

|     | LDEV—Device Register                         |  |

|     | LBER—Bus Error Register                      |  |

|     | LCNR— Configuration Register                 |  |

|     | IBR—Information Base Repair Register         |  |

|     | LBESR0-3—Error Syndrome Registers            |  |

|     | LBECR0,1—Error Command Registers             |  |

|     | MCR—Memory Configuration Register            |  |

|     | AMR—Address Mapping Register                 |  |

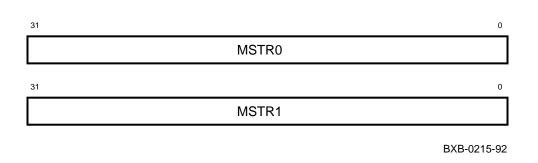

|     | MSTR0,1—Memory Self-Test Registers           |  |

|     | FADR—Failing Address Register                |  |

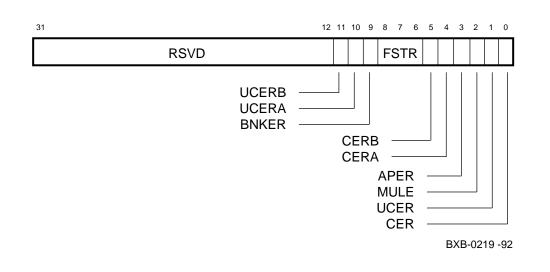

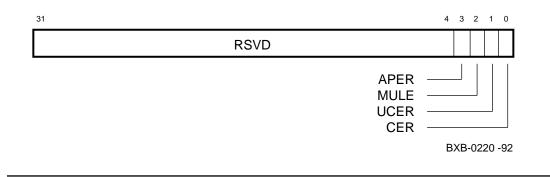

|     | MERA—Memory Error Register A                 |  |

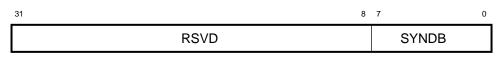

|     | MSYNDA—Memory Error Syndrome Register A      |  |

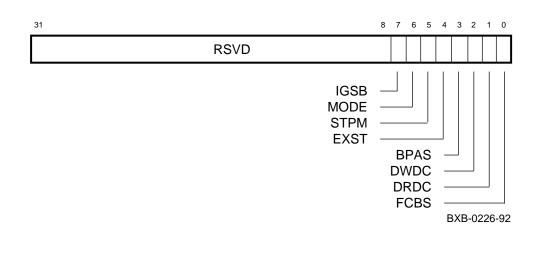

|     | MDRA—Memory Diagnostic Register A            |  |

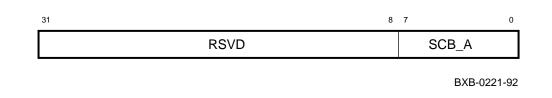

|     | MCBSA—Memory Check Bit Substitute Register A |  |

|     | MERB—Memory Error Register B                 |  |

|     | MSYNDB—Memory Error Syndrome Register B      |  |

|     | MDRB—Memory Diagnostic Register B            |  |

|     | MCBSB—Memory Check Bit Substitute Register B |  |

|     |                                              |  |

# Chapter 8 Error Conditions

| 8.1   | Memory-Related LSB Errors               | . 8-1 |

|-------|-----------------------------------------|-------|

| 8.2   | Memory-Specific Errors                  | . 8-1 |

| 8.3   | Error Syndrome Decoding                 |       |

| 8.3.1 | Quadword Memory Error Syndrome Decoding |       |

| 8.3.2 | Longword Memory Error Syndrome Decoding | . 8-4 |

# Chapter 9 Self-Test

| 9.1 | Self-Test Report      | 9-1 |

|-----|-----------------------|-----|

|     | Self-Test Modes       |     |

| 9.3 | Self-Test Performance | 9-2 |

# Figures

| 1-2 |

|-----|

| 4-2 |

| 4-3 |

| 4-4 |

| 5-1 |

| 5-2 |

|     |

# Tables

| 1    | Definitions of Terms Used in This Document      | ix   |

|------|-------------------------------------------------|------|

| 2    | DEC 7000/10000 and VAX 7000/10000 Documentation | x    |

| 3    | Related Documents                               | xii  |

| 2-1  | LSB Commands for Memory Operations              |      |

| 2-2  | LSB Data Wrapping                               | 2-4  |

| 2-3  | Refresh Rates at Various LSB Cycle Times        | 2-4  |

| 3-1  | MDC Wrap Ordering                               | 3-2  |

| 4-1  | Memory Array Capacity                           |      |

| 5-1  | LSB Memory Signals                              | 5-2  |

| 7-1  | LSB Node Space Base Addresses                   | 7-1  |

| 7-2  | Access Types of Register Bits                   | 7-2  |

| 7-3  | Memory Module Registers                         |      |

| 7-4  | LDEV Register Bit Definitions                   | 7-4  |

| 7-5  | LBER Register Bit Definitions                   | 7-6  |

| 7-6  | LCNR Register Bit Definitions                   |      |

| 7-7  | IBR Register Bit Definitions                    |      |

| 7-8  | LBESR Register Bit Definitions                  |      |

| 7-9  | LBECR Register Bit Definitions                  |      |

| 7-10 | MCR Register Bit Definitions                    |      |

| 7-11 | AMR Register Bit Definitions                    |      |

| 7-12 | MSTR Register Bit Definitions                   |      |

| 7-13 | Memory Error Address Segments                   |      |

| 7-14 | FADR Register Bit Definitions                   |      |

| 7-15 | MERA Register Bit Definitions                   | 7-21 |

| 7-16 | MSYNDA Register Bit Definitions                 |      |

| 7-17 | MDRA Register Bit Definitions                   |      |

| 7-18 | MCBSA Register Bit Definitions                  |      |

| 7-19 | MERB Register Bit Definitions                   |      |

| 7-20 | MSYNDB Register Bit Definitions                 |      |

| 7-21 | MDRB Register Bit Definitions                   |      |

| 7-22 | MCBSB Register Bit Definitions                  |      |

| 8-1  | Quadword Error Syndrome Table                   |      |

| 8-2  | Longword LSB Error Syndrome Table               |      |

| 9-1  | Memory Self-Test Times                          | 9-2  |

|      |                                                 |      |

## Intended Audience

This manual describes the bit-level hardware functions of the MS7AA memory module used in computer systems designed around the LSB bus. It is written for developers of system and application software. It assumes machine level programming knowledge and familiarity with the operating system.

## **Document Structure**

The material is presented in nine chapters.

- Chapter 1, **Overview**, presents an overall introduction to the MS7AA memory module.

- Chapter 2, **Memory Interface Controller**, describes the hardware interface to the LSB bus and discusses the functions of the logic elements implemented on the MIC chips.

- Chapter 3, **Memory Data Controller**, describes the interface between the MIC chips and the dynamic random access memory array of the memory module.

- Chapter 4, **Memory Organization**, describes how memory is organized on a single module or multiple modules and explains how memory performance is enhanced by dividing the DRAMs into two banks and using interleaving techniques.

- Chapter 5, **LSB Memory Signals**, describes the signals used by the memory module to communicate with the LSB bus.

- Chapter 6, **Memory Transactions**, describes how read and write operations are executed on the memory modules.

- Chapter 7, **Registers**, lists the LSB-required and memory-specific registers and provides bit-level functional descriptions of each register.

- Chapter 8, **Error Conditions**, describes the two categories of errors detected by the memory module and explains how errors are reported in associated error syndrome registers.

- Chapter 9, **Self-Test**, tells when a memory module performs a self-test and gives a brief overview of functions that the memory self-test provides.

# **Conventions Used in This Document**

#### **Results and Operations**

Results of operations termed UNPREDICTABLE must not be used by software.

Operations termed UNDEFINED do not cause the processor to hang, that is, reach a state from which there is no transition to a normal state of instruction execution. Nonprivileged software cannot invoke UNDEFINED operations.

#### **Register and Bit Designations**

Certain conventions are followed in register descriptions and in references to bits and bit fields:

- Registers are referred to by their mnemonics, such as **MCR register**. The full name of a register (for example, **Memory Configuration Register**) is spelled out only at the top of the register description page, or when the register is first introduced.

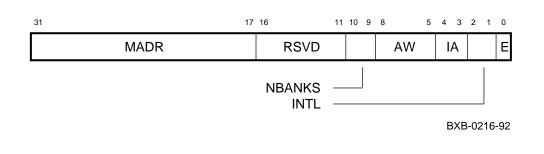

- Bits and fields are enclosed in angle brackets. For example, **bit** <**31**> and **bits** <**31:16**>. For clarity of reference, bits are usually specified by their numbers or names enclosed in angle brackets adjacent to the register mnemonic, such as **AMR**<**31:17**> or **AMR**<**MADR**>, which are equivalent designations.

- When the value of a bit position is given explicitly in a register diagram, the information conveyed is as follows:

| Bit Value<br>Designation | Meaning                                                                                           |

|--------------------------|---------------------------------------------------------------------------------------------------|

| 0                        | Reads as zero; ignored on writes.                                                                 |

| 1                        | Reads as one; ignored on writes.                                                                  |

| X                        | Does not exist in hardware. The value of the bit is unpredictable on reads and ignored on writes. |

- Fields noted as must be zero (MBZ) must never be filled by software with a nonzero value.

- The entry in the **type** column of a register description table may include the initialization value of the bits. For example, entry "R/W, 0" indicates a read/write bit that is initialized to 0.

# Terminology

Table 1 gives the definition of terms and some mnemonics used in this document.

## Table 1 Definitions of Terms Used in This Document

| Term       | Definition                                                                                                                                                                                                                                            |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bank       | Smallest group of DRAMs that can be interleaved. A bank consists of one or more <i>strings</i> .                                                                                                                                                      |

| Block      | 64 bytes of data within naturally aligned boundaries.                                                                                                                                                                                                 |

| DDB        | DRAM data bus. The 576-bit bidirectional data bus that interfaces be-<br>tween the DRAM chips and the MDC gate arrays.                                                                                                                                |

| LSB        | The system bus.                                                                                                                                                                                                                                       |

| MDB        | Memory data bus. The 144-bit bidirectional data bus is the interface be-<br>tween the MIC gate arrays and the MDC gate arrays.                                                                                                                        |

| MDC        | Memory data controller. Chips that buffer data between the MIC and the DRAM arrays.                                                                                                                                                                   |

| MIC        | Memory interface controller. The interface of the memory subsystem to the LSB.                                                                                                                                                                        |

| String     | The smallest group of DRAMs (144 $1/4M \ge 4$ ) needed to store and retrieve 64 bytes of data per LSB transaction. In some array implementations, the number of banks and strings can be equal, while in others there may be more strings than banks. |

| 32-bit ECC | Synonymous with longword ECC.                                                                                                                                                                                                                         |

| 64-bit ECC | Synonymous with quadword ECC.                                                                                                                                                                                                                         |

# **Documentation Titles**

Table 2 lists the books in the DEC 7000/10000 and VAX 7000/10000 documentation sets. Table 3 lists other documents that you may find useful.

| Table 2 | DEC 7000/10000 and VAX 7000/10000 Documentation |  |

|---------|-------------------------------------------------|--|

|         |                                                 |  |

|                                  | 7000 Systems | 10000 Systems |

|----------------------------------|--------------|---------------|

| Title                            | Order Number | Order Number  |

| Installation Kit                 | EK-7000B-DK  | EK-1000B-DK   |

| Site Preparation Guide           | EK-7000B-SP  | EK-1000B-SP   |

| Installation Guide               | EK-700EB-IN  | EK-100EB-IN   |

| Hardware User Information Kit    | EK-7001B-DK  | EK-1001B-DK   |

| Operations Manual                | EK-7000B-OP  | EK-1000B-OP   |

| Basic Troubleshooting            | EK-7000B-TS  | EK-1000B-TS   |

| Service Information Kit—VAX 7000 | EK-7002A-DK  | EK-1002A-DK   |

| Platform Service Manual          | EK-7000A-SV  | EK-1000A-SV   |

| System Service Manual            | EK-7002A-SV  | EK-1002A-SV   |

| Pocket Service Guide             | EK-7000A-PG  | EK-1000A-PG   |

| Advanced Troubleshooting         | EK-7001A-TS  | EK-1001A-TS   |

| Service Information Kit—DEC 7000 | EK-7002B-DK  | EK-1002A-DK   |

| Platform Service Manual          | EK-7000A-SV  | EK-1000A-SV   |

| System Service Manual            | EK-7002B-SV  | EK-1002A-SV   |

| Pocket Service Guide             | EK-7700A-PG  | EK-1100A-PG   |

| Advanced Troubleshooting         | EK-7701A-TS  | EK-1101A-TS   |

| Reference Manuals                |              |               |

| Console Reference Manual         | EK-70C0B-TM  |               |

| KA7AA CPU Technical Manual       | EK-KA7AA-TM  |               |

| KN7AA CPU Technical Manual       | EK-KN7AA-TM  |               |

| MS7AA Memory Technical Manual    | EK-MS7AA-TM  |               |

| I/O System Technical Manual      | EK-70I0A-TM  |               |

| Platform Technical Manual        | EK-7000A-TM  |               |

| Title                                                | 7000 Systems<br>Order Number | 10000 Systems<br>Order Number |

|------------------------------------------------------|------------------------------|-------------------------------|

| Upgrade Manuals                                      |                              |                               |

| KA7AA CPU Installation Guide                         | EK-KA7AA-IN                  |                               |

| KN7AA CPU Installation Guide                         | EK-KN7AA-IN                  |                               |

| MS7AA Memory Installation Guide                      | EK-MS7AA-IN                  |                               |

| KZMSA Adapter Installation Guide                     | EK-KXMSX-IN                  |                               |

| DWLMA XMI PIU Installation Guide                     | EK-DWLMA-IN                  |                               |

| DWMBB VAXBI PIU Installation Guide                   | EK-DWMBB-IN                  |                               |

| H7237 Battery PIU Installation Guide                 | EK-H7237-IN                  |                               |

| H7263 Power Regulator Installation Guide             | EK-H7263-IN                  |                               |

| Futurebus+ PIU Installation Guide                    | EK-DWLAA-IN                  |                               |

| BA654 DSSI Disk PIU Installation Guide               | EK-BA654-IN                  |                               |

| BA655 SCSI Disk and Tape PIU Installa-<br>tion Guide | EK-BA655-IN                  |                               |

| Removable Media Installation Guide                   | EK-TFRRD-IN                  |                               |

Table 2 DEC 7000/10000 and VAX 7000/10000 Documentation (Continued)

# Table 3 Related Documents

| Title                                                                          | Order Number |

|--------------------------------------------------------------------------------|--------------|

| General Site Preparation                                                       |              |

| Site Environmental Preparation Guide                                           | EK-CSEPG-MA  |

| System I/O Options                                                             |              |

| BA350 DECstor/me Modular Storage Shelf<br>Subsystem Configuration Guide        | EK-BA350-CG  |

| BA350 DECstor/me Modular Storage Shelf<br>Subsystem User's Guide               | EK-BA350-UG  |

| BA350-LA DECstor/me Modular Storage Shelf<br>User's Guide                      | EK-350LA-UG  |

| CIXCD Interface User Guide                                                     | EK-CIXCD-UG  |

| DEC FDDIcontroller 400 Installation/Problem Solving                            | EK-DEMFA-IP  |

| DEC LANcontroller 400 Installation Guide                                       | EK-DEMNA-IN  |

| DEC LANcontroller 400 Technical Manual                                         | EK-DEMNA-TM  |

| DSSI VAXcluster Installation and Troubleshooting Manual                        | EK-410AA-MG  |

| InfoServer 150 Installation and Owner's Guide                                  | EK-INFSV-OM  |

| KDM70 Controller User Guide                                                    | EK-KDM70-UG  |

| KFMSA Module Installation and User Manual                                      | EK-KFMSA-IM  |

| KFMSA Module Service Guide                                                     | EK-KFMSA-SV  |

| RRD42 Disc Drive Owner's Manual                                                | EK-RRD42-OM  |

| RF Series Integrated Storage Element User Guide                                | EK-RF72D-UG  |

| TF85 Cartridge Tape Subsystem Owner's Manual                                   | EK-OTF85-OM  |

| TLZ06 Cassette Tape Drive Owner's Manual                                       | EK-TLZ06-OM  |

| Operating System Manuals                                                       |              |

| Alpha Architecture Reference Manual                                            | EY-L520E-DP  |

| DEC OSF/1 Guide to System Administration                                       | AA-PJU7A-TE  |

| DECnet for OpenVMS Network Management Utilities                                | AA-PQYAA-TK  |

| Guide to Installing DEC OSF/1                                                  | AA-PS2DA-TE  |

| OpenVMS Alpha Version 1.0 Upgrade and Installation Manual                      | AA-PQYSA-TE  |

| VMS Upgrade and Installation Supplement: VAX 7000–600 and VAX 10000–600 Series | AA-PRAHA-TE  |

| VMS Network Control Program Manual                                             | AA-LA50A-TE  |

# Table 3 Related Documents (Continued)

| Title                                              | Order Number |

|----------------------------------------------------|--------------|

| VMSclusters and Networking                         |              |

| HSC Installation Manual                            | EK-HSCMN-IN  |

| SC008 Star Coupler User's Guide                    | EK-SC008-UG  |

| VAX Volume Shadowing Manual                        | AA-PBTVA-TE  |

| Peripherals                                        |              |

| Installing and Using the VT420 Video Terminal      | EK-VT420-UG  |

| LA75 Companion Printer Installation and User Guide | EK-LA75X-UG  |

# Chapter 1

# **Overview**

The MS7AA memory module connects directly to the LSB bus and provides up to 2 Gbytes of dynamic random access memory (DRAM) to the CPU. The LSB memory subsystem features the following:

- 64-Mbyte to 2-Gbyte memory capacity per module

- Incremental configuration to a maximum of seven modules in a singleprocessor system

- 1-, 2-, 4-, and 8-way interleaving

- 64-byte block transfers, 16 bytes at a time, over the system bus

- Memory modules with DRAM arrays of 1M x 4 or 4M x 4 components

- Bit scattering to provide correction of data if a single DRAM fails

- Read and write data wrapping on 32-byte naturally aligned boundaries

- Quadword ECC protection that allows detection and correction of single-bit failures and detection of 2-bit failures

- Conversion logic that translates quadword ECC (DRAM ECC) to longword ECC (LSB ECC) during memory reads and longword ECC to quadword ECC during memory writes

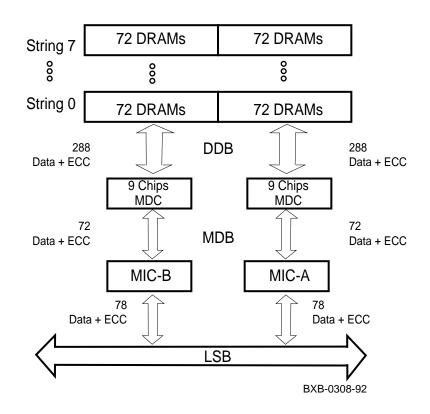

Figure 1-1 shows the architecture of a memory module.

### Figure 1-1 Memory Module Block Diagram

# 1.1 Major Sections

An MS7AA module consists of three major sections:

- Memory interface controller (MIC)

- Memory data controller (MDC)

- DRAM arrays

The major sections communicate with each other through internal buses.

#### 1.1.1 Memory Interface Controller

The memory interface controller (MIC) is comprised of two gate arrays, MIC-A and MIC-B. It provides the interface to the LSB, controls DRAM timing and refresh, runs memory self-test, and contains all LSB-required and memory-specific registers.

The MIC-A interfaces to LSB D<63:0> and the LSB control signals. It decodes the LSB command and determines if the memory module is selected for this transaction. The MIC-A provides the address and control signals for the two banks and contains most of the CSRs.

The MIC-B interfaces to LSB D<127:64>. It is strictly a data path, with some error checking logic and MIC-B-specific CSRs. The operation of the MIC-B is controlled by the MIC-A.

### 1.1.2 Memory Data Controller

The memory data controller (MDC) consists of DRAM buffers that reside between the MIC and the DRAM arrays. During a memory write, the MDC buffers accumulate the four LSB data cycles into a 64-byte packet that is written to the DRAMs in a single operation. During a memory read, the DRAM buffers store 64 bytes of data, then parcel it to the MIC, which in turn parcels it out to the LSB in four consecutive 16-byte cycles under the control of the MIC-A.

#### 1.1.3 DRAM Arrays

The DRAM arrays consist of DRAMs, control signal, and address buffer components. The MS7AA memory modules can use DRAM sizes of 1M x 4 bits or 4M x 4 bits. The DRAM arrays are organized into 1 to 8 strings. Each string requires 144 DRAMs (using DRAMs with quadword ECC), regardless of the DRAM type. A single string supports 64 Mbytes of memory when configured with 4-Mbit DRAMs, and 256 Mbytes of memory when configured with 16-Mbit DRAMs. The DRAM array on each memory module is configured with two independently accessible banks.

Interleaving of DRAM banks increases memory bandwith. Each memory module supports 2-way interleaving when configured with a minimum of two strings. Interleaving occurs between the two independently accessible banks within a module. A memory configuration on the LSB consisting of four memory modules, with at least two strings each, supports a maximum of 8-way interleaving.

# 1.2 Internal Buses

Data within the memory modules is transferred through two internal buses: the memory data bus (MDB) and the DRAM data bus (DDB). The MDB bus transfers data between the MIC chips and the MDC chips. The DDB bus transfers data between the MDC chips and the DRAM arrays.

## 1.3 Transactions

Memory responds to but cannot initiate LSB transactions. It responds to accesses to the memory space and to its own LSB node space. Memory does not respond to any transaction in LSB broadcast space.

Memory modules run synchronously with the LSB. Memory transfers consist of four contiguous, 16-byte data cycles, for a total of 64 bytes per transaction. Up to three pipelined transactions can be in progress on the LSB bus at a given time. Read and write data wrapping is supported on 32byte naturally aligned boundaries.

# 1.4 Refresh

Each memory module implements DRAM refresh. Module refresh is reset and restarted under two different conditions: power-up and system reset. All modules with the same DRAM refresh rate requirements refresh at the same time.

# **Memory Interface Controller**

The memory interface controller (MIC) controls data movement between the memory DRAM arrays and the LSB bus.

## 2.1 Components

The MIC consists of two 64-bit gate arrays, MIC-A and MIC-B.

The MIC-A interfaces to LSB D<63:0>, LSB control/status signals, and LSB ECC<13:0>. It controls the operation of the memory module as well as the operation of the MIC-B. The MIC-A generates the DRAM address and timing functions necessary for all DRAM operations. It also generates all signals used to control the memory data controller (MDC) chips.

The MIC-B interfaces to LSB D<127:64> and LSB ECC<27:14>. It functions strictly as a data path consisting of read and write data buffers, ECC logic, and CSRs.

The MIC-A implements most of the LSB-required and memory-specific registers. When a MIC-B control/status register is accessed by the CPU, data is transferred over an 8-bit bidirectional data path connecting the MIC-A and the MIC-B.

# 2.2 Logic Elements

The MIC implements the following logic elements:

- Command decode logic

- Address decode logic

- DRAM address logic

- DRAM control logic

- MIC data path logic

- Data wrapping

- Refresh logic

- Self-test logic

- LSB state machine control logic

The MIC also contains logic to support the memory data controller (MDC) interface.

### 2.2.1 Command Decode Logic

The LSB command decode logic receives and latches D<37:0> into its address latch during LSB command/address cycles. D<37:35> contain the LSB command field. Table 2-1 lists the LSB commands and the associated operations within the memory module.

#### Table 2-1LSB Commands for Memory Operations

| D<37:35> | Command      | Memory Operation                                      |

|----------|--------------|-------------------------------------------------------|

| 000      | Read         | Read memory at address specified on LSB D<34:0>.      |

| 001      | Write        | Write memory at address specified on LSB D<34:0>.     |

| 010      | Reserved     | Ignore command.                                       |

| 011      | Victim Write | Write memory at address specified on LSB D<34:0>.     |

| 100      | Read CSR     | Read memory CSR at address specified on LSB D<34:0>.  |

| 101      | Write CSR    | Write memory CSR at address specified on LSB D<34:0>. |

| 110      | Reserved     | Ignore command.                                       |

| 111      | Private      | Ignore command.                                       |

### 2.2.2 Address Decode Logic

Memory responds to two types of transactions:

- Node space CSR transactions

- Memory space transactions

Memory modules do not respond to transactions in LSB broadcast space.

#### 2.2.2.1 Node Space CSR Transactions

Node space contains LSB required registers and memory-specific registers accessed on aligned 64-byte boundaries. The MIC decodes the LSB node space address and processes the request to the specified register.

All registers are 32 bits wide. Since not all fields within registers contain a valit bit, CSR transactions involving bit fields with no associated valid bits return UNPREDICTABLE data on reads. Writes to nonexistent bits have no effect on module operations.

The MIC acknowledges memory node space requests whether the addressed CSR actually exists or not. Writes to nonexistent CSRs result in UNDEFINED operations. Reads to nonexistent CSRs return UNPRE-DICTABLE data.

### 2.2.2.2 Memory Space Transactions

The address decode logic compares the LSB address with bits from the Address Mapping Register (AMR) to determine if the memory module is selected for the current transaction. Various fields in the AMR register allow selection of memory space address decode parameters as described in the discussion of the AMR register in Chapter 7.

To support two banks per module, the address decode logic implements two independent address paths.

#### 2.2.3 DRAM Address Logic

The DRAM address logic generates row and column address bits for various memory configurations from the LSB address.

#### 2.2.4 DRAM Control Logic

The timing of DRAM components requires that control signals, along with the row and column addresses, conform to strict parameters. Each memory bank implements a DRAM timing generator to ensure that all DRAM control signals are properly sequenced during LSB memory access, module refresh, and module self-test.

In addition to DRAM control, the two timing generators pass control information between each other. Since there is one common data path between the MIC and the MDCs, communication between the two DRAM timing generators is needed to prevent data path conflicts.

#### 2.2.5 MIC Data Path Logic

The MIC data path can be broken down into two distinct blocks. The data path to/from the DRAMs and the data path to/from the CSRs.

The data path to/from memory consists of a write path and a read path. Within each path there are data buffers and ECC logic. The data path to/from the CSRs implements parity generation logic needed to generate LSB parity on returning CSR read data.

The MIC data path logic implements a  $4 \times 16$  byte write buffer and a  $4 \times 16$  byte read buffer that are used as temporary storage elements on the write data path and the read data path, respectively. Storage of LSB write data is necessary when the MDCs are busy with a previous write transaction. Storage of LSB read data is necessary when LSB STALL is asserted by a node other than the memory node supplying the requested read data. The buffers are designed to minimize delays on the data paths.

The LSB operates on a 32-bit ECC algorithm, while memory stores and retrieves data with a 64-bit ECC algorithm. The write data path logic checks, corrects, and then converts LSB longword (32-bit) ECC into quadword (64-bit) ECC that is stored in each memory module. Similarly, the read data path ECC logic checks, corrects, and then converts quadword (64-bit) ECC used by memory into longword (32-bit) ECC used by the LSB.

### 2.2.6 Data Wrapping

The data wrapping logic controls the alignment of data in the MDC chips. LSB supports read and write data wrapping on 32-byte boundaries. During an LSB command/address cycle, LSB D<0> is deasserted on all naturally aligned 64-byte block transactions. It is asserted when the commander node issues the second 32 bytes of data prior to the first 32 bytes on write transactions, and expects the second 32 bytes of data prior to the first 32 bytes on read transactions.

Table 2-2 defines the wrapping of read or write data depending upon the state of LSB D<0> latched during a command/address cycle.

#### Table 2-2 LSB Data Wrapping

| LSB D<0> | Data Cycle Ordering                            |

|----------|------------------------------------------------|

| 0        | Octaword-1, Octaword-2, Octaword-3, Octaword-4 |

| 1        | Octaword-3, Octaword-4, Octaword-1, Octaword-2 |

## 2.2.7 Refresh Logic

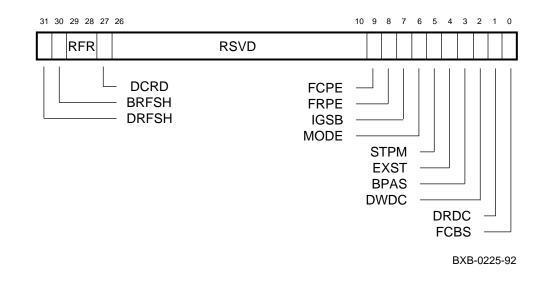

The refresh logic refreshes the memory module approximately every 15.6 microseconds regardless of DRAM type (4 Mbit, 16 Mbit). The refresh period is generated by a 10-bit divide-by counter from LSB clocks. The actual count value is 780 ticks. A given module can be refreshed at the nominal rate, 2 or 4 times the nominal rate as determined by bits in the Memory Diagnostic Register. Upon power-up or reset, the default refresh rate is the nominal value. Table 2-3 lists the refresh rate at various LSB cycle times.

#### Table 2-3 Refresh Rates at Various LSB Cycle Times

| LSB Cycle Time (ns) | Refresh Rate |  |

|---------------------|--------------|--|

| 16                  | 12.48        |  |

| 17                  | 13.26        |  |

| 18                  | 14.04        |  |

| 19                  | 14.82        |  |

| 20                  | 15.60        |  |

|                     |              |  |

Each memory module is refreshed independently of the other memory modules. Both banks of a memory array (all strings) are refreshed simultaneously with one exception: when an LSB read or write transaction is currently being serviced by one of the banks, refresh of the bank may be held off until the transaction has completed. Refresh is performed on the memory bank immediately following the completion of the transaction.

### 2.2.8 Self-Test Logic

Upon power-up, system reset, or when EXST\_A (bit <4> of the Memory Diagnostic Register A) is set by software, each module executes a self-test designed to test and initialize the DRAMs with good ECC. While self-test is executing, any reference to memory space is NO ACKed. CSR space can be accessed during self-test execution. However, writes to the Memory Diagnostic Register A (MDRA) and Memory Diagnostic Register B (MDRB) can result in UNPREDICTABLE behavior. See Chapter 9 for self-test times.

### 2.2.9 LSB State Machine Control Logic

The LSB state machine control logic controls the data path interface to/from the LSB and all CSR operations (read/write). This logic also starts the DRAM timing generators.

# Chapter 3

# **Memory Data Controller**

The memory data controller (MDC) is the data interface between the DRAMs and the memory interface controller (MIC). It connects the 576-bit DRAM data path to the 144-bit MIC data path. The MDC operates under the control of the MIC.

## 3.1 MDC Data Paths

The MDC provides separate read and write data paths to the DRAM array on one side and the MIC on the other.

Each MDC block is composed of eighteen MDC chips. Each MDC chip interfaces between a 32-bit bidirectional DDB (DRAM data bus) port and an 8-bit bidirectional MDB (MIC data bus) port. Both ports are controlled by the MIC-A.

## 3.2 MDC Transactions

MDC supports four types of transactions:

- Read

- Wrapped read

- Write

- Wrapped write

#### 3.2.1 Read and Wrapped Read Transactions

During a read transaction, the MDC chip receives DRAM read data on the DDB<31:0> port and loads it in its internal read data buffer. Once four bytes of data are assembled in the read data buffer, the MDC chip drives the content of the read data buffer onto the MDB<7:0> port in four separate clock cycles.

When data wrapping is selected, the order in which read data is transferred to the MIC is altered, as shown in Table 3-1.

### Table 3-1 MDC Wrap Ordering

| Cycle No. | Octaword No.<br>Wrap Disabled<br>(LSB D<0>=0) | Octaword No.<br>Wrap Enabled<br>(LSB D<0>=1) |

|-----------|-----------------------------------------------|----------------------------------------------|

| 1         | 1                                             | 3                                            |

| 2         | 2                                             | 4                                            |

| 3         | 3                                             | 1                                            |

| 4         | 4                                             | 2                                            |

## 3.2.2 Write and Wrapped Write Transactions

During a write transaction, the MDC chip receives DRAM write data on the MDB<7:0> port and loads it in its internal write data buffer in four consecutive cycles. Once the data is assembled in the write data buffer, the MDC drives the contents of the write data buffer onto the DDB<31:0> port.

When data wrapping is selected, the order in which write data is latched into the MDC is altered (see Table 3-1) so that data written to the DRAMs is not wrapped.

# **Memory Organization**

The system supports up to seven memory modules in single-processor configurations. The physical memory composed of a single or multiple memory modules can be organized in various ways to optimize memory access.

# 4.1 Memory Capacity

Memory can be configured with MS7AA modules of various capacities, from 64 Mbytes to 2 Gbytes. The DRAM arrays consist of DRAMs, control signals, and address buffer components. The memory modules can use DRAM sizes of 4 Mbits or 16 Mbits. The DRAM arrays are organized into 1 to 8 strings. Each string requires 144 DRAMs (using 1M x 4 or 4M x 4 DRAMs). A single string supports 64 Mbytes of memory when configured with 4-Mbit DRAMs, and 256 Mbytes of memory when configured with 16-Mbit DRAMs. Table 1-1 lists array capacities that can be configured based upon the number of strings on a module and the DRAM type.

| DRAM Type<br>(Mbits) | Number of<br>Strings | Memory Capacity<br>(Mbytes) |

|----------------------|----------------------|-----------------------------|

| 4                    | 1                    | 64                          |

| 4                    | 2                    | 128                         |

| 4                    | 4                    | 256                         |

| 4                    | 8                    | 512                         |

| 16                   | 1                    | 256                         |

| 16                   | 2                    | 512                         |

| 16                   | 4                    | 1024                        |

| 16                   | 8                    | 2048                        |

#### Table 4-1 Memory Array Capacity

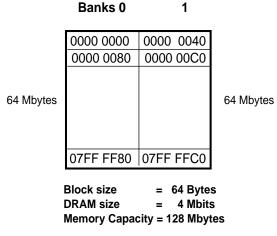

## 4.2 Memory Banking

DRAM arrays on all memory modules containing more than one string are organized as two banks, Bank 0 and Bank 1. A bank is a grouping of one or more strings that share a common address path. Each bank has its own set of control, address, and timing signals and is accessible independently. This arrangement prevents memory idling by allowing access to the second bank while the first bank is still busy.

# 4.3 Memory Interleaving

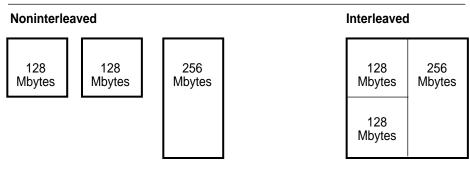

Further enhancement of memory performance can be achieved by interleaving the physical memory. Interleaving can be done at two levels: module and system.

At the module level, the DRAM arrays can be interleaved on 64-byte block boundaries. Each memory module supports 2-way interleaving when configured with a minimum of two strings. Interleaving occurs between the two independently accessible banks within a module. Figure 4-1 shows a 2-way interleaved 2-string memory module. The DRAM array in a 2string MS7AA memory module is always interleaved.

#### Figure 4-1 Two-Way Interleave of a 128-Mbyte DRAM Array

BXB-0307A-92

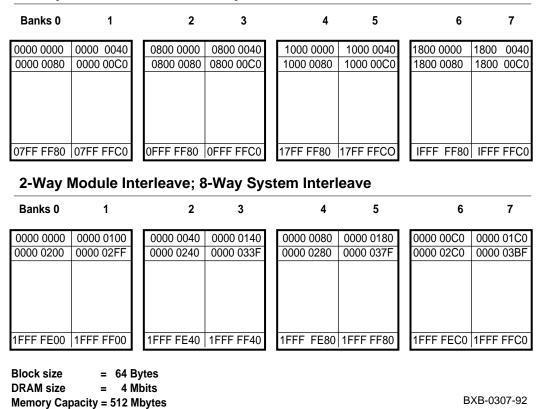

In multi-module memory subsystems, three modes of interleave are possible at the system level: default, explicit, and none. The interleave mode selection parameters are stored in the console EEPROM and can be modified through the console program. Initialization software uses registers in LSB commanders and each memory module to configure the memory interleave as specified by the EEPROM parameters. A memory configuration consisting of four memory modules supports a maximum of 8-way interleaving when each of the four modules is 2-way interleaved. The three additional modules (modules 5 to 7), if present, can be configured into the system as two modules 4-way interleaved and 1 module 2-way interleaved. Figure 4-2 shows four memory modules in an 8-way interleaved organization.

#### Figure 4-2 Eight-Way System Interleave of Four 128-Mbyte Memory Modules

#### 2-Way Module Interleave; No System Interleave

If the EEPROM specifies default interleave, the console attempts to form interleave sets so that the largest interleave factor is obtained for each group of DRAM arrays.

The default mode optimizes interleaving of memory in any arrangement of memory modules. For example, two 128-Mbyte modules can be combined to appear as a single 256-Mbyte module that can then be interleaved with a single 256-Mbyte module. In this configuration, three modules are 2-way interleaved among each other. This type of configuration yields 2-way module interleaving and 4-way system-level interleaving as shown in Figure 4-3.

## Figure 4-3 Interleaving Different Size Memory Modules

Two 128-Mbyte and One 256-Mbyte Memory Modules

BXB-0389A-92

If the EEPROM specifies explicit interleave sets, the console then interleaves the arrays as requested. In a noninterleave mode, the console configures arrays in order, by node number, with the lowest numbered array at the lowest physical address.

# Chapter 5 LSB Memory Signals

A memory module interfaces the LSB bus through a total of 173 signals. This chapter lists the LSB memory signals and describes their functions. Refer to the *Platform Technical Manual* for a complete listing of the LSB bus signals. Table 5-1 lists the LSB memory signals and identifies their functions.

#### LSB Data D<127:0>

The LSB data signals transfer command/address and data information between nodes. A memory module receives command/address cycles. It drives and receives data cycles.

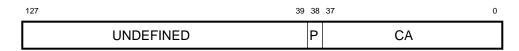

During command/address cycles, only D<38:0> contain valid information (see Figure 5-1). D<38> carries the parity bit protecting the command and address information in D<37:0>. D<127:39> contain UNDEFINED data that will be ignored.

### Figure 5-1 LSB D<127:0> During Command/Address Cycles

BXB-0266-92

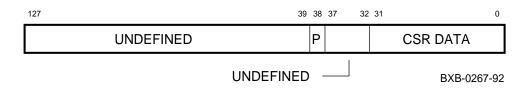

During CSR data cycles, D<31:0> transfer the CSR data. D<37:32> contain UNDEFINED data (see Figure 5-2). D<38> carries the parity bit for read and write data. A memory module checks for correct parity on CSR writes and supplies correct parity on CSR reads.

*NOTE:* Data is ignored in D<37:32>. However, memory computes CSR data cycle parity over D<37:0>. Hence, for parity checking, D<37:32> are valid.

# Figure 5-2 LSB D<127:0> During CSR Data Cycles

# Table 5-1LSB Memory Signals

| Signal                                                                             | No. of<br>Lines | Function                                                                                                                                                                                                                                                                           |

|------------------------------------------------------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| СА                                                                                 | 1               | <b>Command/Address.</b> Asserted by a bus commander to signify a command/address cycle.                                                                                                                                                                                            |

| CNF                                                                                | 1               | <b>Confirmation.</b> Asserted by the selected memory module to signify acceptance of a command/address cycle.                                                                                                                                                                      |

| D<127:0>                                                                           | 128             | <b>Data.</b> Command/address and data lines. <sup>1</sup>                                                                                                                                                                                                                          |

| DIRTY                                                                              | 1               | <b>Dirty.</b> Asserted by a CPU module to indicate that the targeted cache block has been modified more recently than the copy in memory. When asserted during a read transaction, the selected memory module aborts the transaction and does not return read data to the LSB bus. |

| ECC<27:0>                                                                          | 28              | <b>Error Checking and Correction.</b> Error correction lines for data cycles.                                                                                                                                                                                                      |

| ERR                                                                                | 1               | <b>Error.</b> Asserted when a memory module detects certain LSB and memory-related errors.                                                                                                                                                                                         |

| NID<2:0>                                                                           | 3               | <b>Node ID.</b> Hardwired lines that indicate the node ID (slot number) of the memory module.                                                                                                                                                                                      |

| PH0 (SINE)                                                                         | 1               | <b>Sine.</b> Used to generate the eight copies of the digital clock for each module.                                                                                                                                                                                               |

| REQ<9:0>                                                                           | 10<br>1         | <b>Arbitration Request.</b> Asserted by the I/O module or CPU modules to arbitrate for the LSB bus. Memory modules never assert REQ<9:0>.                                                                                                                                          |

| RESET                                                                              | 1               | <b>Reset.</b> Causes a system reset when asserted by a node.                                                                                                                                                                                                                       |

| STALL                                                                              | 1               | <b>Stall.</b> Asserted when the module is unable to accept write data or supply read data.                                                                                                                                                                                         |

| $^1$ Only D<38:0> are valid during command/address cycles and LSB CSR data cycles. |                 |                                                                                                                                                                                                                                                                                    |

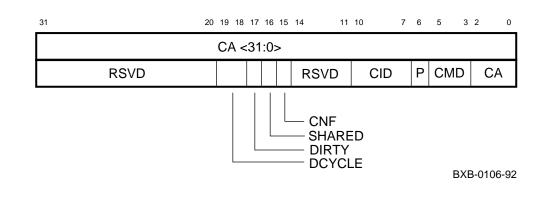

#### LSB CA

CA is asserted by an LSB commander node when it is driving a command/address cycle on the LSB. The memory module receives but never drives this signal.

#### LSB CNF

CNF is asserted by memory to confirm the acceptance of a command/address cycle to either memory or node space. The selected module asserts CNF only when the LSB address matches the module's memory or node space, and no parity errors are detected.

#### LSB D<127:0>

Command/address and data lines.

#### LSB DIRTY

Memory modules monitor LSB DIRTY. If asserted during an LSB read transaction, memory does not supply read data for the transaction associated with the assertion of LSB DIRTY. The node that asserted DIRTY supplies the read data in place of memory.

#### LSB ECC Signals ECC<27:0>

LSB ECC signals carry the longword ECC check bits protecting D<127:0> during memory space read or write data cycles.

During the four memory space write data cycles, the selected memory module receives ECC<27:0>, with write data in D<127:0>, checks and corrects ECC errors before data is written to memory. During read data cycles from memory, a module checks and corrects single-bit ECC errors before data is driven onto LSB.

During CSR data cycles, ECC<27:0> contain UNDEFINED data that is ignored.

#### LSB ERR

Memory modules monitor and assert ERR under conditions discussed in the *Platform Technical Manual.* In addition, memory asserts ERR for memory-specific error conditions. Refer to Chapter 8 for additional details.

#### LSB NID<2:0>

These three signals indicate the node ID. They are hardwired into the backplane.

#### LSB PH0 (SINE)

This is the LSB-supplied clock signal. Each memory module receives and generates multiple copies of a single-phase clock.

#### LSB REQ<9:0>

Memory modules monitor REQ<9:0> to determine when a command/ address cycle will be driven on the LSB. The *OR* of these ten signals initiates the LSB state machines and gates the address lines to the DRAMs to help reduce power consumption. The decoded DRAM ROW address is sent to all modules and all strings independent of module selection. This is done to speed access time. If a module is not selected for the transaction, or if the bus goes to the idle state, the address drivers are held in their previous state to conserve power.

#### LSB RESET

All modules monitor LSB RESET. When asserted, the module is reset to its default power-up state. The assertion of LSB RESET inhibits DRAM refresh. When LSB RESET is deasserted, all memory modules start refresh operation within a specified number of cycles.

#### LSB STALL

Memory modules monitor and assert STALL. Memory monitors STALL to ensure that it stays in sync with the bus protocol. Memory asserts STALL for two conditions:

- A module asserts STALL when it is not able to supply read data to an LSB commander at the required time due to a memory timing conflict. STALL remains asserted until the conflict is resolved and read data can be driven on the LSB. This condition occurs when a read transaction immediately follows a write transaction on the LSB to the same memory bank. In this instance nine STALLs are asserted on the LSB.

- A module asserts STALL when it cannot supply read data or accept write data due to DRAM refresh cycles. In this case 1 to 14 STALLs are asserted on the LSB.

# **Memory Transactions**

The design of the memory module architecture ensures that the command/address issued to the DRAMs is always driven on the address lines of an idle memory bank. This speeds DRAM access during reads.

## 6.1 Memory Read Transactions

During a memory read transaction, DRAM read data is driven onto the MDB bus to both MIC-A and MIC-B in four consecutive clock cycles. The memory module starts the DRAM access 1.5 cycles after a command/ address cycle.

A read transaction can be stalled by the LSB bus or by the memory module.

#### 6.1.1 LSB Stalled Read Transactions

The assertion of LSB STALL by another LSB node during memory read transactions causes the memory module to delay the release of read data to the LSB bus. The DRAM read timing is not affected by the assertion of LSB STALL. Under a stall condition, the DRAM read data is latched either in the MDC chips or is transferred to the read data buffer of the MIC. The DRAM read data remains in the MIC until LSB STALL is deasserted. Read data is driven on the LSB bus two cycles after the deassertion of LSB STALL.

## 6.1.2 Module Stalled Read Transactions

The start of the DRAM access for a memory read transaction may be delayed due to conflicts on the memory module. These conflicts result from either DRAM refresh cycles or from DRAM write and read timing.

# 6.2 Memory Write Transactions

During a memory write transaction, LSB write data is latched into the MIC. Data is then transferred from the MIC to the MDC chips through the 144-bit MDB bus in four consecutive cycles. The memory module starts DRAM access a minimum of 12 bus cycles after the command/address cycle coincident with receiving the write data.

A write transaction can be stalled by the LSB bus or by the memory module.

### 6.2.1 LSB Stalled Write Transactions

The assertion of LSB STALL by another node delays the start of the DRAM write access until after the first LSB write data has been received. Once the DRAM write has started, it is completed in four consecutive LSB cycles.

#### 6.2.2 Module Stalled Write Transactions

The memory module asserts LSB STALL to suppress the generation of write transactions to memory when conflicts on the memory module delay loading of write data into the DRAMs. The stall occurs on the third back-to-back write transaction to a single module preceded by a DRAM refresh. The memory module maintains LSB STALL assertion until the completion of the refresh cycle. When refresh has completed, the memory module deasserts LSB STALL, and the DRAM cycle for the write transaction starts.

# 6.3 Memory Transaction Ordering

In general, memory transactions are performed on a first come first served protocol. However, this protocol is overruled when a memory read follows a write transaction and targets different banks of the same memory module. In this case, the memory read transaction is always performed first to enhance system performance.

# 6.4 ECC Conversion

Memory modules convert LSB longword (32-bit) ECC into quadword (64bit) ECC that is stored with LSB data on writes. During LSB reads, quadword ECC is converted to longword ECC as required by the LSB. Quadword ECC requires fewer DRAMs per string.

# Chapter 7

# Registers

The MS7AA memory module has two groups of registers:

- LSB required registers

- Module-specific registers

LSB required registers are used for internode communication over the LSB bus. Memory-specific registers are used to perform functions unique to the memory module.

#### 7.1 Node Space Base Addresses

All memory registers reside on the memory controller interface. They are mapped to the node space as offsets to a base address (BB). The base address is implemented in hardware and depends on the node ID of the module, which is determined by the LSB slot occupied by the module. Table 7-1 gives the physical base addresses of nodes on the LSB bus for processors that support a 32-bit address range (for example, KA7AA) and a 34-bit address range (for example, KN7AA).

| Node ID |            | Physical Base Address (BB)<br>(Byte) |              |  |

|---------|------------|--------------------------------------|--------------|--|

| (Slot)  | Module     | 32-Bit Range                         | 34-Bit Range |  |

| 0       | CPU/Memory | F800 0000                            | 3 F800 0000  |  |

| 1       | CPU/Memory | F840 0000                            | 3 F840 0000  |  |

| 2       | CPU/Memory | F880 0000                            | 3 F880 0000  |  |

| 3       | CPU/Memory | F8C0 0000                            | 3 F8C0 0000  |  |

| 4       | CPU/Memory | F900 0000                            | 3 F900 0000  |  |

| 5       | CPU/Memory | F940 0000                            | 3 F940 0000  |  |

| 6       | CPU/Memory | F980 0000                            | 3 F980 0000  |  |

| 7       | CPU/Memory | F9C0 0000                            | 3 F9C0 0000  |  |

| 8       | I/O        | FA00 0000                            | 3 FA00 0000  |  |

Table 7-1

LSB Node Space Base Addresses

## 7.2 Bit Access Type Acronyms

Acronyms are used throughout register descriptions to indicate the access type of the bit(s). Table 7-2 lists those acronyms.

Table 7-2 Access Types of Register Bits

| Acronym | Access Type                                                           |

|---------|-----------------------------------------------------------------------|

| RO      | Read only; writes ignored.                                            |

| R0      | Read as zero.                                                         |

| R/W     | Read/write.                                                           |

| W1C     | Read/write one to clear; unaltered by a write of zero.                |

| W1S     | Write one to set; self-cleared; cannot be cleared by a write of zero. |

| WO      | Write only.                                                           |

## 7.3 Register Descriptions

Table 7-3 lists the memory module registers and gives the address of each register as an offset from a selected node space base address. Functional descriptions of the memory registers follow.

### Table 7-3 Memory Module Registers

| Register Name                          | Mnemonic | Address<br>(Byte Offset) |

|----------------------------------------|----------|--------------------------|

| LSB Required                           |          |                          |

| Device Register                        | LDEV     | $BB^{1} + 0000$          |

| Bus Error Register                     | LBER     | BB + 0040                |

| Configuration Register                 | LCNR     | BB + 0080                |

| Information Base Repair Register       | IBR      | BB + 00C0                |

| Error Syndrome Register 0              | LBESR0   | BB + 0600                |

| Error Syndrome Register 1              | LBESR1   | BB + 0640                |

| Error Syndrome Register 2              | LBESR2   | BB + 0680                |

| Error Syndrome Register 3              | LBESR3   | BB + 06C0                |

| Error Command Register 0               | LBECR0   | BB + 0700                |

| Error Command Register 1               | LBECR1   | BB + 0740                |

| Memory-Specific                        |          |                          |

| Memory Configuration Register          | MCR      | <b>BB</b> + 2000         |

| Address MappingRegister                | AMR      | BB + 2040                |

| Memory Self-Test Register 0            | MSTR0    | BB + 2080                |

| Memory Self-Test Register 1            | MSTR1    | BB + 20C0                |

| Failing Address Register               | FADR     | BB + 2100                |

| Memory Error Register A                | MERA     | BB + 2140                |

| Memory Error Syndrome Register A       | MSYNDA   | BB + 2180                |

| Memory Diagnostic Register A           | MDRA     | BB + 21C0                |

| Memory Check Bit Substitute Register A | MCBSA    | BB + 2200                |

| Memory Error Register B                | MERB     | BB + 4140                |

| Memory Error Syndrome Register B       | MSYNDB   | BB + 4180                |

| Memory Diagnostic Register B           | MDRB     | BB + 41C0                |

| Memory Check Bit Substitute Register B | MCBSB    | BB + 4200                |

<sup>1</sup> BB is the node space base address of the memory module in hex.

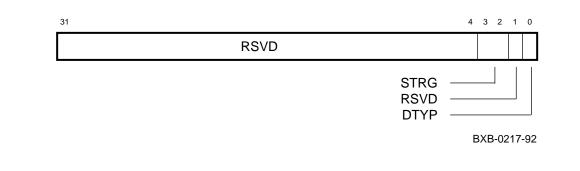

# LDEV—Device Register

AddressBB + 0000AccessR/W

# The LDEV register is loaded during initialization with information that identifies a node.

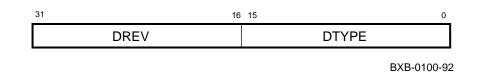

#### Table 7-4 LDEV Register Bit Definitions

| Name  | Bit(s)  | Туре | Function                                                                                                                                                                                                                                                                                                 |

|-------|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DREV  | <31:16> | R/W  | <b>Device Revision.</b> Identifies the functional revision level of the module. The value of this field is contained in the EEPROM of the memory module and is loaded into the LDEV register by console software at system initialization. For the MS7AA memory module, the value of this field is zero. |

| DTYPE | <15:0>  | R/W  | <b>Device Type.</b> Loaded at initialization with a value of 4000 (hex), which identifies the node as a memory module. The device type may be modified by console software when the device type field is fetched from the serial EEPROM located on the memory module.                                    |

## LBER—Bus Error Register

| Address | BB + 0040 |

|---------|-----------|

| Access  | R/W       |

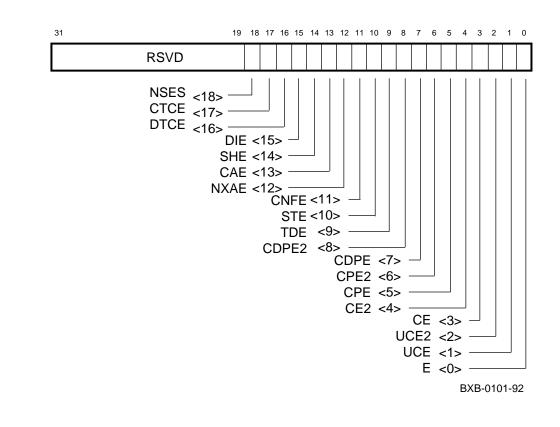

The LBER register stores the error bits that are flagged in memory operations and logs the failing commander ID. The status of this register remains locked until software resets the error bit(s).

## Table 7-5 LBER Register Bit Definitions

| Name  | Bit(s)  | Туре   | Function                                                                                                            |

|-------|---------|--------|---------------------------------------------------------------------------------------------------------------------|

| RSVD  | <31:19> | R/W, 0 | Reserved.                                                                                                           |

| NSES  | <18>    | RO, 0  | <b>Node-Specific Error Summary</b> . Set when one of bits <11>, <10>, <9>, <5>, or <4> of the MERA register is set. |

| CTCE  | <17>    | W1C, 0 | <b>Control Transmit Check Error.</b> Not imple-<br>mented on memory.                                                |

| DTCE  | <16>    | W1C, 0 | <b>Data Transmit Check Error.</b> Not implemented on memory.                                                        |

| DIE   | <15>    | W1C, 0 | DIRTY Error.                                                                                                        |

| SHE   | <14>    | W1C, 0 | SHARED Error. Not implemented on memory.                                                                            |

| CAE   | <13>    | W1C, 0 | Command/Address Error.                                                                                              |

| NXAE  | <12>    | W1C, 0 | Nonexistent Address Error. Not implemented on memory.                                                               |

| CNFE  | <11>    | W1C, 0 | CNF Error.                                                                                                          |

| STE   | <10>    | W1C, 0 | STALL Error.                                                                                                        |

| TDE   | <9>     | W1C, 0 | Transmitter During Error.                                                                                           |

| CDPE2 | <8>     | W1C, 0 | Second CSR Data Parity Error. Not imple-<br>mented on memory.                                                       |

| CDPE  | <7>     | W1C, 0 | <b>CSR Data Parity Error.</b> Not implemented on memory.                                                            |

| CPE2  | <6>     | W1C, 0 | Second Command Parity Error.                                                                                        |

| CPE   | <5>     | W1C, 0 | Command Parity Error.                                                                                               |

| CE2   | <4>     | W1C, 0 | Second Correctable Data Error.                                                                                      |

| CE    | <3>     | W1C, 0 | Correctable Data Error.                                                                                             |

| UCE2  | <2>     | W1C, 0 | Second Uncorrectable Data Error.                                                                                    |

| UCE   | <1>     | W1C, 0 | Uncorrectable Data Error.                                                                                           |

| Е     | <0>     | W1C, 0 | Error. Signals assertion of error line.                                                                             |

# LCNR— Configuration Register

| Address | BB + 0080 |

|---------|-----------|

| Access  | R/W       |

# The LCNR register contains LSB systemwide configuration setup and status information.

| Table 7-6 LC | IR Register Bit Definition | ons |

|--------------|----------------------------|-----|

|--------------|----------------------------|-----|

| Name    | Bit(s) | Туре   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|--------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

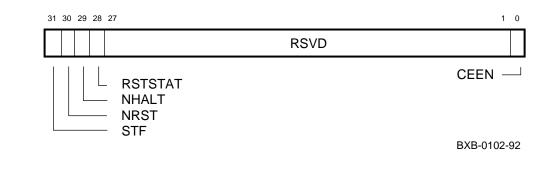

| STF     | <31>   | R/W, 1 | <b>Self-Test Fail.</b> When set, indicates that this node has not yet completed self-test. Memory clears this bit at the completion of self-test regardless of defective locations found in the DRAM array.                                                                                                                                                                                                                                                                                                                                                           |

| NRST    | <30>   | WO, 0  | <b>Node Reset.</b> When set, the node enters console mode<br>and undergoes a reset sequence. CSRs are reset to their<br>initialized state. Any pending transactions are lost or<br>left uncompleted. Memory self-test halts, if running,<br>and does not restart. An internally generated reset sig-<br>nal remains asserted for 16 LSB bus cycles after NRST<br>is set, providing sufficient time to reset memory state<br>and clear NRST. If NRST is set, a value of zero must be<br>written to the MDRA register; otherwise, the memory<br>operation is UNDEFINED. |

| NHALT   | <29>   | R0     | Node Halt. Not implemented on memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RSTSTAT | <28>   | R0     | <b>Reset Status.</b> Not implemented on memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| RSVD    | <27:1> | R0     | Reserved. Read as zero.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CEEN    | <0>    | R/W, 0 | <b>Correctable Error Detection Enable</b> . When set, enables detection of correctable errors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

## **IBR**—Information Base Repair Register

AddressBB + 00C0AccessR/W

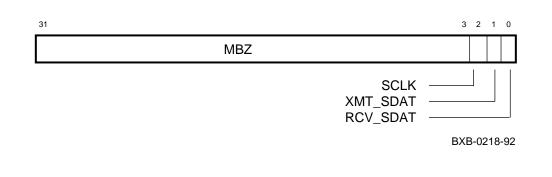

The IBR register is used to access the EEPROM on the LSB memory and I/O modules. The EEPROM access is accomplished through continual updates of this register by software.

| Table 7-7 | <b>IBR Register Bit Definitions</b> |

|-----------|-------------------------------------|

|-----------|-------------------------------------|

| Name     | Bit(s) | Туре   | Function                                                                                                                                                                                                                                             |

|----------|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MBZ      | <31:3> | R/W, 0 | Must Be Zero. Must always be written as zero.                                                                                                                                                                                                        |

| SCLK     | <2>    | R/W, 0 | <b>Serial Clock.</b> Used by software to implement the EEPROM serial clock interface. When this bit is written with a one, the EEPROM serial clock input is forced to logic high. When it is cleared, the serial clock input is forced to logic low. |

| XMT_SDAT | <1>    | R/W, 1 | <b>Transmit Serial Data.</b> Used by software to assert the serial data line of the EEPROM to either high or low logic levels. This bit is used with SCLK to transfer command/address and write data to the EEPROM.                                  |

| RCV_SDAT | <0>    | RO, 1  | <b>Receive Serial Data.</b> Returns the status of the EEPROM serial data line. Used by software to receive serial read data and EEPROM responses. XMT_SDAT must be one to receive an EEPROM response or serial read data.                            |

## LBESR0-3—Error Syndrome Registers

| Address | BB + 0600 to 06C0 |

|---------|-------------------|

| Access  | RO                |

The LBESR registers contain the syndrome computed from data received on the LSB D and ECC fields during the cycle when an error was detected. These registers are locked upon the first ECC detected error and remain locked until all LSB ECC error bits in LBER are cleared.

| 31 7 | 6 0    |

|------|--------|

| RSVD | SYND_0 |

| RSVD | SYND_1 |

| RSVD | SYND_2 |

| RSVD | SYND_3 |

BXB-0105-92

| Table 7-8 | LBESR Register Bit Definitions |

|-----------|--------------------------------|

|-----------|--------------------------------|

| Name   | Bit(s) | Туре  | Function                                                                                |

|--------|--------|-------|-----------------------------------------------------------------------------------------|

| RSVD   | <31:7> | R0    | Reserved. Read as zero.                                                                 |

| SYND_0 | <6:0>  | RO, 0 | <b>Syndrome 0</b> . Syndrome computed from D<31:0> and ECC<6:0> during error cycle.     |

| SYND_1 | <6:0>  | RO, 0 | <b>Syndrome 1</b> . Syndrome computed from D<63:32> and ECC<13:7> during error cycle.   |

| SYND_2 | <6:0>  | RO, 0 | <b>Syndrome 2</b> . Syndrome computed from D<95:33> and ECC<20:14> during error cycle.  |

| SYND_3 | <6:0>  | RO, 0 | <b>Syndrome 3</b> . Syndrome computed from D<127:96> and ECC<27:21> during error cycle. |

## LBECR0,1—Error Command Registers

Address

BB + 0700 and BB + 0740

Access

RO