# RAM Buffer (RB2) Specification

Farhad Fouladi Shyamoli Banerjee

**Revision 2.3**

**Silicon Graphics Confidential**

#### 1.0 Device Introduction

#### 1.1 Part Name and Number

Part Name: RAM Buffer2 (RB2)

SGI Part Number: Vendor:LSI Logic Vendor Part Number:

Process Design Technology: LCA 100K

Package: 100-pin PQFP

Number of gates:5K gates (approx.)

### 1.2 General Description

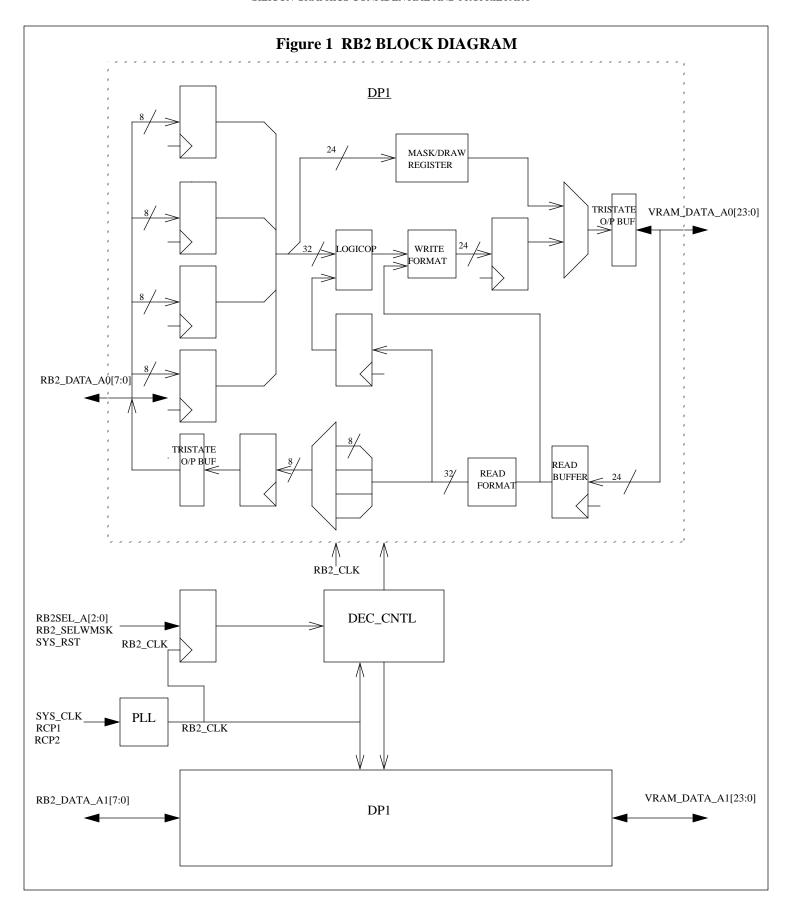

The RB2 is a gate array located between the Raster Engine (REX3) and graphics memory. RB2 contains the read/write formatter and LogicOp funtions of the pixel pipe. The front end of the pixel pipe is in REX3. This document specifies the functionality, timing requirements and pinout of the RB2. A block diagram of the RB2 is attached as Figure 1.

RB2 is designed with LCA 100K CMOS technology, operates at a maximum clock rate of 66MHz and is housed in a 100-pin plastic quad flat pack. The chip has 11 input pins, 2 output pins, 64 bidirects and 23 power and ground pins which add up to a total of 100 pins.

#### 1.3 Additional Documentation

Newport Graphics Subsystem Specification Rev. 1.0

REX3 specification. Rev 0.1

### 2.0 Device Interface

### 2.1 Pin Description

Refer to Figure 2.1 for a logical pin diagram of RB2. The table describes each pin, defined as type Input or Output and specifies output drive in milliamps. Total pin count is 100 pins.

| Pin Name               | Туре | Function                                                                                                                                                   | <b>Output Drive</b> |

|------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| RB2_DATA_A0[7:0]       | I/O  | Data bus between REX3 and RB2. The data on this bus is read from/written to BankA, VRAM0 of Frame Buffer.                                                  | 4mA                 |

| RB2_DATA_A1[7:0]       | I/O  | Data bus between REX3 and RB2. The data on this bus is read from/written to BankA, VRAM1 of Frame Buffer.                                                  | 4mA                 |

| RB2_SELWMSK_A          | I    | This signal selects whether data from write mask register or write data register gets driven on VRAM data bus. It is driven by the RAS_N signal from REX3. |                     |

| RB2SEL_A[2:0]          | I    | These three bits specify the function that has to be executed by RB2 in the next cycle. The various functions are detailed in Chapter 4.                   |                     |

| SYS_RST                | I    | On power-up reset, the state machines, etc. are reset.                                                                                                     |                     |

| SYS_CLK                | I    | 33MHz system clock.                                                                                                                                        |                     |

| VRAM_DATA_A0[23:0]     | I/O  | Data bus between Frame Buffer and RB2. The data on this bus is read from/written to BankA, VRAM0.                                                          | 4mA                 |

| VRAM_DATA_A1[23:0]     | I/O  | Data bus between Frame Buffer and RB2. The data on this bus is read from/written to BankA, VRAM1.                                                          | 4mA                 |

| RCP1                   | 0    | Phase detector output.                                                                                                                                     |                     |

| RCP2                   | I    | PLL VCO input.                                                                                                                                             |                     |

| TEST PINS:             |      |                                                                                                                                                            |                     |

| TEI/ IDDTN             | ı    | I/O pin tri-state enable/ PLL IDDTN pin.                                                                                                                   |                     |

| PTREE/ PLLCTRO         | 0    | Parametric NAND tree output/ PLL test mode counter output.                                                                                                 |                     |

| PLL_TSTMD              | I    | When asserted, this pin puts the PLL in test mode.                                                                                                         |                     |

| PLL_TSTCLK             | I    | PLL test mode clock input.                                                                                                                                 |                     |

| PLL_RESET_N            | I    | PLL reset signal.                                                                                                                                          |                     |

| POWER AND GROUND PINS: |      |                                                                                                                                                            |                     |

| VDD                    |      | +5v supply pins.                                                                                                                                           |                     |

| VSS                    |      | 0v supply pins.                                                                                                                                            |                     |

| PLLVDD                 |      | PLL power pin.                                                                                                                                             |                     |

| PLLVSS                 |      | PLL ground pin.                                                                                                                                            |                     |

| PLLAGND                |      | PLL analog ground.                                                                                                                                         |                     |

VCC VRAM\_DATA\_A0[23:0] RB2\_DATA\_A0[7:0] . VRAM\_DATA\_A1[23:0] RB2\_DATA\_A1[7:0] . RCP1 RB2\_SELWMSK RB2 RCP2 RB2SEL\_A[2:0]  $SYS\_CLK$ PTREE/ PLLCTRO TEI/ IDDTN SYS\_RST PLL\_TSTMD PLL\_TSTCLK PLL\_RESET\_N PLLVDD PLLVSS PLLAGND

Figure 2.1 Logical pin diagram of RB2

### 3.0 System Interface

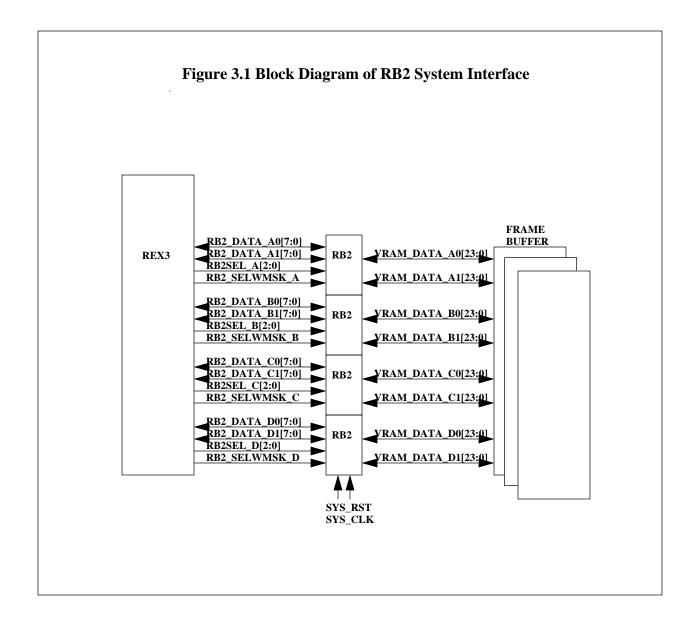

#### 3.1 REX3 - RB2 Interface

The interface between RB2 and REX3 runs at 1/4 the page mode cycle or 15 ns(66 MHZ.). Every clock 8-bits of data is transferred between REX3 and RB2. For VRAM write, after 4 clocks the full 32 bits are latched into the RB2 and are then ready to be moved into the pixel pipe. For VRAM read, 24-bits of data are read from VRAM bus, re-formatted to RGBA format by READ Format Block and sent out 8-bits at a time to REX3 via the RB2\_DATA bus.

#### 3.2 RB2 - VRAM Interface

This is the RB2 interface with the frame buffer(VRAM). Each bank of memory can perform a page mode read or a page mode write of two adjacent pixels in 60 ns. When reading or writing pixels at the maximum rate, each memory bank must receive a new 24-bit data every 60 ns.

#### 3.3 Tester Interface

RB2 does not have ATPG or JTAG testing capability. The only test pins are for parametric and PLL tests.

TEI/IDDTN disables the output drivers of the bi-directional buffers for parametric test and PTREE/PLLCTRO is the output of the parametric NAND tree. The on chip Phase Lock Loop requires 5 pins for testing: PLL\_RESET\_N which resets the PLL, PLL\_TSTMD which places the PLL into Test Mode, PLL\_TSTCLK is the PLL test mode clock input, PTREE/PLLCTRO is the PLL test mode counter output and TEI/IDDTN, PLL IDD test enable which is used used for PLL testing at LSI.

### 4.0 Functional Description

The data (color and alpha) from REX3 is first latched into the RB2, go down the pixel pipe and is processed depending upon the function specified by RB2SEL[2:0] and draw register and is finally written into the memory.

The pixel pipe in RB2 consists of LogicOp function and read and write formatter.

Since there are 8 pixel ports (2 pixels per bank), four RB2s are required with two of these pixel ports located in each RB2. The datapaths for the two pixel ports and the pixel processor pipes, inside the RB2 chip, are identical. The four RB2 chips interface to BankA, BankB, BankC and BankD of the frame buffer. Each RB2 requires 70 signal pins.

#### 4.1 Function Selection

The function select pins of the RB2 (RB2SEL[2:0]) are decoded by the Dec\_Cntl block and control signals are generated to execute the specified function. These bits are pipelined as shown on the block diagram so that the value of RB2SEL[2:0] at the input of RB2 apply to data 1 clock later.

| RB2SEL[2:0] | Operation                                             |

|-------------|-------------------------------------------------------|

| 000         | none                                                  |

| 001         | WRITE pixel plane or low pixel of OLAY/CID/PUP plane. |

| 010         | WRITE high pixel of OLAY/CID/PUP plane.               |

| 011         | LOAD write mask and draw register.                    |

| 100         | READ pixel plane or low pixel of OLAY/CID/PUP plane.  |

| 101         | READ high pixel of OLAY/CID/PUP plane.                |

| 110         | CID CHECK: READ low pixel of CID plane.               |

| 111         | CID CHECK: READ high pixel of CID plane.              |

Table 1. RB2\_BSEL[2:0] Definition

#### 4.2 Draw Register / Write Mask Register

The RB2 has a 24-bit write mask register and a 12-bit draw register. The write mask register is in the datapath corresponding to sub-bank0 and the draw register is in the datapath corresponding to sub-bank1. These registers are written into simultaneously by REX3 (RB2\_DATA\_A0 and RB2\_DATA\_A1) by asserting RB2SEL[2:0]= '011' and cannot be read. The data from write mask register is sent out to the VRAMs during RAS pre-charge time.

The draw register bits are defined as follows:

| bit11 | bit10 | bit9   | bit [8:6]    | bit[5:4]       | bit[3:0]     |

|-------|-------|--------|--------------|----------------|--------------|

| fast  | rgb   | dblsrc | planes (2:0) | drawdepth(1:0) | logicop(3:0) |

| clear | mode  |        |              |                |              |

<sup>•</sup> Fast Clear: Active HI signal. When this signal is HI, column mask is passed through the write formatter without any change, to the VRAM bus.

- RGB mode: Active HI. Selects RGB (vs. Color Index) pixel format.

- DBLSRC: Pixels read from source buffer of VRAM, (0=buffer0, 1=buffer1) are in double buffer mode.

- Planes(2:0): Specifies which frame buffer planes are enabled for R/W.

| Planes[2:0] | Function           |

|-------------|--------------------|

| 000         | none               |

| 001         | R/W RGB/CI planes. |

| 010         | R/W RGBA planes.   |

| 011         | X                  |

| 100         | R/W OLAY planes.   |

| 101         | R/W PUP planes     |

| 110         | R/W CID planes.    |

| 111         | X                  |

• Drawdepth(1:0): This is the drawn depth of framebuffer planes, not including alpha.

| drawdepth[1:0] | Depth    |

|----------------|----------|

| 00             | 4 bits.  |

| 01             | 8 bits.  |

| 10             | 12 bits. |

| 11             | 24 bits. |

• Logicop: This is discussed in the following section.

### 4.3 LogicOp

Draw\_register[3:0] defines the logic operation to be performed between the pixels being iterated(source pixels) and the pixels from the frame buffer(destination pixels) to generate the resultant destination pixels to be written into the frame buffer. Logical Operations are disabled when LogicOp = "0011".

LogicOp is defined defined by the following table:

| Value | Name         | Operation         |

|-------|--------------|-------------------|

| 0000  | Clear        | 0                 |

| 0001  | And          | src AND dst       |

| 0010  | AndReverse   | src AND (NOT dst) |

| 0011  | Сору         | src               |

| 0100  | AndInverted  | (NOT src) AND dst |

| 0101  | Noop         | dst               |

| 0110  | Xor          | src XOR dst       |

| 0111  | Or           | src OR dst        |

| 1000  | Nor          | NOT (src OR dst)  |

| 1001  | Equiv        | NOT (src XOR dst) |

| 1010  | Invert       | NOT dst           |

| 1011  | OrReverse    | src OR (NOT dst)  |

| 1100  | CopyInverted | NOT src           |

| 1101  | Orlnverted   | (NOT src) OR dst  |

| 1110  | Nand         | NOT (src AND dst) |

| 1111  | Set          | 1                 |

Table 4.3. LOGICOP[3:0] Definition

#### 4.4 Write Format Block

The pixels coming out of the Logicop block are write formatted depending on the bits specified in the draw register. The different write formats are specified in Table 4.4 at the end of the chapter.

#### 4.5 Read Format Block

Data read back from the frame buffer are formatted by this block. It is the reverse of write formatting in that it takes 24-bits in frame buffer format and converts it to 32-bits RGBA. The read format is specified by dblsrc, drawdepth bits of draw register and also whether it is CID check and whether access is to CID/PUP/OLAY planes of frame buffer.

#### 4.6 RB2-VRAM bus source control

The RB2\_SELWMSK controls a 2 to 1 multiplexer that chooses between the writemask register and the write data register. Table 4.6 shows the encoding of this signal. The RAS signal will be connected to this pin , so that when RAS is high the write mask register is presented to the VRAMs and when RAS goes low the write data register will be sourced to the output pins. The RB2\_SELWMSK is clocked before it is used internally. RB2\_WRITE signal is driven by DEC\_CNTL block by decoding RB2SEL\_A[2:0].

| RB2_WRITE | RB2_SELWMSK | RB2-VRAM bus        |

|-----------|-------------|---------------------|

| 1         | 0           | write data register |

| 1         | 1           | write mask register |

| 0         | X           | tristate            |

Table 4.6. RB2\_SELWMSK definition

### 4.7 Decode and Control block

The DEC\_CNTL block decodes the reclocked versions of the RB2SEL\_A[2:0], RB2\_SELWMSK input pins and draw register bits and generates load enable signals for the pipeline registers, the tristate enable for the bidirectional buses and control signals for Logicop, Read Format and Write Format blocks. This block also includes the state machines needed to generate a number of the above mentioned control signals.

#### 4.8 RB2 clock

In order to minimize on-chip clock skew between REX3 and RB2, a 33MHz system clock (SYS\_CLK) is applied to the input of a PLL circuit in the RB2 and REX3 chips. The PLL, while tracking the system clock to minimize skew, also multiplies the input frequency by a factor of 2 to 66MHz which is then used as the internal clock (RB2\_CLK) at which the RB2 operates.

### 4.9 Chip Reset and Initialization

When SYS\_RST signal is asserted, all state machines in RB2 are reset to IDLE state.

| BIT<br>PLANES | PIXEL TYPE                                    | D<br>2<br>3      | D<br>2<br>2      | D<br>2<br>1 | D<br>2<br>0      | D<br>1<br>9      | D<br>1<br>8      | D<br>1<br>7 | D<br>1<br>6      | D<br>1<br>5      | D<br>1<br>4      | D<br>1<br>3      | D<br>1<br>2 | D<br>1<br>1      | D<br>1<br>0      | D<br>9      | D<br>8      | D<br>7      | D<br>6      | D<br>5      | D<br>4      | D<br>3      | D<br>2      | D<br>1      | D<br>0      |

|---------------|-----------------------------------------------|------------------|------------------|-------------|------------------|------------------|------------------|-------------|------------------|------------------|------------------|------------------|-------------|------------------|------------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| 24            | RGB-SB<br>24BIT                               | B<br>0           | R<br>0           | G o         | B<br>1           | R<br>1           | G<br>1           | B<br>2      | R<br>2           | G<br>2           | B<br>3           | R<br>3           | G<br>3      | B<br>4           | R<br>4           | G<br>4      | B<br>5      | R<br>5      | G<br>5      | B<br>6      | R<br>6      | G<br>6      | B<br>7      | R<br>7      | G<br>7      |

| 24            | RGB-DB<br>444+444                             | B<br>4           | R<br>4           | G<br>4      | B<br>5           | R<br>5           | G<br>5           | B<br>6      | R<br>6           | G<br>6           | B<br>7           | R<br>7           | G<br>7      | B<br>4           | R<br>4           | G<br>4      | B<br>5      | R<br>5      | G<br>5      | B<br>6      | R<br>6      | G<br>6      | B<br>7      | R<br>7      | G<br>7      |

| 24            | CI-SB<br>12BIT                                | -                | -                | -           | -                | -                | -                | -           | -                | -                | -                | -                |             | I<br>1<br>1      | I<br>1<br>0      | I<br>9      | I<br>8      | 1<br>7      | I<br>6      | 1<br>5      | I<br>4      | 1<br>3      | 1<br>2      | I<br>1      | I<br>0      |

| 24            | CI-DB<br>12+12                                | I<br>1<br>1      | I<br>1<br>0      | I<br>9      | 1<br>8           | 1<br>7           | I<br>6           | 1<br>5      | I<br>4           | 1<br>3           | 1<br>2           | 1<br>1           | 0           | I<br>1<br>1      | I<br>1<br>0      | I<br>9      | I<br>8      | 1<br>7      | I<br>6      | 1<br>5      | I<br>4      | 1<br>3      | 1<br>2      | I<br>1      | I<br>0      |

| 8/24          | RGB-SB<br>8BIT 332                            | -                | -                | -           | -                | -                | -                | -           | -                | -                | -                | -                |             | -                | -                | -           | -           | R<br>5      | G<br>5      | B<br>6      | R<br>6      | G<br>6      | B<br>7      | R<br>7      | G<br>7      |

| 8/24          | RGB-DB<br>8BIT<br>121+121                     | -                | -                | -           | -                | -                | -                | -           | -                | -                | -                | -                |             | -                | -                | -           | -           | G<br>6      | B<br>7      | R<br>7      | G<br>7      | G<br>6      | B<br>7      | R<br>7      | G<br>7      |

| 8/24          | CI-SB<br>8BIT                                 | -                | -                | -           | -                | -                | -                | -           | -                | -                | -                | -                |             | -                | -                | -           | -           | 1<br>7      | I<br>6      | 1<br>5      | I<br>4      | 1<br>3      | 1<br>2      | I<br>1      | I<br>0      |

| 8/24          | CI-DB<br>4+4                                  | -                | -                | -           | -                | -                | -                | -           | -                | -                | -                | -                |             | -                | -                | -           | -           | 1<br>3      | 1<br>2      | I<br>1      | I<br>0      | 1<br>3      | 1<br>2      | I<br>1      | I<br>0      |

| 24            | RGBα - DB<br>3324 + 3324                      | α<br>4           | α<br>5           | α<br>6      | α<br>7           | R<br>5           | G<br>5           | B<br>6      | R<br>6           | G<br>6           | B<br>7           | R<br>7           | G<br>7      | α<br>4           | α<br>5           | α<br>6      | α<br>7      | R<br>5      | G<br>5      | B<br>6      | R<br>6      | G<br>6      | B<br>7      | R<br>7      | G<br>7      |

| 24            | RGBα - SB<br>444 8                            | -                | -                | -           | -                | α<br>0           | α<br>1           | α<br>2      | α<br>3           | α<br>4           | α<br>5           | α<br>6           | α<br>7      | B<br>4           | R<br>4           | G<br>4      | B<br>5      | R<br>5      | G<br>5      | B<br>6      | R<br>6      | G<br>6      | B<br>7      | R<br>7      | G<br>7      |

| 24            | CID/AUX<br>2BITS-CID<br>2BITS-PUP<br>8BIT AUX | A<br>8<br>7      | A<br>8<br>6      | A<br>8<br>5 | A<br>8<br>4      | A<br>0<br>7      | A<br>0<br>6      | A<br>0<br>5 | A<br>0<br>4      | A<br>8<br>3      | A<br>8<br>2      | A<br>8<br>1      | A<br>8<br>0 | A<br>0<br>3      | A<br>0<br>2      | A<br>0<br>1 | A<br>0<br>0 | P<br>8<br>1 | P<br>8<br>0 | C<br>8<br>1 | C<br>8<br>0 | P<br>0<br>1 | P<br>0<br>0 | 0<br>1      | C<br>0<br>0 |

| 24            | CID/AUX<br>2BITS-CID<br>2BITS-PUP<br>4+4 AUX  | A<br>8<br>1<br>3 | A<br>8<br>1<br>2 | A<br>8<br>1 | A<br>8<br>1<br>0 | A<br>0<br>1<br>3 | A<br>0<br>1<br>2 | A<br>0<br>1 | A<br>0<br>1<br>0 | A<br>8<br>0<br>3 | A<br>8<br>0<br>2 | A<br>8<br>0<br>1 | A 8 0 0     | A<br>0<br>0<br>3 | A<br>0<br>0<br>2 | A<br>0<br>0 | A<br>0<br>0 | P<br>8<br>1 | P<br>8<br>0 | C<br>8<br>1 | C<br>8<br>0 | P<br>0<br>1 | P 0 0       | C<br>0<br>1 | C<br>0<br>0 |

| 8             | 2BITS-CID<br>2BITS-PUP                        | -                | -                | -           | -                | -                | -                | -           | -                | -                | -                | -                | -           | -                | -                | -           | -           | P<br>8<br>1 | P<br>8<br>0 | C<br>8<br>1 | C<br>8<br>0 | P<br>0<br>1 | P<br>0<br>0 | C<br>0<br>1 | C<br>0<br>0 |

NOTES: R - Red, G - Green, B - Blue, In - Color index,  $C_{p,n}$  - CIDpixel, bit field,  $P_{p,n}$  - PUPpixel, bit field,  $A_{p,(b),n}$  - OLAYpixel, (buffer), bit field,  $\alpha_n$  - Alpha

Table 4.4. Frame Buffer pixel formats

### 5.0 Device Characteristics

### 5.1 Absolute Maximum Ratings

Stresses beyond those listed may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those listed in the operating range section of this specification is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

| Ambient Operating Temperature with voltage applied (Junction temperature not to exceed ambient temperature by more than 20 ° C.) | -40 °C to + 85 °C |

|----------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Storage Temperature                                                                                                              | -40 °C            |

| Supply Voltage                                                                                                                   | -0.50 V to +6.00V |

| Input Voltage                                                                                                                    | -0.50 V to +5.50V |

| DC Input Current                                                                                                                 | 20 mA             |

| Lead Temperature                                                                                                                 | 300 °C            |

Table 5.1 Absolute maximum ratings

#### 5.2 Recommended Operating Range

| Ambient Operating Temperature with voltage applied                            | 0 °C to + 70 °C  |

|-------------------------------------------------------------------------------|------------------|

| (Junction temperature not to exceed ambient temperature by more than 20 ° C.) |                  |

| VDD Supply Voltage (VSS = 0.00 V)                                             | +4.75 V to +5.25 |

Table 5.2 Operating range

#### 5.3 DC Characteristics

| Parameter | Description            | Description Test Condition Min |         |         |    |

|-----------|------------------------|--------------------------------|---------|---------|----|

| VIL       | Low Input Voltage      |                                |         | 0.3 VDD | V  |

| VIH       | High Input Voltage     |                                | 0.7 VDD |         | V  |

| Vol       | Low Output Voltage     | IOL = 8.0 mA                   |         | 0.4     | V  |

| Voн       | High Output Voltage    | IOH = -8.0mA                   | 2.4     |         | V  |

| II∟       | Input Leakage Current  | VIN = VDD or VSS               | -10     | 10      | μΑ |

| loz       | Output Leakage Current | Vout = Vss or Vdd              | -10     | 10      | μΑ |

| Соит      | Output Capacitance     |                                |         | 10      | pF |

Table 5.3 DC characteristics

### 5.4 AC Characteristics

| Name     | Description                                       | Min  | Max  |

|----------|---------------------------------------------------|------|------|

| tVOUT    | Clock to output delay of RB2-VRAM bus             | 3ns  | 13ns |

| tVSU     | Setup time with respect to clock for RB2-VRAM bus | 2ns  |      |

| t∨H      | Hold time with respect to clock for RB2-VRAM bus  | 1ns  |      |

| tROUT    | Clock to output delay of RB2-REX3 bus             | 2ns  | 13ns |

| tRSU     | Setup time for signals latched by RB2_CLK         | 1ns  |      |

| tRH      | Hold time for signals latched by RB2_CLK          | 3ns  |      |

| tRB2_CLK | Clock period of RB2_CLK (internal clock)          | 15ns |      |

Table 5.4 Timing Requirements

### Notes:

Load on RB2-VRAM bus is 30pf. Load on RB2-REX3 bus is 25pf. Worst case operating conditions are Vcc = 4.75V and Tj = 110 C.

# 6.0 Revision History

.

# **APPENDIX 1**

# **RB2 TIMING DIAGRAMS**