# OpenVMS VAX Device Support Manual

Order Number: AA-PWC8A-TE

#### March 1994

This manual describes how to write a driver for a device connected to a VAX processor. It discusses the required and optional components of a driver and explains their functions. It details the requirements the operating system imposes upon driver code and includes guidelines for creating, loading, and debugging a driver that can run on OpenVMS uniprocessing and multiprocessing systems.

| Revision/Update Information: | This manual supersedes the <i>OpenVMS</i><br><i>VAX Device Support Manual</i> , Version<br>6.0. |

|------------------------------|-------------------------------------------------------------------------------------------------|

| Software Version:            | OpenVMS VAX Version 6.1                                                                         |

Digital Equipment Corporation Maynard, Massachusetts

#### March 1994

Digital Equipment Corporation makes no representations that the use of its products in the manner described in this publication will not infringe on existing or future patent rights, nor do the descriptions contained in this publication imply the granting of licenses to make, use, or sell equipment or software in accordance with the description.

Possession, use, or copying of the software described in this publication is authorized only pursuant to a valid written license from Digital or an authorized sublicensor.

© Digital Equipment Corporation 1994. All rights reserved.

The postpaid Reader's Comments forms at the end of this document request your critical evaluation to assist in preparing future documentation.

The following are trademarks of Digital Equipment Corporation: BI, Bookreader, CI, CMI, DEC, DECnet, Digital, MASSBUS, MicroVAX, MSCP, NMI, OpenVMS, Q-bus, Q22-bus, SBI, TMSCP, TURBOchannel, UNIBUS, VAX, VAXBI, VAXcluster, VAX DOCUMENT, VAX MACRO, VAXstation, VMS, and the DIGITAL logo.

The following are third-party trademarks:

UNIX is a registered trademark licensed exclusively by X/Open Co. Ltd.

Internet is a registered trademark of Internet, Inc.

All other trademarks and registered trademarks are the property of their respective holders.

ZK5502

This document is available on CD-ROM.

This document was prepared using VAX DOCUMENT Version 2.1.

#### Send Us Your Comments

We welcome your comments on this or any other OpenVMS manual. If you have suggestions for improving a particular section or find any errors, please indicate the title, order number, chapter, section, and page number (if available). We also welcome more general comments. Your input is valuable in improving future releases of our documentation.

You can send comments to us in the following ways:

- Internet electronic mail: OPENVMSDOC@ZKO.MTS.DEC.COM

- Fax: 603-881-0120 Attn: OpenVMS Documentation, ZK03-4/U08

- A completed Reader's Comments form (postage paid, if mailed in the United States), or a letter, via the postal service. Two Reader's Comments forms are located at the back of each printed OpenVMS manual. Please send letters and forms to:

Digital Equipment Corporation Information Design and Consulting OpenVMS Documentation 110 Spit Brook Road, ZKO3-4/U08 Nashua, NH 03062-2698 USA

You may also use an online questionnaire to give us feedback. Print or edit the online file SYS\$HELP:OPENVMSDOC\_SURVEY.TXT. Send the completed online file by electronic mail to our Internet address, or send the completed hardcopy survey by fax or through the postal service.

Thank you.

# Contents

## Part I OpenVMS VAX Device Driver Environment

#### 1 Introduction to Device Drivers

| 1.1     | Driver Functions                                            | 1–2  |

|---------|-------------------------------------------------------------|------|

| 1.2     | Driver Components                                           | 1–2  |

| 1.2.1   | Driver Tables                                               | 1–2  |

| 1.2.2   | Driver Routines                                             | 1–3  |

| 1.3     | I/O Database                                                | 1–4  |

| 1.3.1   | Driver Tables                                               | 1–4  |

| 1.3.2   | Data Structures                                             | 1–4  |

| 1.3.3   | I/O Request Packets                                         | 1–6  |

| 1.4     | Synchronization of Driver Activity                          | 1–6  |

| 1.5     | Driver Context                                              | 1–7  |

| 1.5.1   | Example of Driver Context-Switching                         | 1–8  |

| 1.6     | Hardware Considerations                                     | 1–9  |

| 1.6.1   | Driver Dependency on VAX Processing Systems                 | 1–10 |

| 1.6.1.1 | Address Space                                               | 1–10 |

| 1.6.1.2 | VAX-11/780, VAX-11/785, and VAX 8600/8650 Systems           | 1–11 |

| 1.6.1.3 | VAX-11/750 System                                           | 1–12 |

| 1.6.1.4 | VAX-11/730 System                                           | 1–14 |

| 1.6.1.5 | VAX 82x0/83x0, VAX 85x0/8700/88x0, and VAX 6000 Series      |      |

|         | Systems                                                     | 1–14 |

| 1.6.1.6 | VAX 9000 Series System                                      | 1–17 |

| 1.6.1.7 | VAX 7000 Series and VAX 10000 Series Systems                | 1–19 |

| 1.6.1.8 | MicroVAX 3400/3600/3900 Series, MicroVAX/VAXstation II, and |      |

|         | VAX 4000 Series Systems                                     | 1–21 |

| 1.6.1.9 | MicroVAX/VAXstation 3100 and VAXstation 3520/3540           |      |

|         | Systems                                                     | 1–22 |

| 1.7     | Programmed-I/O and Direct-Memory-Access Transfers           | 1–24 |

| 1.7.1   | Programmed I/O                                              | 1–24 |

| 1.7.2   | Direct-Memory-Access I/O                                    | 1–24 |

| 1.8     | Buffered and Direct I/O                                     | 1–25 |

| 1.9     | Example of an I/O Request                                   | 1–26 |

## 2 Handling a \$QIO Request

| 2.1  | Driver Code for the LP11 Write Function          | 2–1 |

|------|--------------------------------------------------|-----|

| 2.2  | A User Process I/O Request                       | 2–3 |

| 2.3  | Device-Independent System I/O Preprocessing      | 2–3 |

| 2.4  | Device-Dependent I/O Preprocessing by the Driver | 2–3 |

| 2.5  | Queuing the I/O Request Packet to the Driver     | 2–4 |

| 2.6  | Activating the Printer                           | 2–5 |

| 2.7  | Waiting for a Device Interrupt                   | 2–5 |

| 2.8  | Handling Interrupts                              | 2–6 |

| 2.9  | I/O Postprocessing by the Driver                 | 2–6 |

| 2.10 | System I/O Postprocessing                        | 2–7 |

## 3 Synchronization of I/O Request Processing

| 3.1     | Interrupt Priority Levels                           | 3–1  |

|---------|-----------------------------------------------------|------|

| 3.1.1   | Interrupt Service Routines                          | 3–3  |

| 3.1.2   | IPL Use During I/O Processing                       | 3–3  |

| 3.1.2.1 | IPL 2 (IPL\$_ASTDEL)                                | 3–3  |

| 3.1.2.2 | IPL 4 (IPL\$_IOPOST)                                | 3–4  |

| 3.1.2.3 | IPL 8 to IPL 11 (Fork IPLs)                         | 3–5  |

| 3.1.2.4 | IPL 20 to IPL 23 (Device IPLs)                      | 3–5  |

| 3.1.2.5 | IPL 31 (IPL\$_POWER)                                | 3–6  |

| 3.1.3   | Additional IPLs                                     | 3–6  |

| 3.1.3.1 | IPL 3 (IPL\$_RESCHED)                               | 3–6  |

| 3.1.3.2 | IPL 6 (IPL\$_QUEUEAST)                              | 3–6  |

| 3.1.3.3 | IPL 7 (IPL\$_TIMERFORK)                             | 3–7  |

| 3.1.3.4 | IPL 8 (IPL\$_SYNCH)                                 | 3–7  |

| 3.1.3.5 | IPL 11 (IPL\$_MAILBOX)                              | 3–7  |

| 3.1.3.6 | IPL 14 (XDELTA Entry IPL)                           | 3–8  |

| 3.1.3.7 | IPL 22 or IPL 24 (Interval Clock IPLs)              | 3–8  |

| 3.1.4   | Modifying IPL in Driver Code                        | 3–8  |

| 3.1.4.1 | Raising IPL                                         | 3–9  |

| 3.1.4.2 | Lowering IPL                                        | 3–10 |

| 3.2     | Spinlocks                                           | 3–11 |

| 3.2.1   | Fork Locks                                          | 3–14 |

| 3.2.2   | Device Locks                                        | 3–15 |

| 3.3     | Device Driver Synchronization                       | 3–15 |

| 3.3.1   | Overview of the Synchronization of an I/O Operation | 3–15 |

| 3.3.2   | Synchronizing the Device Database                   | 3–19 |

| 3.3.3   | Synchronizing at Driver Fork Level                  | 3–20 |

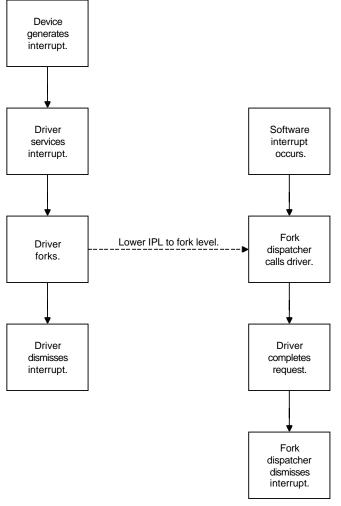

| 3.3.3.1 | Forking and the System Fork Dispatcher              | 3–21 |

| 3.3.3.2 | Restrictions on Fork Processes                      | 3–22 |

| 3.4     | Resource Wait Queues                                | 3–23 |

| 3.4.1   | Competing for a Controller's Data Channel           | 3–23 |

## 4 Overview of I/O Processing

| 4.1     | Preprocessing an I/O Request                 | 4–4 |

|---------|----------------------------------------------|-----|

| 4.1.1   | Process I/O Channel Assignment               | 4–5 |

| 4.1.2   | Locating a Device Driver in the I/O Database | 4–5 |

| 4.1.2.1 | Channel Request Block                        | 4–5 |

| 4.1.2.2 | Interrupt Dispatch Block                     | 4–7 |

| 4.1.2.3 | Device Data Block                            | 4–8 |

| 4.1.3   | Validating the I/O Function                  | 4–8 |

| 4.1.4 | Checking Process I/O Request Quotas              | 4–8  |

|-------|--------------------------------------------------|------|

| 4.1.5 | Validating the I/O Status Block                  | 4–8  |

| 4.1.6 | Allocating and Setting Up an I/O Request Packet  | 4–8  |

| 4.1.7 | FDT Processing                                   | 4–9  |

| 4.2   | Handling Device Activity                         | 4–12 |

| 4.2.1 | Creating a Driver Fork Process to Start I/O      | 4–13 |

| 4.2.2 | Activating a Device and Waiting for an Interrupt | 4–14 |

| 4.2.3 | Handling a Device Interrupt                      | 4–15 |

| 4.2.4 | Switching from Interrupt to Fork Process Context | 4–15 |

| 4.2.5 | Activating a Fork Process from a Fork Queue      | 4–16 |

| 4.3   | Completing an I/O Request                        | 4–16 |

| 4.3.1 | I/O Postprocessing                               | 4–17 |

|       |                                                  |      |

#### Part II Writing a Device Driver

## 5 Device Driver Coding Format

| 5.1 | Coding Conventions                                   | 5–1 |

|-----|------------------------------------------------------|-----|

| 5.2 | Restrictions on the Use of Device-Register I/O Space | 5–3 |

| 5.3 | Implementing Conditional Code in a Driver            | 5–4 |

## 6 Writing Device-Driver Tables

| 6.1   | Driver Prologue Table                   | 6–1 |

|-------|-----------------------------------------|-----|

| 6.2   | Driver Dispatch Table                   | 6–3 |

| 6.3   | Function Decision Table                 | 6–4 |

| 6.3.1 | Defining Buffered-I/O Functions         | 6–7 |

| 6.3.2 | Defining Device-Specific Function Codes | 6–8 |

#### 7 Writing FDT Routines

| 7.1                                   | Context of FDT Routine Execution            | 7–1                        |

|---------------------------------------|---------------------------------------------|----------------------------|

| 7.2                                   | FDT Routines and Their Exit Paths           | 7–2                        |

| 7.2.1                                 | FDT Exit Paths                              | 7–3                        |

| 7.2.1.1                               | RSB                                         | 7–3                        |

| 7.2.1.2                               | JMP G^EXE\$QIODRVPKT                        | 7–4                        |

| 7.2.1.3                               | JMP G^EXE\$FINISHIO or JMP G^EXE\$FINISHIOC | 7–4                        |

| 7.2.1.4                               | JMP G^EXE\$ABORTIO                          | 7–4                        |

| 7.2.1.5                               | JSB G^EXE\$ALTQUEPKT                        | 7–5                        |

| 7.3                                   |                                             | 7–5                        |

| 7.4                                   | FDT Routines for System Buffered I/O        | 7–5                        |

| 7.4.1                                 | Checking Accessibility of the User's Buffer | 7–6                        |

| 7.4.2                                 | Allocating the System Buffer                | 7–6                        |

| 7.4.3                                 | Buffered-I/O Postprocessing                 | 7–7                        |

| 7.5                                   | System-Provided FDT Routines                | 7–8                        |

| 7.3<br>7.4<br>7.4.1<br>7.4.2<br>7.4.3 | FDT Routines for System Direct I/O          | 7-<br>7-<br>7-<br>7-<br>7- |

#### 8 Writing a Start-I/O Routine

| 8.1   | Transferring Control to the Start-I/O Routine                    | 8–1 |

|-------|------------------------------------------------------------------|-----|

| 8.2   | Context of a Driver Fork Process                                 | 8–1 |

| 8.3   | Functions of a Start-I/O Routine                                 | 8–2 |

| 8.3.1 | Obtaining Controller Access                                      | 8–2 |

| 8.3.2 | Obtaining and Converting the I/O Function Code and Its Modifiers | 8–4 |

| 8.3.3 | Preparing the Device Activation Bit Mask                         | 8–4 |

| 8.3.4 | Synchronizing Access to the Device Database  | 8–4 |

|-------|----------------------------------------------|-----|

| 8.3.5 | Checking for a Local Processor Power Failure | 8–5 |

| 8.3.6 | Activating the Device                        | 8–5 |

| 8.4   | Waiting for an Interrupt or Timeout          | 8–5 |

| 8.4.1 | Expansion of WFIKPCH Macro                   | 8–6 |

| 8.4.2 | IOC\$WFIKPCH Routine                         | 8–6 |

#### 9 Writing an Interrupt Service Routine

| 9.1   | Interrupt Context                  | 9–3 |

|-------|------------------------------------|-----|

| 9.2   | Servicing a Solicited Interrupt    | 9–3 |

| 9.3   | Servicing an Unsolicited Interrupt | 9–4 |

| 9.3.1 | Examples of Unsolicited Interrupts | 9–6 |

#### **10** Completing an I/O Request and Handling Timeouts

| 10.1 I/O Postprocessing                                    | 10–1 |

|------------------------------------------------------------|------|

| 10.1.1 EXE\$IOFORK                                         | 10–1 |

| 10.1.2 Completing an I/O Request                           | 10–2 |

| 10.1.2.1 Releasing the Controller                          | 10–2 |

| 10.1.2.2 Saving Status, Count, and Device-Dependent Status | 10–3 |

| 10.1.2.3 Returning Control to the Operating System         | 10–3 |

| 10.2 Timeout Handling Routines                             | 10–4 |

| 10.2.1 Retrying an I/O Operation                           | 10–5 |

| 10.2.2 Aborting an I/O Request                             | 10–6 |

| 10.2.3 Sending a Message to the Operator                   | 10–6 |

#### **11 Other Driver Routines**

| 11.1   | Initialization Routines                             | 11–1  |

|--------|-----------------------------------------------------|-------|

| 11.1.1 | Controller Initialization Routine                   | 11–1  |

| 11.1.2 | Unit Initialization Routine                         | 11–2  |

| 11.1.3 | Initialization During Driver Loading                | 11–3  |

| 11.1.4 | Initialization During Recovery from a Power Failure | 11–4  |

| 11.1.5 | Forking from a Driver Initialization Routine        | 11–5  |

| 11.2   | Cancel-I/O Routine                                  | 11–6  |

| 11.2.1 | Context of a Cancel-I/O Routine                     | 11–7  |

| 11.2.2 | Drivers That Need No Cancel-I/O Routine             | 11–7  |

| 11.2.3 | Device-Independent Cancel-I/O Routine               | 11–7  |

| 11.2.4 | Device-Dependent Cancel-I/O Routine                 | 11–8  |

| 11.3   | Error-Logging Routines                              | 11–8  |

| 11.3.1 | System-Supplied Error-Logging Routines              | 11–9  |

| 11.3.2 | Register-Dumping Routine                            | 11–9  |

| 11.3.3 | Interpreting Error Log Entries                      | 11–10 |

| 11.4   | Cloned UCB Routine                                  | 11–10 |

## Part III Loading and Debugging a Driver

## 12 Loading a Device Driver

| 12.1   | Preparing a Driver for Loading into the Operating System | 12–1  |

|--------|----------------------------------------------------------|-------|

| 12.2   | Loading a Driver                                         | 12–2  |

| 12.2.1 | LOAD Command                                             | 12–3  |

| 12.2.2 | CONNECT Command                                          | 12–3  |

| 12.2.3 | RELOAD Command                                           | 12–7  |

| 12.2.4 | SHOW/ADAPTER Command                                     | 12–8  |

| 12.2.5 | SHOW/BI Command                                          | 12–9  |

| 12.2.6 | SHOW/BUS Command                                         | 12–9  |

| 12.2.7 | SHOW/XMI Command                                         | 12–10 |

| 12.2.8 | SHOW/CONFIGURATION Command                               | 12–11 |

| 12.2.9 | SHOW/DEVICE Command                                      | 12–11 |

| 12.3   | Loading Uniprocessing and Multiprocessing Drivers        | 12–12 |

| 12.4   | SYSGEN Autoconfiguration Facility                        | 12–13 |

| 12.4.1 | SYSGEN Device Table                                      | 12–13 |

| 12.4.2 | Device Driver Control of Autoconfiguration               | 12–19 |

| 12.4.3 | Floating-Vector Address Calculation                      | 12–20 |

| 12.4.4 | Floating-CSR Address Calculation                         | 12–20 |

| 12.4.5 | Rules for Configuration                                  | 12–20 |

## 13 Debugging a Device Driver

| 13.1 E    | Bootstrapping the System with XDELTA                   | 13–1  |

|-----------|--------------------------------------------------------|-------|

| 13.2 F    | Proceeding from the Initial Breakpoints                | 13–5  |

| 13.3 I    | Loading the Driver                                     | 13–6  |

| 13.4 I    | nserting Breakpoints in Driver Source Code             | 13–6  |

| 13.5 (    | Calculating the Base of Driver Code                    | 13–7  |

| 13.6 F    | Requesting an XDELTA Software Interrupt                | 13–7  |

| 13.7 E    | Examining the Vector-Jump Table                        | 13–9  |

| 13.8 \$   | Setting an XDELTA Base Register                        | 13–9  |

| 13.9 H    | Examining the UCB, IRP, or PSL                         | 13–10 |

| 13.10 X   | XDELTA Commands                                        | 13–10 |

| 13.10.1   | Values and Expressions                                 | 13–12 |

| 13.10.2   | Special Symbols                                        | 13–12 |

| 13.10.2.1 |                                                        | 13–13 |

| 13.10.2.2 |                                                        | 13–13 |

| 13.10.2.3 |                                                        | 13–13 |

| 13.10.3   | Display Names and Locations of Loaded Executive Images | 13–14 |

| 13.10.4   | Set Display Mode                                       | 13–14 |

| 13.10.5   | Open, Examine, and Close Location                      | 13–15 |

| 13.10.5.1 | - F                                                    | 13–15 |

| 13.10.5.2 |                                                        | 13–15 |

| 13.10.5.3 | 1 5                                                    | 13–16 |

| 13.10.5.4 | 1 5 0                                                  | 13–16 |

| 13.10.5.5 |                                                        | 13–16 |

| 13.10.5.6 | Display Previous Location Command                      | 13–16 |

| 13.10.6   | Breakpoints                                            | 13–17 |

| 13.10.6.1 | Setting Breakpoints                                    | 13–17 |

| 13.10.6.2 | 2 Clearing Breakpoints                                 | 13–17 |

| 13.10.6.3 | B Displaying Breakpoint List                           | 13–17 |

| 13.10.6.4 | Proceeding from Breakpoints                            | 13–18 |

| 13.10.6.5 |                                                        | 13–18 |

|           |                                                        |       |

| 13.10.7   | Step, Set Location, and Execute Instruction Commands | 13–18 |

|-----------|------------------------------------------------------|-------|

| 13.10.7.1 | Loading PC and Continuing                            | 13–18 |

| 13.10.7.2 | Execute Instruction and Step Command                 | 13–18 |

| 13.10.7.3 | Step Instruction over Subroutine Command             | 13–18 |

| 13.10.8   | Execute String Command                               | 13–19 |

| 13.10.8.1 | Locating Nonpaged System Patch Space                 | 13–19 |

| 13.11 Gu  | idelines for Debugging Device Drivers                | 13–20 |

| 13.11.1   | Opening Device Registers in XDELTA                   | 13–20 |

| 13.11.2   | Adjusting the Device Timeout Value                   | 13–21 |

| 13.11.3   | XDELTA and System Failures                           | 13–21 |

| 13.12 Co  | mmon Driver Errors                                   | 13–21 |

| 13.12.1   | References to System Addresses                       | 13–21 |

| 13.12.2   | Incorrect References to Device Registers             | 13–21 |

| 13.12.3   | Destroying Register Contents                         | 13–22 |

| 13.13 Po  | ol Checking Mechanism                                | 13–22 |

| 13.14 De  | tecting Driver Problems in a Multiprocessing System  | 13–26 |

## Part IV Bus Specifics and Advanced Topics

## 14 UNIBUS and Q22–bus Device Support

| 14.1 Fu  | nctions of the UNIBUS Adapter and Q22–bus Interface         | 14–1  |

|----------|-------------------------------------------------------------|-------|

| 14.1.1   | Reading and Writing Device Registers                        | 14–3  |

| 14.1.2   | Map Registers                                               | 14–3  |

| 14.1.3   | UNIBUS Adapter Data Transfer Paths                          | 14–7  |

| 14.1.3.1 | Direct Data Path                                            | 14–9  |

| 14.1.3.2 | Buffered Data Paths                                         | 14–10 |

| 14.1.3.3 | Byte-Offset Data Transfers                                  | 14–12 |

| 14.1.3.4 | Purging a Buffered Data Path                                | 14–12 |

| 14.1.3.5 | Longword-Aligned, 32-Bit, Random-Access Mode                | 14–13 |

| 14.2 Wr  | iting Driver Code for UNIBUS/Q22-bus DMA Transfers          | 14–13 |

| 14.2.1   | Selecting and Requesting a Data Path                        | 14–15 |

| 14.2.1.1 | Requesting a Buffered Data Path                             | 14–15 |

| 14.2.1.2 | Requesting a Permanent Buffered Data Path                   | 14–16 |

| 14.2.1.3 | Requesting the Direct Data Path                             | 14–16 |

| 14.2.1.4 | Mixed Use of Direct and Buffered Data Paths                 | 14–17 |

| 14.2.2   | Requesting Map Registers                                    | 14–17 |

| 14.2.2.1 | Allocating Map Registers                                    | 14–17 |

| 14.2.2.2 | Permanently Allocating Map Registers                        | 14–18 |

| 14.2.3   | Loading Map Registers                                       | 14–19 |

| 14.2.4   | Computing the Starting Address of a Transfer                | 14–20 |

| 14.2.5   | Computing the Transfer Length                               | 14–21 |

| 14.2.6   | Activating the Device                                       | 14–21 |

| 14.2.7   | Completing a DMA Transfer                                   | 14–21 |

| 14.2.7.1 | Purging the Data Path                                       | 14–22 |

| 14.2.7.2 | Releasing a Buffered Data Path                              | 14–22 |

| 14.2.7.3 | Releasing Map Registers                                     | 14–23 |

| 14.3 Int | errupt Dispatching in a UNIBUS/Q22-bus System               | 14–24 |

| 14.3.1   | Direct-Vector and Non-Direct-Vector Interrupt Dispatching   | 14–27 |

| 14.3.2   | Adapter Dispatch Table                                      | 14–28 |

| 14.3.3   | Interrupt Transfer Vector and Interrupt Transfer Routine    | 14–28 |

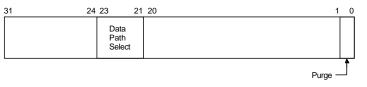

| 14.3.4   | Multilevel Device Interrupt Dispatching for Q22-bus Devices | 14–31 |

| 14.3.4.1 | Ensuring That the Q22-bus Is Properly Configured            | 14–32 |

| 14.3.4.2 | Effects of Enabling Multilevel Device Interrupt Dispatching | 14–33 |

## 15 MASSBUS Device Support

| 15.1     | MASSBUS Adapter Registers                             | 15–1  |

|----------|-------------------------------------------------------|-------|

| 15.1.1   | Loading MASSBUS Adapter Registers                     | 15–3  |

| 15.1.2   | MASSBUS Adapter Registers and Offsets                 | 15–4  |

| 15.1.3   | Modifying MASSBUS Adapter Registers                   | 15–5  |

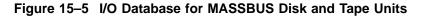

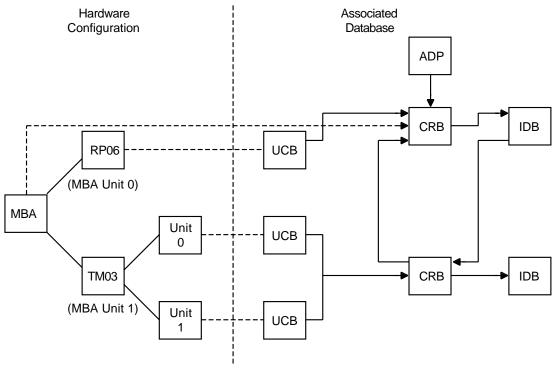

| 15.2     | I/O Database for MASSBUS Devices                      | 15–6  |

| 15.3     | MASSBUS Adapter Operations                            | 15–8  |

| 15.4     | MASSBUS Adapter's Interrupt Dispatching               | 15–9  |

| 15.4.1   | Checking for MASSBUS Adapter Ownership                | 15–9  |

| 15.4.2   | Dispatching a Device Interrupt                        | 15–10 |

| 15.5     | Special Considerations for MASSBUS Device Drivers     | 15–10 |

| 15.5.1   | Unit Initialization Routine                           | 15–10 |

| 15.5.2   | The MASSBUS Adapter and the I/O Database              | 15–11 |

| 15.5.3   | Start-I/O Routine                                     | 15–11 |

| 15.5.3.  | 1 Requesting Controller Data Channels                 | 15–12 |

| 15.5.3.2 | 2 Loading Map Registers                               | 15–12 |

| 15.5.3.3 |                                                       | 15–13 |

| 15.5.4   | DPTAB Macro                                           | 15–13 |

| 15.6     | Interrupt Service Routines for MASSBUS Devices        | 15–13 |

| 15.6.1   | Transferring Control to the Interrupt Service Routine | 15–13 |

| 15.6.2   | Returning Control to MBA\$INT                         | 15–14 |

| 15.6.3   | Considerations for Interrupt Service Routines         | 15–14 |

|          |                                                       |       |

## 16 Generic VAXBI Device Support

| 16.1 Overview of VAXBI Driver Support                                    | 16–1  |

|--------------------------------------------------------------------------|-------|

| 16.2 VAXBI Concepts                                                      | 16–1  |

| 16.2.1 VAXBI Address Space                                               | 16–2  |

| 16.2.2 Backplane Interconnect Interface Chip (BIIC)                      | 16–5  |

| 16.3 XBI+ Adapter                                                        | 16–5  |

| 16.3.1 XBI+ BI-to-XMI Address Translation                                | 16–6  |

| 16.3.2 VAXBI Device Register Access                                      | 16–6  |

| 16.4 SCU/XMI Concepts                                                    | 16–6  |

| 16.5 VAX 7000 Series and VAX 10000 Series Systems                        | 16–7  |

| 16.5.1 Data Structures                                                   | 16–8  |

| 16.5.2 System Macros                                                     | 16–8  |

| 16.5.3 Processing                                                        | 16–9  |

| 16.6 Initialization Performed by the System                              | 16–10 |

| 16.6.1 Data Structures                                                   | 16–11 |

| 16.6.2 System Control Block                                              | 16–12 |

| 16.7 Initialization Performed by the VAXBI Device Driver                 | 16–13 |

| 16.7.1 Examining BIIC Self-Test Status                                   | 16–15 |

| 16.7.2 Clearing BIIC Errors, Setting Interrupts, and Enabling Interrupts | 16–16 |

| 16.7.2.1 Clearing the Bus Error Register                                 | 16–16 |

| 16.7.2.2 Loading the Interrupt Destination Register                      | 16–16 |

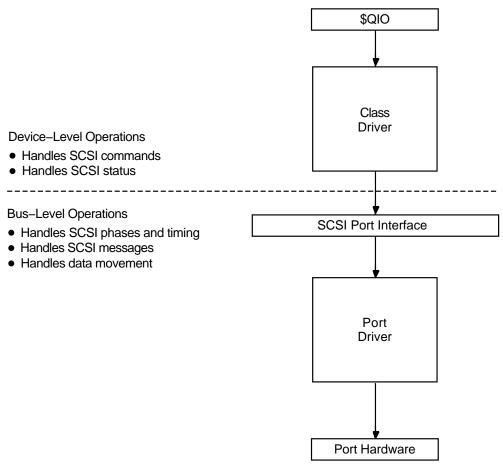

| 16.7.2.3 Setting Interrupt Vectors                                       | 16–16 |

| 16.7.2.4 Enabling Error Interrupts                                       | 16–17 |

| 16.7.2.5 Enabling BIIC Options                                           | 16–17 |

| 16.7.3 Mapping Window Space                                              | 16–17 |

| 16.8 DMA Transfers                                                       | 16–19 |

| 16.8.1 Example: DMB32 Asynchronous/Synchronous Multiplexer               | 16–21 |

| 16.9 Unit Initialization Routine                                         | 16–23 |

| 16.10 Register-Dumping Routine                                           | 16–23 |

| 16.11 Loading a VAXBI Device Driver                                      | 16–23 |

|    | 16.12   | BIIC Register Definitions                                          | 16–23 |

|----|---------|--------------------------------------------------------------------|-------|

| 17 | SCSI    | Class Driver Support                                               |       |

|    | 17.1    | VAX Systems with SCSI Bus Concepts                                 | 17–2  |

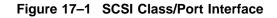

|    | 17.2    | SCSI Class/Port Architecture                                       | 17–2  |

|    | 17.2.1  | SCSI Port Interface                                                | 17–5  |

|    | 17.2.2  | SCSI-Specific Data Structures                                      | 17-6  |

|    | 17.2.2  | SCSI Class Driver Template                                         | 17-8  |

|    | 17.2.3  | -                                                                  | 17-0  |

|    | 17.3    | Connecting to a SCSI Device<br>Setting Up a SCSI Command           | 17-9  |

|    | 17.4.1  |                                                                    | 17–9  |

|    | 17.4.1  | Preparing a SCSI Command Descriptor Block                          | 17–10 |

|    | 17.4.2  | Setting Command Timeouts                                           | 17–11 |

|    |         | Disabling Command Retry                                            | 17–11 |

|    | 17.5    | Performing a SCSI Data Transfer                                    | 17-12 |

|    | 17.5.1  | Setting the Data Transfer Mode                                     |       |

|    | 17.5.2  | Enabling Disconnection and Reselection                             | 17–12 |

|    | 17.5.3  | Determining the Maximum Data Transfer Size                         | 17–13 |

|    | 17.5.4  | Initializing the SCDRP to Reflect Class Driver Data Buffering      | 47 40 |

|    |         | Mechanisms                                                         | 17–13 |

|    | 17.5.5  | Making a Class Driver Data Buffer Accessible to the Port           | 17–14 |

|    | 17.5.6  | Examining Port and SCSI Status.                                    | 17–15 |

|    | 17.5.6. | 0                                                                  | 17–16 |

|    | 17.5.6. |                                                                    | 17–16 |

|    | 17.5.6. | 0 1                                                                | 17–17 |

|    | 17.6    | Other SCSI Class Driver Issues                                     | 17–17 |

|    | 17.6.1  | Preserving Local Context                                           | 17–17 |

|    | 17.6.2  | Error Logging                                                      | 17–18 |

|    | 17.7    | Flow of a Read I/O Request Through the SCSI Class and Port Drivers | 17–20 |

|    | 17.8    | Components of a SCSI Class Driver                                  | 17–22 |

|    | 17.8.1  | Data Definitions                                                   | 17–22 |

|    | 17.8.2  | Driver Prologue Table                                              | 17–23 |

|    | 17.8.3  | Driver Dispatch Table                                              | 17–23 |

|    | 17.8.4  | Function Decision Table and FDT Routines                           | 17–23 |

|    | 17.8.5  | Controller Initialization Routine                                  | 17–23 |

|    | 17.8.6  | Unit Initialization Routine                                        | 17–23 |

|    | 17.8.7  | Start-I/O Routine                                                  | 17–24 |

|    | 17.8.8  | Cancel-I/O Routine                                                 | 17–25 |

|    | 17.8.9  | Register-Dumping Routine                                           | 17–26 |

|    | 17.9    | Servicing Asynchronous Events from a SCSI Device                   | 17–26 |

|    | 17.10   | Tagged Command Queuing I/O for SCSI-2 Devices                      | 17–27 |

|    | 17.10.1 | SCSI-2 Driver Design Considerations                                | 17–28 |

|    | 17.10.2 | -                                                                  | 17–30 |

|    | 17.10.3 | Mixing Queued and Non-Queued I/O Requests                          | 17–30 |

|    | 17.10.4 |                                                                    | 17–31 |

|    | 17.10.5 |                                                                    | 17–32 |

|    | 17.10.6 |                                                                    | 17–32 |

|    | 17.10.7 |                                                                    | 17–33 |

|    | 17.11   | Configuring a SCSI Third-Party Device                              | 17–34 |

|    | 17.11.1 |                                                                    | 17–34 |

|    | 17.12   | Debugging a SCSI Class Driver                                      | 17–35 |

|    | 17.12.1 |                                                                    | 17–36 |

|    |         |                                                                    |       |

| 17.12.2   | Interpreting SCSI Error Log Entries                 | 17–36 |

|-----------|-----------------------------------------------------|-------|

| 17.12.2.1 | SCSI Port Driver Error Log Entries                  | 17–36 |

| 17.12.2.2 | SCSI Class Driver Error Log Entries                 | 17–41 |

| 17.13 Re  | solving SCSI Class Driver Problems Using Error Logs | 17–42 |

#### **18 Terminal Class and Port Drivers**

| 18.1 Ove  | erview                            | 18–2  |

|-----------|-----------------------------------|-------|

| 18.2 Dat  | a Structures                      | 18–2  |

| 18.2.1    | Terminal UCB                      | 18–2  |

| 18.2.2    | Port Driver Vector Table          | 18–3  |

|           | Class Driver Vector Table         | 18–4  |

|           | Vector Table Generation Macros    | 18–5  |

| 18.2.4.1  | \$VECINI Macro                    | 18–5  |

| 18.2.4.2  | \$VEC Macro                       | 18–6  |

| 18.2.4.3  | \$VECEND Macro                    | 18–6  |

| 18.3 Stru | ucture of Port and Class Drivers  | 18–6  |

| 18.3.1    | Binding Class and Port Drivers    | 18–6  |

|           | t Driver Routines                 | 18–9  |

|           | Port Startup Routines             | 18–10 |

| 18.4.1.1  | Controller Initialization Routine | 18–10 |

| 18.4.1.2  | Unit Initialization Routine       | 18–11 |

| 18.4.2    | Port Initiate Routines            | 18–11 |

| 18.4.2.1  | PORT_DISCONNECT                   | 18–11 |

| 18.4.2.2  | PORT_DS_SET                       | 18–12 |

| 18.4.2.3  | PORT_FDT                          | 18–12 |

| 18.4.2.4  | PORT_FORKRET                      | 18–13 |

| 18.4.2.5  | PORT_MAINT                        | 18–13 |

| 18.4.2.6  | PORT_SET_LINE                     | 18–13 |

| 18.4.2.7  | PORT_SET_MODEM                    | 18–13 |

| 18.4.2.8  | PORT_STARTIO                      | 18–14 |

| 18.4.3    | Port Service Routines             | 18–14 |

| 18.4.3.1  | PORT_ABORT                        | 18–14 |

| 18.4.3.2  | PORT_CANCEL                       | 18–15 |

| 18.4.3.3  | PORT_RESUME                       | 18–15 |

| 18.4.3.4  | PORT_STOP                         | 18–15 |

| 18.4.3.5  | PORT_XOFF                         | 18–15 |

| 18.4.3.6  | PORT_XON                          | 18–16 |

| 18.4.3.7  | Port Interrupt Service Routines   | 18–16 |

|           | ss Driver Routines                | 18–17 |

|           | CLASS_DDT                         | 18–17 |

|           | CLASS_DISCONNECT                  | 18–17 |

|           | CLASS_DS_TRANS                    | 18–17 |

|           | CLASS_FORK                        | 18–18 |

|           | CLASS GETNXT                      | 18–18 |

|           | CLASS_PUTNXT                      | 18-19 |

|           | CLASS_SETUP_UCB                   | 18-19 |

|           | CLASS_POWERFAIL                   | 18-20 |

|           | CLASS_READERROR                   | 18-20 |

|           |                                   | 10 20 |

#### **19 TURBOchannel Device Driver Support**

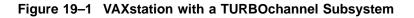

| 19.1   | Hardware Environment                         | 19–1 |

|--------|----------------------------------------------|------|

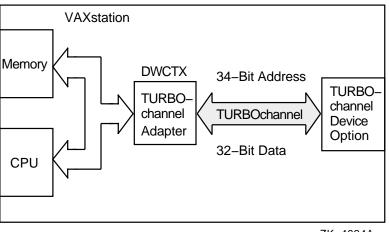

| 19.1.1 | Address Maps                                 | 19–2 |

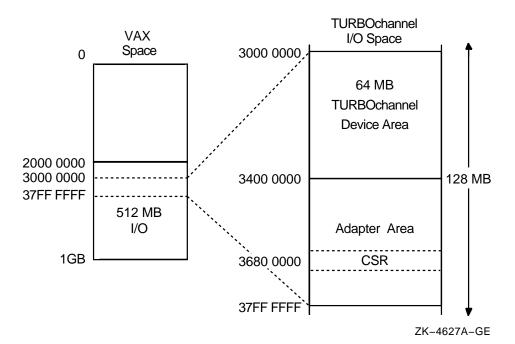

| 19.2   | DMA Transactions                             | 19–3 |

| 19.2.1 | Mapped DMA                                   | 19–3 |

| 19.2.2 | Unmapped DMA                                 | 19–4 |

| 19.3   | Using TURBOchannel Mapped DMA Routines       | 19–4 |

| 19.4   | Coding a TURBOchannel Device Driver          | 19–5 |

| 19.5   | Assembling and Linking a TURBOchannel Driver | 19–5 |

| 19.6   | Loading a TURBOchannel Device Driver         | 19–6 |

#### 20 VMEbus Device Driver Support

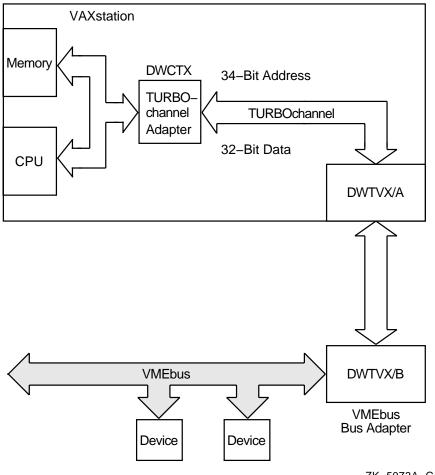

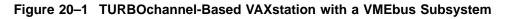

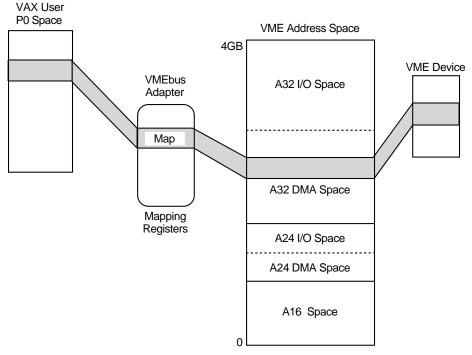

| 20.1   | Hardware Environment                         | 20–1  |

|--------|----------------------------------------------|-------|

| 20.2   | VMEbus Protocol Parameters                   | 20–3  |

| 20.3   | Considering Byte Order Transfer Differences  | 20–3  |

| 20.4   | Handling Interrupts                          | 20–4  |

| 20.5   | DMA Operations                               | 20–5  |

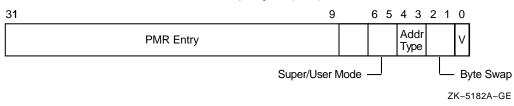

| 20.6   | Programmed I/O Operations and I/O Mapping    | 20–7  |

| 20.7   | VAX 7000 Series and VAX 10000 Series Systems | 20–9  |

| 20.7.1 | Data Structures                              | 20–9  |

| 20.7.2 | System Macros                                | 20–10 |

| 20.7.3 | Processing                                   | 20–10 |

| 20.8   | Coding a VMEbus Device Driver                | 20–11 |

| 20.8.1 | Porting UNIX Based Drivers                   | 20–11 |

| 20.9   | Assembling and Linking a VMEbus Driver       | 20–12 |

| 20.10  | Loading a VME Device Driver                  | 20–13 |

#### 21 Mapping to I/O Space and the Connect-to-Interrupt Facility

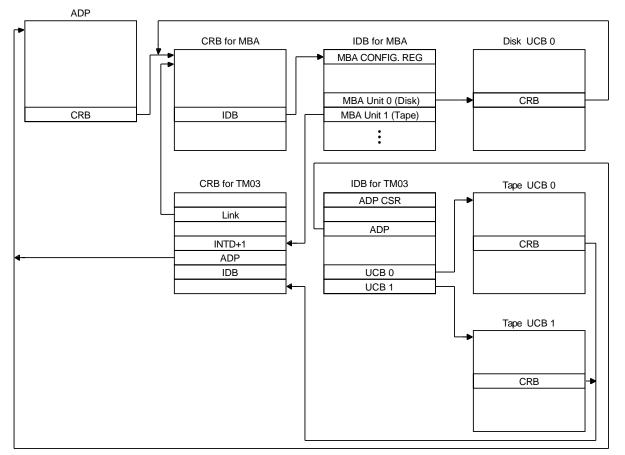

| 21.1     | I/O Address Space                                        | 21–1  |

|----------|----------------------------------------------------------|-------|

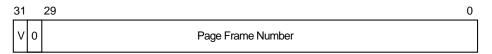

| 21.2     | PFN Mapping                                              | 21–5  |

| 21.2.1   | Notes on PFN Mapping                                     | 21–6  |

| 21.3     | Connecting to an Interrupt Vector                        | 21–7  |

| 21.3.1   | Performing the Connect-to-Interrupt                      | 21–8  |

| 21.3.2   | \$QIO Connect-to-Interrupt Request to Driver             | 21–9  |

| 21.3.3   | Connect-to-Interrupt Driver (CONINTERR.EXE)              | 21–12 |

| 21.3.4   | Process-Specified Routines                               | 21–12 |

| 21.3.4.  |                                                          | 21–13 |

| 21.3.4.2 | 2 Start-I/O Routine                                      | 21–14 |

| 21.3.4.3 | 3 Interrupt Service Routine                              | 21–15 |

| 21.3.4.4 | 4 Cancel-I/O Routine                                     | 21–16 |

| 21.3.5   | AST Procedure                                            | 21–17 |

| 21.4     | Real-Time Applications Examples                          | 21–17 |

| 21.4.1   | Example 1: KW11–W Watchdog Timer                         | 21–18 |

| 21.4.2   | Example 2: AD11-K, AM11-K A/D Converter with Multiplexer |       |

|          | Connected to the UNIBUS                                  | 21–19 |

| 21.4.3   | Example 3: KW11–P Real-Time Clock and AD11–K Converter   |       |

|          | Connected to the UNIBUS                                  | 21–21 |

|          |                                                          |       |

Part V Driver Templates and Examples

- A Driver Template

- **B** SCSI Class Driver Template

- C Sample Driver for the RL11, RL01, and RL02 Disk Drives

- D Sample Driver for the DR11–W and DRV11–WA Interfaces

- E Sample Driver for a TURBOchannel Device

- **F** Sample Driver for a VMEbus DR11–W Interface

#### G Multiprocessing Requirements on Kernel-Mode Code

| G.1     | Uniprocessor and Multiprocessor Device Drivers                 | G–1  |

|---------|----------------------------------------------------------------|------|

| G.1.1   | MULTIPROCESSING System Parameter                               | G–2  |

| G.1.2   | Device Driver Loading                                          | G–3  |

| G.1.3   | System Synchronization Macros                                  | G–4  |

| G.2     | Changes Required to Drivers Written Before VMS Version 5.0     | G–4  |

| G.2.1   | Address of the Driver's Interrupt Service Routine in the DPT   | G–5  |

| G.2.2   | Checking, Debiting, and Crediting a Process's Byte Count Quota | G–5  |

| G.2.3   | Referring to the Current PCB                                   | G–6  |

| G.2.4   | Allocating System Page-Table Entries                           | G–6  |

| G.2.5   | Referring to a System Process Mailbox                          | G–7  |

| G.2.6   | Reassembling and Relinking the Driver                          | G–7  |

| G.3     | Adapting Device Drivers to Run on a Multiprocessing System     | G–8  |

| G.3.1   | Specifying the Fork Lock Index                                 | G–8  |

| G.3.2   | Synchronizing Access to the Device Database with the Interrupt |      |

|         | Service Routine                                                | G–8  |

| G.3.2.1 | Synchronizing at Device IPL                                    | G–9  |

| G.3.2.2 | Raising IPL to IPL\$_POWER                                     | G–9  |

| G.3.2.3 | Synchronization Within the Interrupt Service Routine           | G–10 |

| G.3.3   | Controller and Unit Initialization Routines                    | G–11 |

| G.3.3.1 | Permanently Allocating Map Registers and Buffered Data         |      |

|         | Paths                                                          | G–11 |

| G.3.4   | Timeout Handling Routine                                       | G–11 |

| G.3.5   | General Methods for Synchronizing Kernel-Mode Code             | G–12 |

| G.3.5.1 |                                                                | G–12 |

| G.3.5.2 | 8                                                              | G–13 |

| G.3.6   | Miscellaneous Conversion Tasks                                 | G–14 |

| G.3.6.1 |                                                                | G–14 |

| G.3.6.2 | Calling the Driver Fork Process from a TQE                     | G–14 |

| G.3.6.3 | 0                                                              | G–14 |

| G.3.6.4 |                                                                | G–15 |

| G.3.6.5 | Poor Man's Lockdown                                            | G–15 |

| G.3.7     | Troubleshooting a Device Driver in a Multiprocessing System | G–16 |

|-----------|-------------------------------------------------------------|------|

| G.3.7.1   | Multiprocessing Bugchecks                                   | G–17 |

| G.3.7.2   | Analyzing a Multiprocessing System Failure                  | G–17 |

| G.3.7.2.1 | Investigating the Status of Spinlocks                       | G–18 |

| G.3.7.3   | Using XDELTA on SMP Systems                                 | G–19 |

## Glossary

#### Index

## Examples

| 9–1  | Example of an Unsolicited Interrupt                         | 9–6   |

|------|-------------------------------------------------------------|-------|

| 13–1 | Loading a Driver                                            | 13–6  |

| 17–1 | SCSI Bus Phase Error Port Driver Error Log Entry            | 17–43 |

| 17–2 | SCSI Bus Reset Port Driver Error Log Entry                  | 17–44 |

| 17–3 | SCSI Bus Reset Class Driver Error Log Entry                 | 17–45 |

| 19–1 | Using the SHOW/ADAPTER Command                              | 19–6  |

| 19–2 | Using the SHOW/TURBOCHANNEL Command                         | 19–6  |

| 19–3 | Loading a Driver with the CONNECT Command                   | 19–6  |

| 20–1 | Using the SHOW/ADAPTER Command (VAX 6000 Series System)     | 20–14 |

| 20–2 | Using the SHOW/ADAPTER Command (VAX 7000 Series System)     | 20–14 |

| 20–3 | Using the SHOW/BUS Command (VAX 6000 Series System)         | 20–14 |

| 20–4 | Using the SHOW/BUS Command (VAX 7000 Series System)         | 20–15 |

| 20–5 | Loading a Driver with the CONNECT Command                   | 20–15 |

| 21–1 | Locating the Adapter Address Space of a UNIBUS Adapter on a |       |

|      | VAXBI Bus                                                   | 21–4  |

## Figures

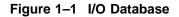

| 1–1  | I/O Database                                             | 1–5  |

|------|----------------------------------------------------------|------|

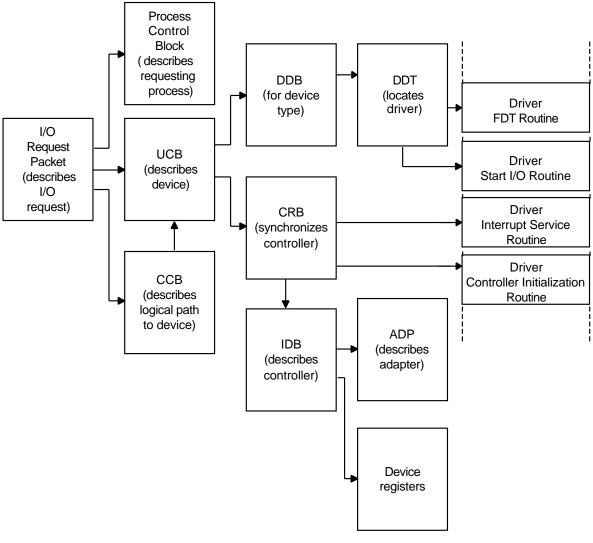

| 1–2  | Physical Address Space for VAXBI Based Processors        | 1–11 |

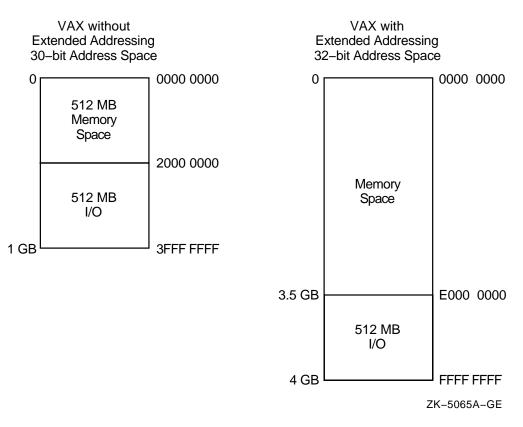

| 1–3  | Virtual Address Space for VAXes                          | 1–12 |

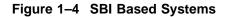

| 1–4  | SBI Based Systems                                        | 1–13 |

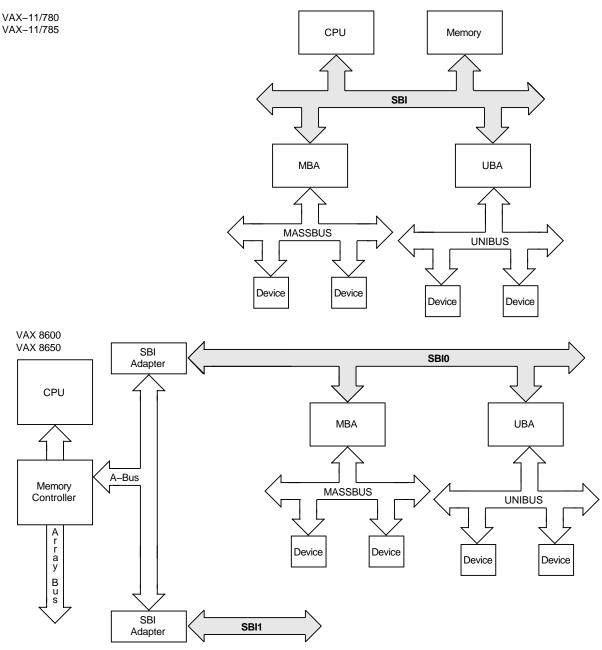

| 1–5  | VAXBI Based Systems                                      | 1–15 |

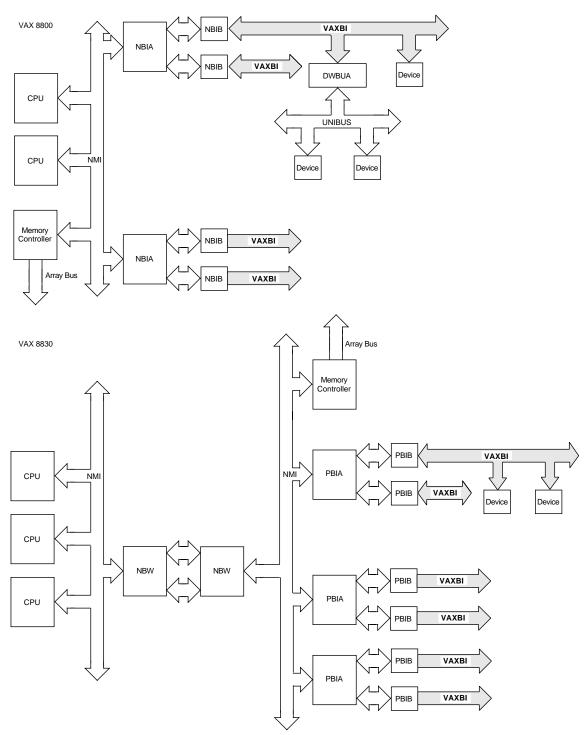

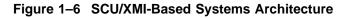

| 1–6  | SCU/XMI-Based Systems Architecture                       | 1–18 |

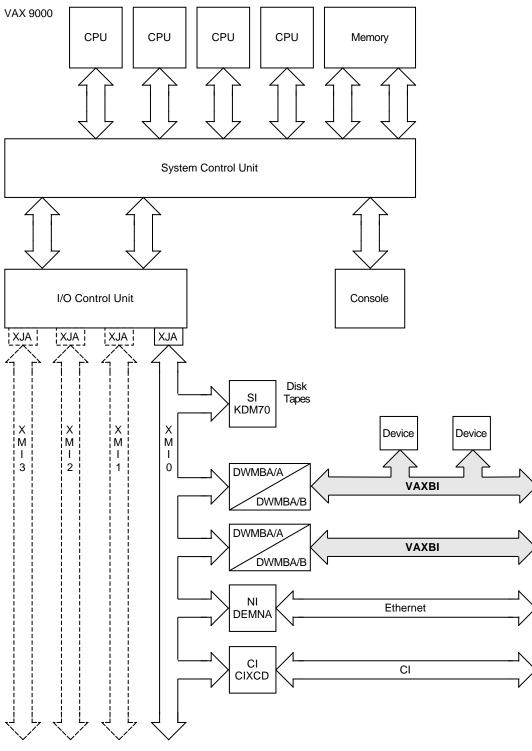

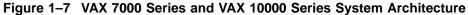

| 1–7  | VAX 7000 Series and VAX 10000 Series System Architecture | 1–20 |

| 1–8  | Q22-bus Based Systems                                    | 1–21 |

| 1–9  | MicroVAX/VAXstation 3100 System Architecture             | 1–22 |

| 1–10 | VAXstation 3520/3540 System Architecture                 | 1–23 |

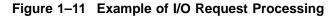

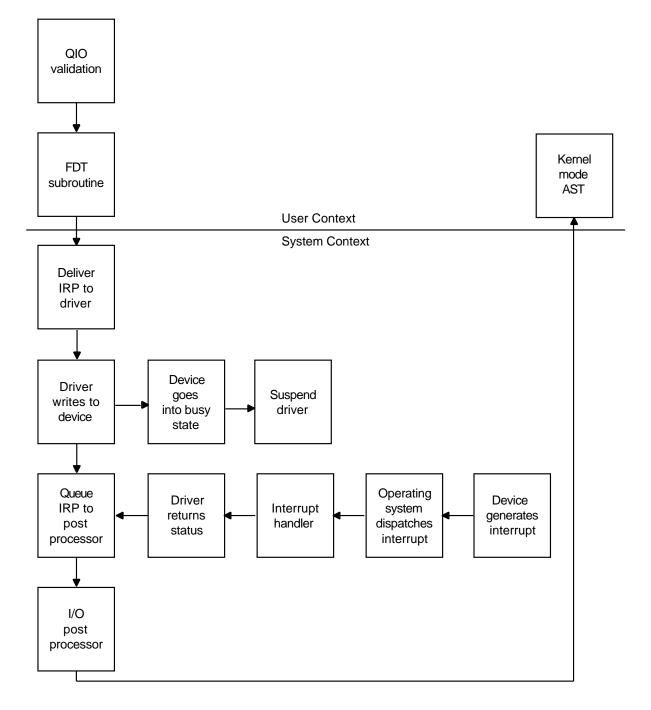

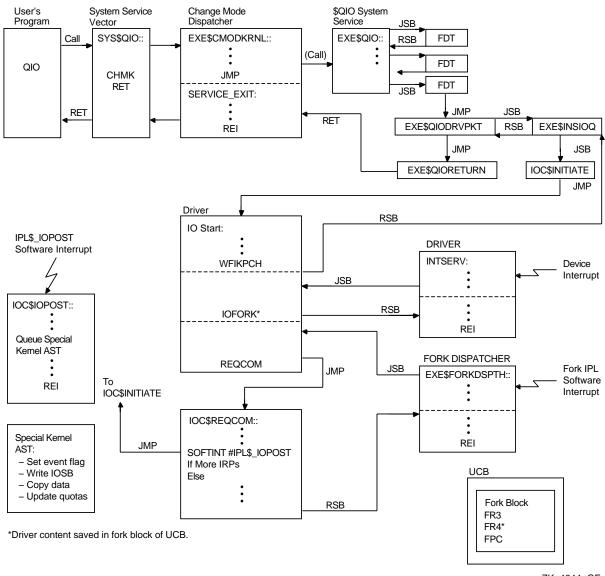

| 1–11 | Example of I/O Request Processing                        | 1–26 |

| 2–1  | A Printer Write Function                                 | 2–2  |

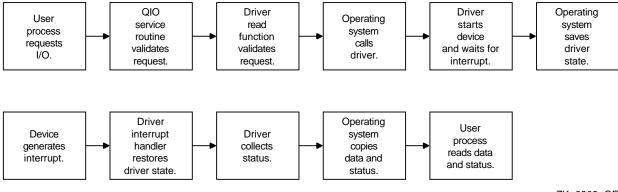

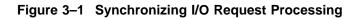

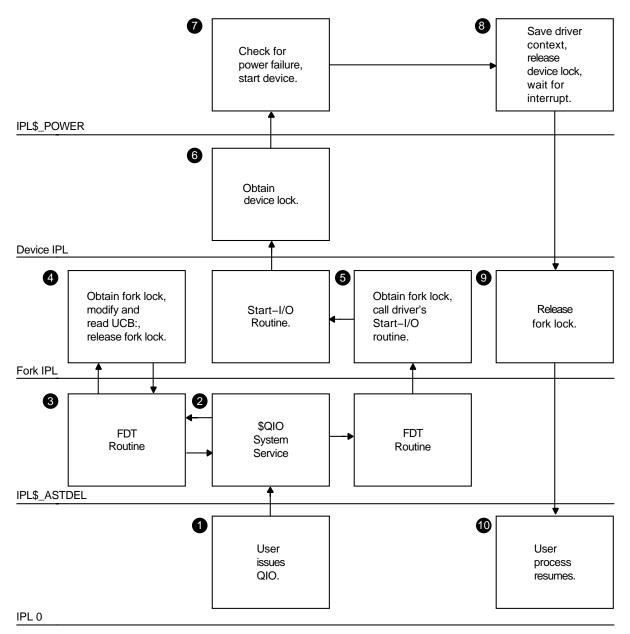

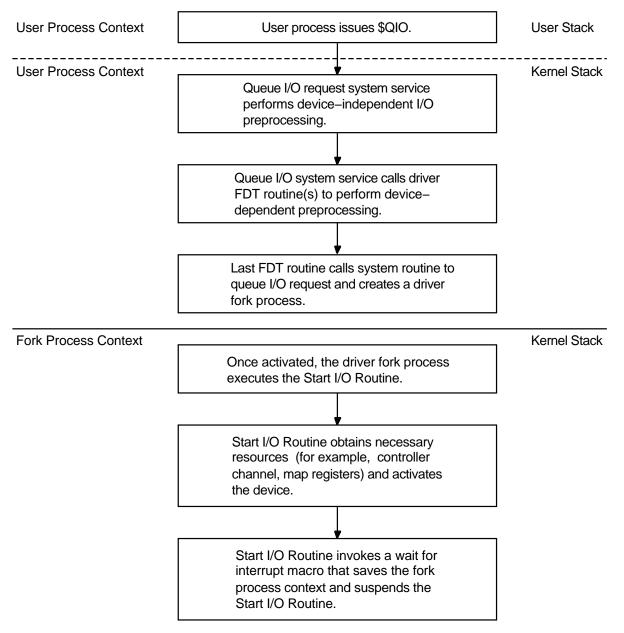

| 3–1  | Synchronizing I/O Request Processing                     | 3–16 |

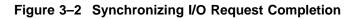

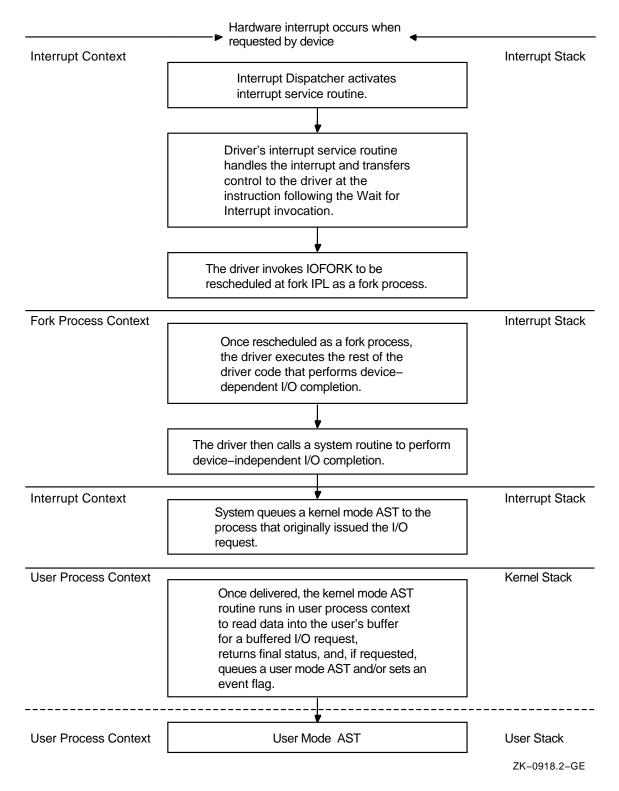

| 3–2  | Synchronizing I/O Request Completion                     | 3–18 |

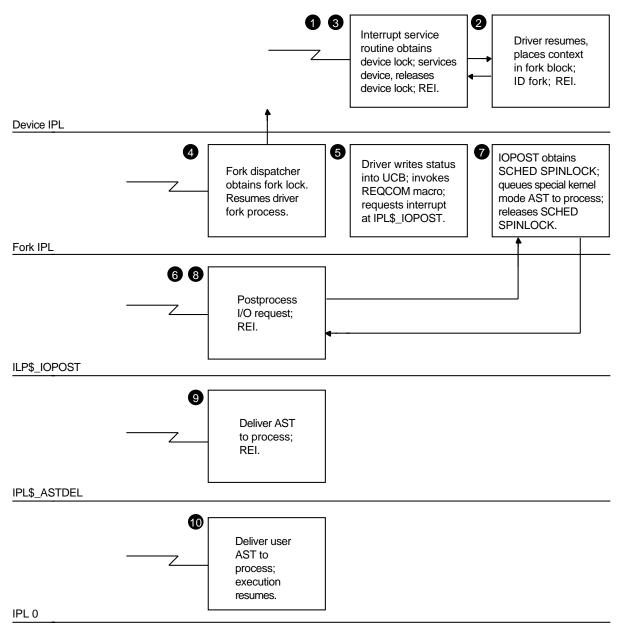

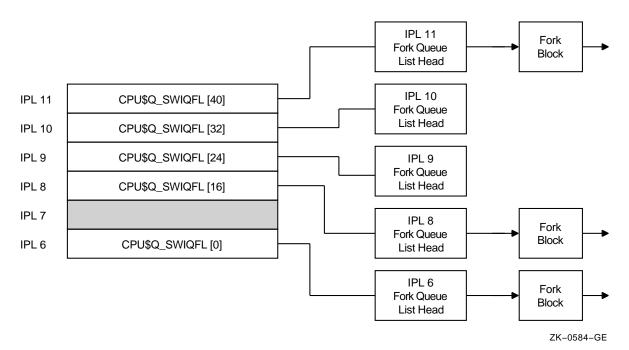

| 3–3  | Processor-Specific Fork Queue Structure                  | 3–22 |

| 4–1  | Sequence of Driver Execution                             | 4–2  |

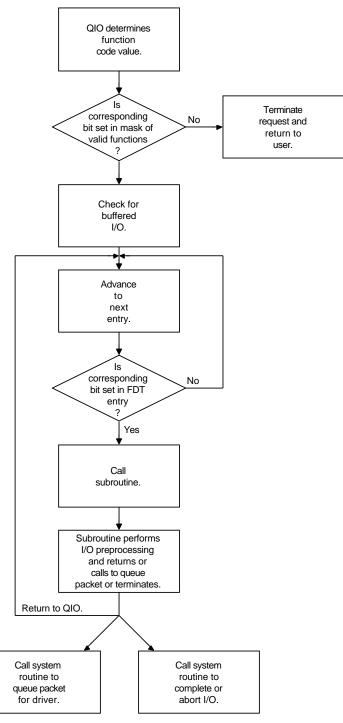

| 4–2  | Detailed Sequence of System I/O Processing               | 4–4  |

|      |                                                          |      |

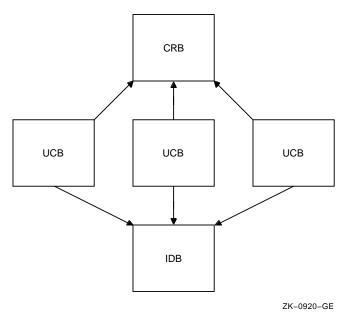

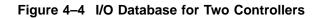

| 4–3          | Data Structures for Three Devices on One Controller                            | 4–6   |

|--------------|--------------------------------------------------------------------------------|-------|

| 4–4          | I/O Database for Two Controllers                                               | 4–7   |

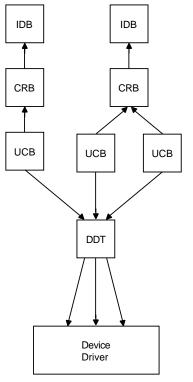

| 4–5          | Layout of a Function Decision Table                                            | 4–10  |

| 4–6          | FDT Routines and I/O Preprocessing                                             | 4–12  |

| 4–7          | Creating a Fork Process After an Interrupt                                     | 4–16  |

| 4–8          | Reactivation of a Driver Fork Process                                          | 4–17  |

| 5–1          | Driver Organization                                                            | 5–2   |

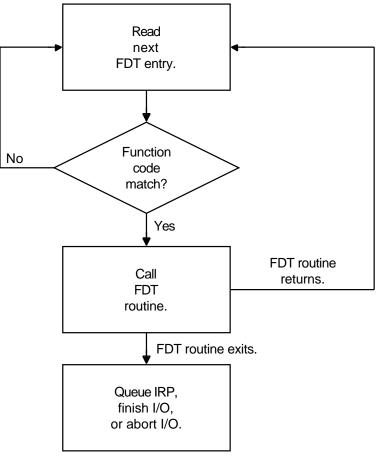

| 7–1          | SQIO Scan of a Function Decision Table                                         | 7–3   |

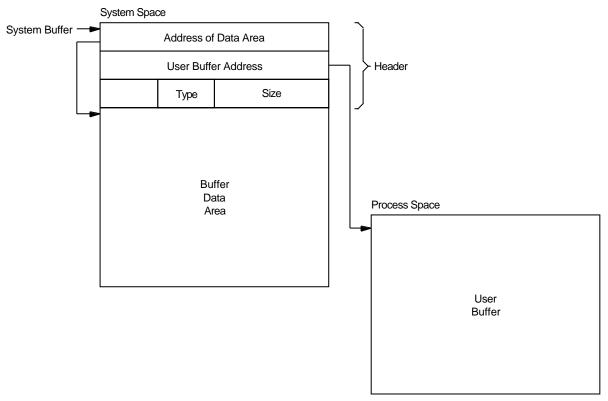

| 7–2          | Format of System Buffer for a Buffered-I/O Read Function                       | 7–7   |

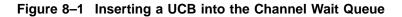

| 8–1          | Inserting a UCB into the Channel Wait Queue                                    | 8–3   |

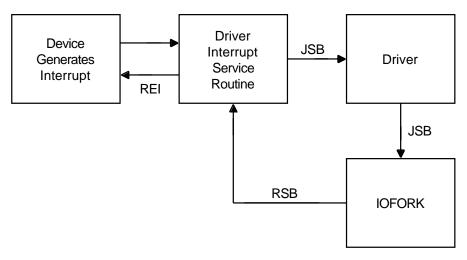

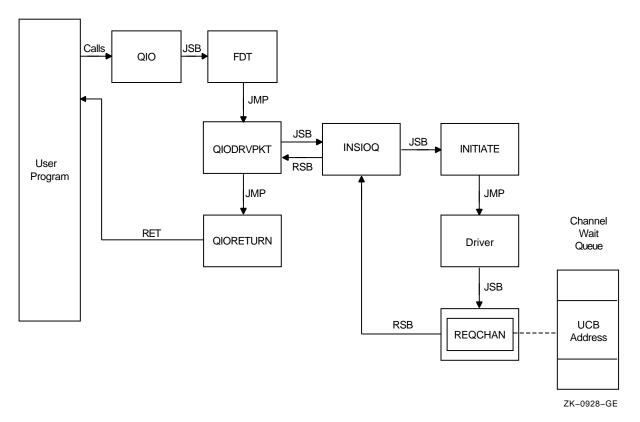

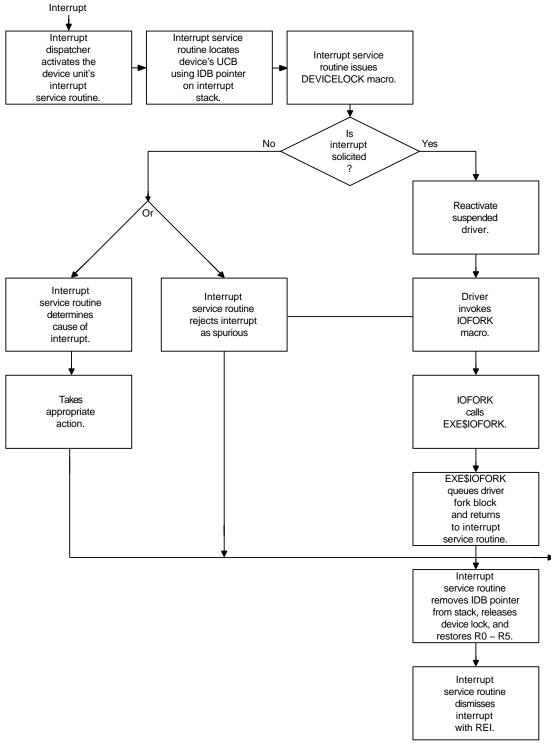

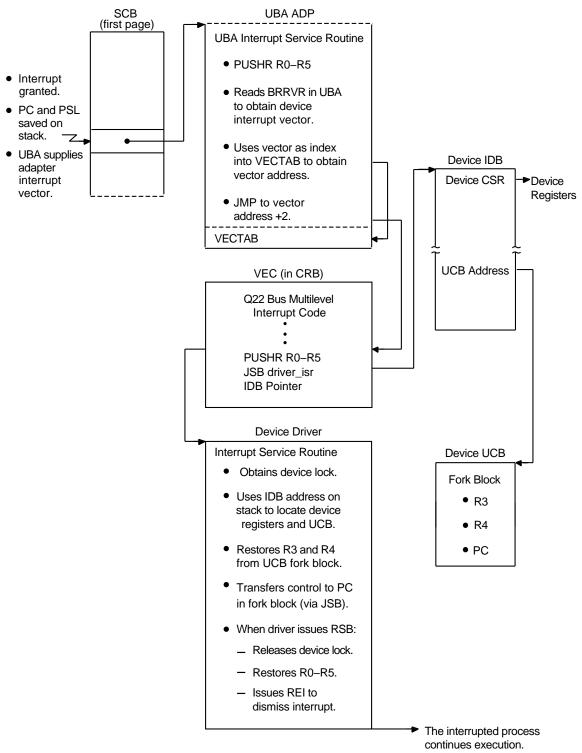

| 9–1          | Flow of Interrupt Servicing                                                    | 9–2   |

| 13–1         | Format of the POOLCHECK System Parameter                                       | 13–23 |

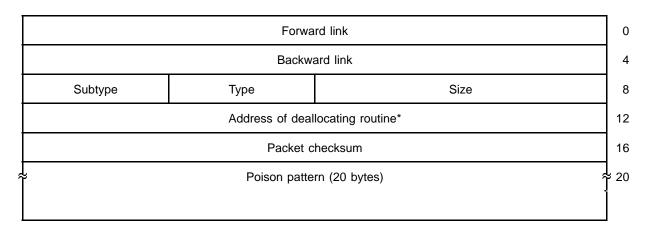

| 13–2         | Poisoned Pool Packet                                                           | 13–25 |

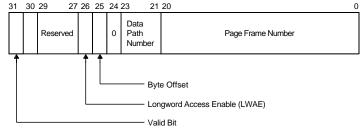

| 14–1         | UNIBUS and Q22-bus Map Registers                                               | 14–5  |

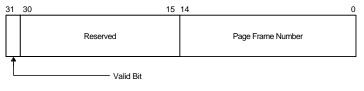

| 14–2         | Mapping a UNIBUS Address to a Physical Address                                 | 14–6  |

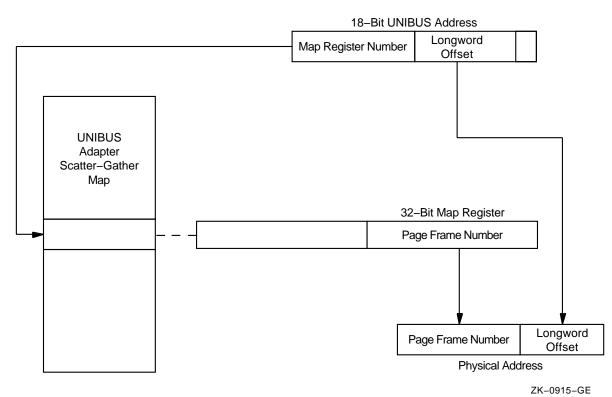

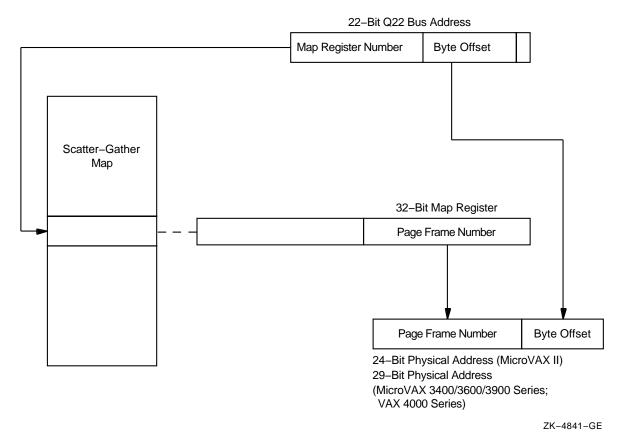

| 14–3         | Mapping a Q22-bus Address to a Physical Address                                | 14–7  |

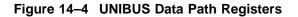

| 14–4         | UNIBUS Data Path Registers                                                     | 14–8  |

| 14–5         | Direct-Vector Interrupt Dispatching                                            | 14–25 |

| 14–6         | Non-Direct-Vector Interrupt Dispatching                                        | 14–26 |

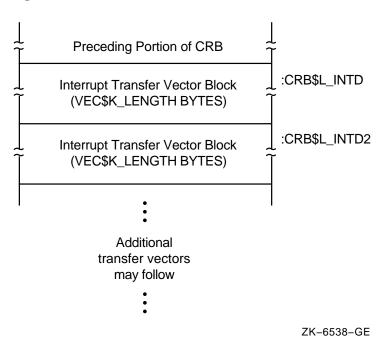

| 14–7         | VEC Structures Within a CRB                                                    | 14–29 |

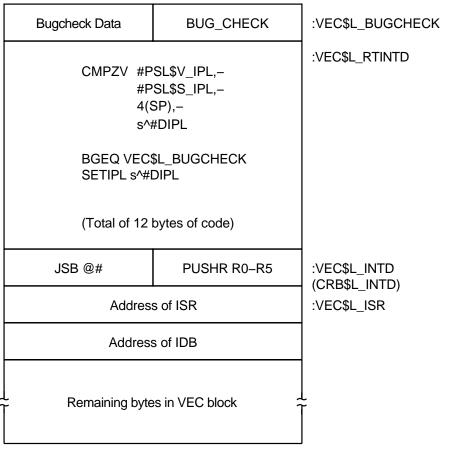

| 14–8         | Interrupt Transfer Vector Block (VEC)                                          | 14–30 |

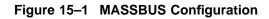

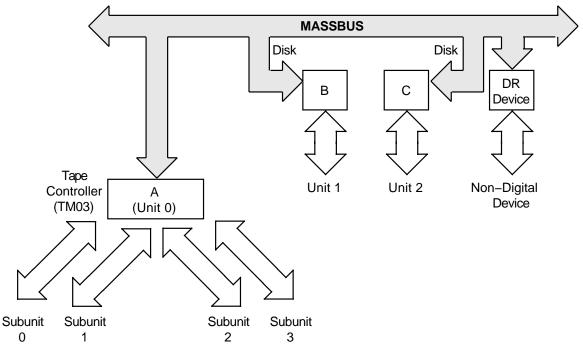

| 15–1         | MASSBUS Configuration                                                          | 15–2  |

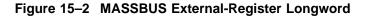

| 15–2         | MASSBUS External-Register Longword                                             | 15–2  |

| 15–3         | Location of MASSBUS Registers in Physical Address Space                        | 15–5  |

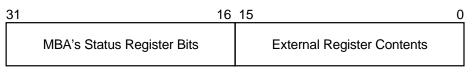

| 15–4         | I/O Database for MASSBUS Disk Unit                                             | 15–7  |

| 15–5         | I/O Database for MASSBUS Disk and Tape Units                                   | 15–7  |

| 15–6         | I/O Data Structures Used in Dispatching a MASSBUS Device                       | 15–8  |

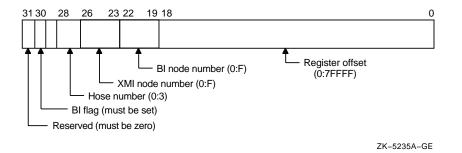

| 16–1         | Interrupt                                                                      | 15-6  |

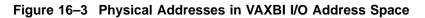

| 16–1<br>16–2 | VAXBI Address Space Description of VAXBI I/O Address Space                     | 16-2  |

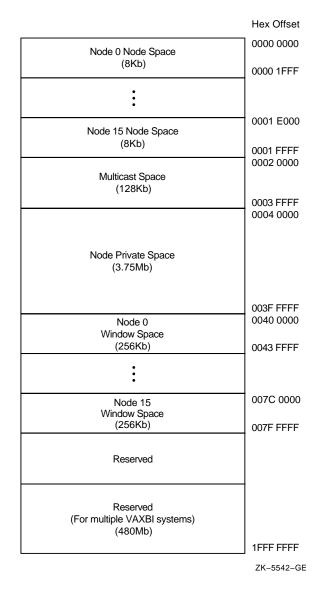

| 16–2<br>16–3 | Physical Addresses in VAXBI I/O Address Space                                  | 16-4  |

| 16–3<br>16–4 | 5 I                                                                            | 16-4  |

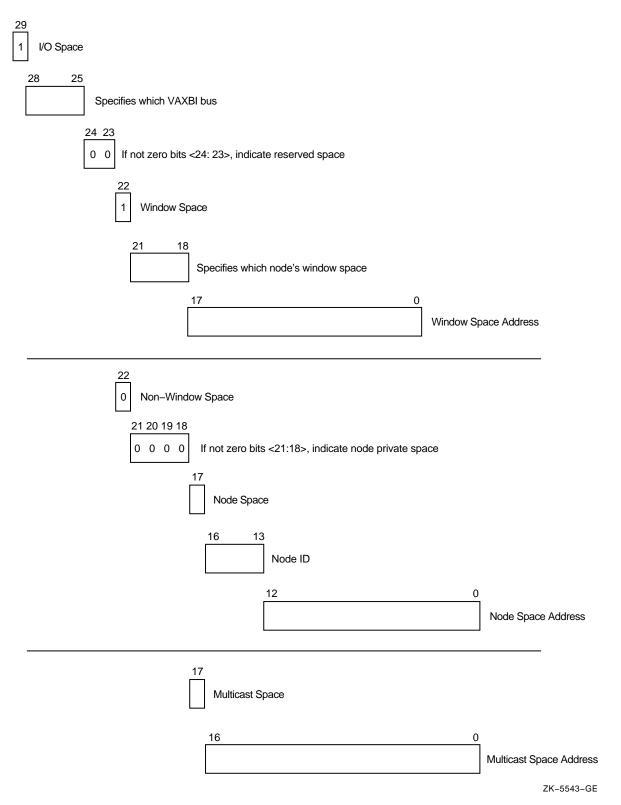

| 16–4<br>16–5 | SCU/XMI Systems I/O Address Space                                              | 16-7  |

| 16–5<br>16–6 |                                                                                | 16–14 |

| 16–6<br>16–7 | VAXBI Device Vectors<br>Backplane Interconnect Interface Chip (BIIC) Registers | 16-14 |

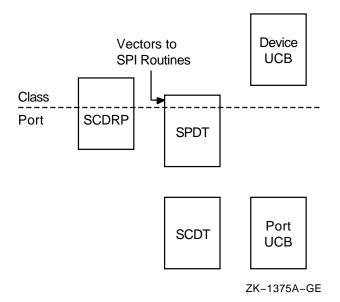

| 17–1         | SCSI Class/Port Interface                                                      | 10-24 |

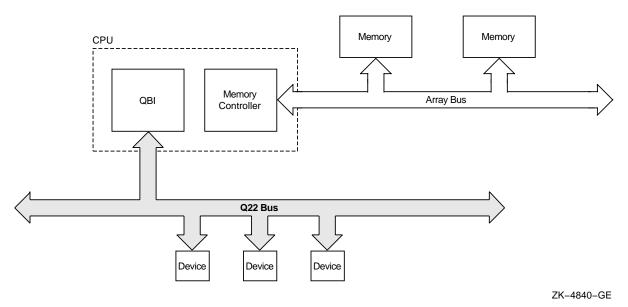

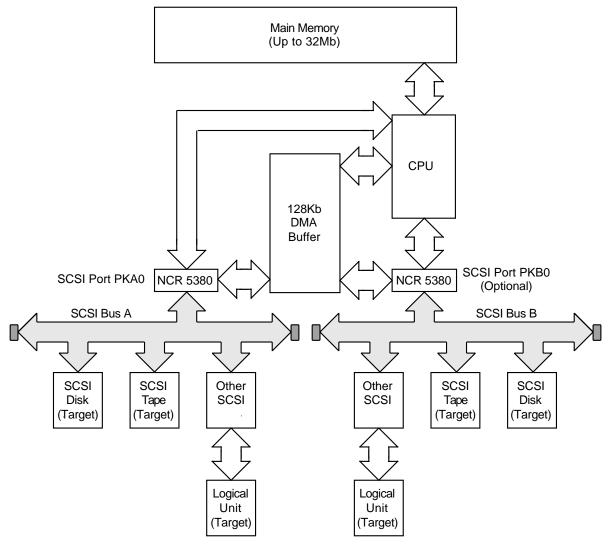

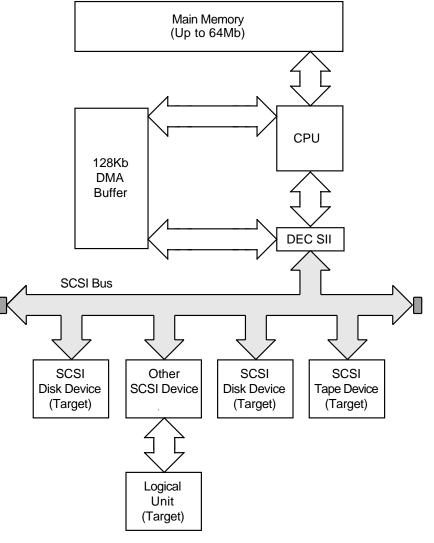

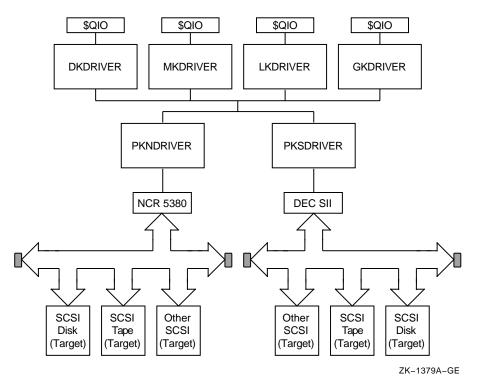

| 17–1         | SCSI Port Driver Configuration                                                 | 17-3  |

| 17–2<br>17–3 | SCSI Class Driver Configuration                                                | 17-4  |

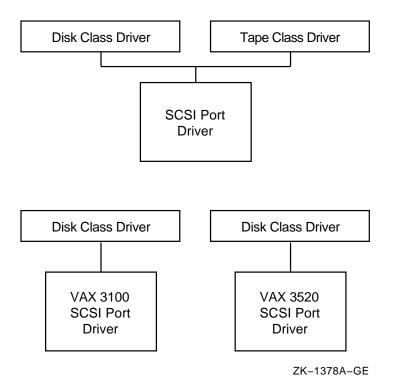

| 17–3<br>17–4 | SCSI Class/Port Data Structures                                                | 17-3  |

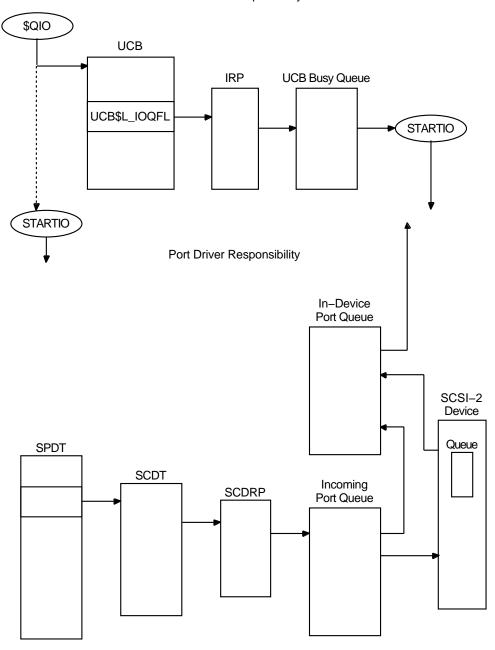

| 17–4         | Class/Port Tagged Command Queuing Model                                        | 17–29 |

| 17–5         | SCSI_NOAUTO System Parameter                                                   | 17-25 |

| 18–1         | UCB Structure for Terminal Class/Port Drivers                                  | 18–3  |

| 18–1         | Port Driver Vector Table                                                       | 18-4  |

| 18–3         | Class Driver Vector Table                                                      | 18-5  |

| 18–4         | Port Driver Structure                                                          | 18-7  |

| 18–5         | Class Driver Structure                                                         | 18-8  |

| 18–6         | Terminal Class/Port Driver Binding                                             | 18-9  |

| .0 0         | terminal classifi of Driver Dinang                                             | 10 3  |

| 19–1 | VAXstation with a TURBOchannel Subsystem              | 19–2 |

|------|-------------------------------------------------------|------|

| 19–2 | TURBOchannel Adapter Space for the VAXstation CPU     | 19–2 |

| 19–3 | TURBOchannel DMA to a VAX Host                        | 19–3 |

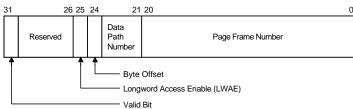

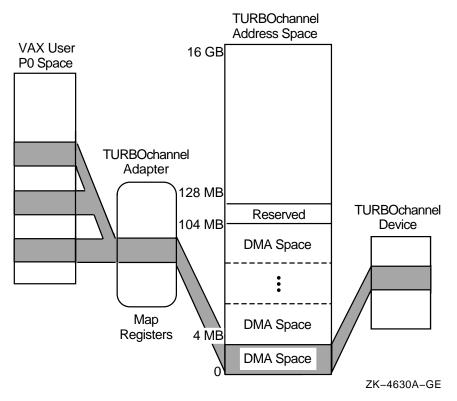

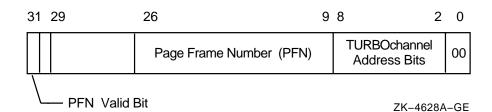

| 19–4 | TURBOchannel Map Register                             | 19–4 |

| 20–1 | TURBOchannel-Based VAXstation with a VMEbus Subsystem | 20–2 |

| 20–2 | XMI/VME Bus-Based System                              | 20–3 |

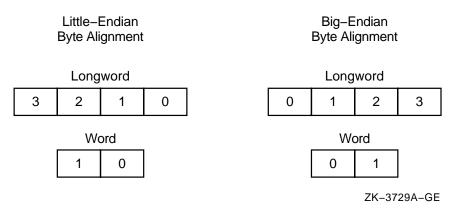

| 20–3 | Little-Endian Versus Big-Endian Byte Alignment        | 20–4 |

| 20–4 | VMEbus DMA to and from VAX Host                       | 20–5 |

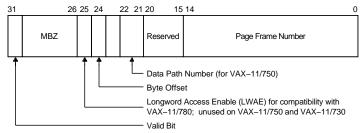

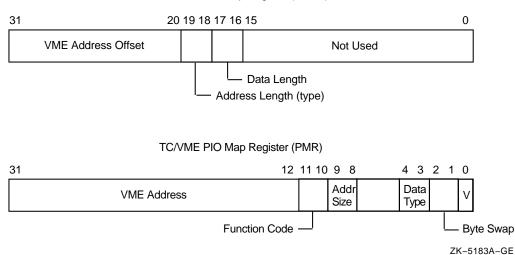

| 20–5 | VMEbus DMA Map Registers                              | 20–6 |

| 20–6 | VMEbus PIO Map Register                               | 20–8 |

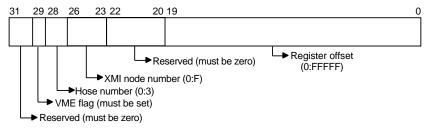

| 20–7 | VMEbus Pseudo CSR Address                             | 20–9 |

| 21–1 | Format of a Physical Address                          | 21–4 |

|      |                                                       |      |

## Tables

| 3–1  | System-Defined IPLs                                       | 3–2   |

|------|-----------------------------------------------------------|-------|

| 3–2  | System Macros That Change a Processor IPL                 | 3–8   |

| 3–3  | Static Spinlocks                                          | 3–12  |

| 4–1  | IRP Data Fields                                           | 4–9   |

| 6–1  | I/O Function Codes                                        | 6–5   |

| 7–1  | Registers Loaded by the \$QIO System Service              | 7–2   |

| 7–2  | System-Provided FDT Routines                              | 7–8   |

| 11–1 | Input for Cloned UCB Routine                              | 11–11 |

| 12–1 | Conventional Nexus Assignments                            | 12–5  |

| 12–2 | SYSGEN Device Table                                       | 12–15 |

| 13–1 | Boot Flags That Control the Loading of XDELTA             | 13–2  |

| 13–2 | Recommended Methods for Bootstrapping with XDELTA         | 13–2  |

| 13–3 | Requesting an XDELTA Software Interrupt                   | 13–8  |

| 13–4 | XDELTA Command Summary                                    | 13–10 |

| 13–5 | POOLCHECK Parameter Flag Bit Definitions                  | 13–23 |

| 13–6 | POOLCHECK Bugcheck Longword Reasons                       | 13–24 |

| 13–7 | Relevant Registers to a Corrupt Packet Bugcheck           | 13–25 |

| 13–8 | Settings of MULTIPROCESSING System Parameter              | 13–27 |

| 13–9 | Bugchecks Produced by Full-Checking Multiprocessing       | 13–27 |

| 14–1 | Features of the UNIBUS Adapters/Q22-bus Interfaces of VAX |       |

|      | Systems                                                   | 14–2  |

| 14–2 | VAX System UNIBUS/Q22-bus Interrupt Dispatching           | 14–27 |

| 15–1 | Major Offsets Defined by \$MBADEF                         | 15–4  |

| 16–1 | Contents of the BIIC Registers                            | 16–25 |

| 17–1 | SCSI Port Interface (SPI) Macros                          | 17–6  |

| 17–2 | Data Structures                                           | 17–7  |

| 17–3 | Initialized SCDRP Fields for a Process Buffer             | 17–14 |

| 17–4 | Initialized SCDRP Fields for a System Buffer              | 17–14 |

| 17–5 | Initialized SCDRP Fields from SPI\$MAP_BUFFER             | 17–15 |

| 17–6 | Port Driver Return Status in R0                           | 17–16 |

| 17–7 | SCSI Status Byte Format                                   | 17–16 |

| 17–8 | Error Message Buffer Extension for SCSI Class Drivers     | 17–19 |

| 17–9  | SPI Extension Macros Supporting Asynchronous Event         |       |

|-------|------------------------------------------------------------|-------|

|       | Notification                                               | 17–26 |

| 17–10 | SCSI-2 Port Interface (SPI) Macros                         | 17–31 |

| 17–11 | Key to Port Driver Error Log Entries                       | 17–38 |

| 17–12 | Key to Class Driver Error Log Entries                      | 17–41 |

| 18–1  | Initialized UCB Fields from CLASS_UNIT_INIT Routine        | 18–6  |

| 18–2  | Port Driver Routines                                       | 18–10 |

| 18–3  | Class Driver Routines                                      | 18–17 |

| 20–1  | TURBOchannel/VME DMA Map Register VMEbus Flag Selections   | 20–6  |

| 20–2  | TURBOchannel/VME PIO Map Register VMEbus Flag Selections   | 20–8  |

| 20–3  | UNIX-to-OpenVMS Driver Correlations                        | 20–11 |

| 21–1  | Symbols Defined by the \$IOxxxDEF Macros                   | 21–2  |

| 21–2  | UNIBUS and Q22–bus Adapter Address Space                   | 21–4  |

| 21–3  | Section Type Flag Bits                                     | 21–6  |

| E–1   | TURBOchannel Test Board Driver Code Contents               | E–1   |

| F–1   | DR11-W VME Driver Code Contents                            | F–1   |

| G–1   | System Synchronization Images                              | G–2   |

| G–2   | Settings of MULTIPROCESSING System Parameter               | G–3   |

| G–3   | Converting IPL Synchronization to Spinlock Synchronization | G–12  |

## Preface

The *OpenVMS VAX Device Support Manual* provides information you need to write a device driver that runs under OpenVMS VAX Version 6.1 and to load the driver into the operating system. Digital does not guarantee that drivers written for earlier versions of the operating system will execute without modification on this version of the operating system. Although the intent is to maintain the existing interface, some unavoidable changes might occur as new features are added.

The use of internal executive interfaces other than those described in this manual is discouraged.

#### **Intended Audience**

This manual is intended for system programmers who are already familiar with VAX processors and the OpenVMS operating system.

#### **Document Structure**

This manual contains five parts.

Part I describes the components and environment of a device driver and provides explanations of system concepts critical to an understanding of a device driver's functions and role in the operating system. Part I contains four chapters.

- Chapter 1 describes the role of a device driver in the operating system, introduces the components of a typical driver and the data structures it uses, and provides an overview of system concepts critical to driver operation. It concludes with an examination of the I/O subsystems of VAX processing systems.

- Chapter 2 provides an example of a device driver: the system line printer driver. It illustrates the functions of the various components of this driver and describes the driver's interaction with the operating system.

- Chapter 3 discusses system synchronization mechanisms: interrupt priority levels; spin locks, fork locks, and device locks; fork processes and fork queues; and resource-wait queues.

- Chapter 4 provides an overview of I/O processing and discusses the interaction of device drivers with the operating system.

Part II describes how to code each part of a driver. Part II contains seven chapters.

- Chapter 5 explains some general driver coding rules and conventions and describes a device driver.

- Chapter 6 describes how to create driver tables, including the driver prologue table, driver dispatch table, and function decision table (FDT).

- Chapter 7 explains how to write FDT routines, how to use system-supplied FDT routines, and how to transfer control out of I/O request preprocessing.

- Chapter 8 discusses the components of a driver's start-I/O routine.

- Chapter 9 discusses the functions performed by an interrupt service routine (ISR).

- Chapter 10 describes how to perform device-dependent I/O completion and how to write timeout handling routines.

- Chapter 11 describes unit and controller initialization routines, cancel-I/O routines, error-logging routines, register dumping routines, and cloned unit control block (UCB) routines.

Part III describes how to load and debug a device driver. Part III contains two chapters.

- Chapter 12 examines the methods by which a device is logically connected to the processor and by which a driver is loaded into the operating system.

- Chapter 13 describes the use of XDELTA as a device driver debugging tool.

Part IV contains discussions of bus-specific and processor-specific details that affect the composition and operation of a device driver. The eight chapters contained in Part IV also discuss advanced topics relating to the writing of specific types of drivers.

- Chapter 14 discusses I/O bus features that govern the operation of directmemory-access (DMA) transfers and that affect the code of DMA device drivers for UNIBUS and Q22-bus devices.

- Chapter 15 describes strategies for producing a MASSBUS device driver.

- Chapter 16 describes special coding considerations for generic VAXBI devices.

- Chapter 17 provides information on creating a third-party SCSI class driver to support a non-Digital-supplied small computer system interface (SCSI) device.

- Chapter 18 discusses the components of terminal class and port drivers.

- Chapter 19 provides information on creating a third-party TURBOchannel device driver to support a non-Digital-supplied TURBOchannel device.

- Chapter 20 provides information on creating a third-party VME device driver to support a non-Digital-supplied VMEbus device.

- Chapter 21 describes the connect-to-interrupt driver interface that is available to real-time users.

Part V contains driver program templates and code examples of drivers for devices connected to a SCSI bus, a VMEbus, a UNIBUS, and a Q22–bus. Part V contains seven appendixes.

- Appendix A includes a template for a UNIBUS or Q22-bus device driver.

- Appendix B includes a template for a SCSI class driver.

- Appendix C includes a sample driver that operates an RL11 or RL01 /RL02-type disk on the UNIBUS or Q22-bus.

- Appendix D contains a sample driver for two connected DR11 or DRV11 controllers on the UNIBUS or Q22-bus.

- Appendix E contains a sample driver for a TURBOchannel device.

- Appendix F contains a sample driver for DR11-W controllers on the VMEbus.

- Appendix G describes the differences between drivers intended for a uniprocessing environment and those intended for a multiprocessing environment. It further describes those changes required for the upgrade of non-Digital-supplied drivers written before VMS Version 5.0 and also discusses the means by which a uniprocessing driver can be converted to a multiprocessing driver.

The Glossary defines vocabulary that pertains to device drivers and their environment.

#### **Associated Documents**

Before reading the *OpenVMS VAX Device Support Manual*, you should have an understanding of the material discussed in the following documents:

- *OpenVMS VAX Device Support Reference Manual*, a companion document, which describes the required reference material for driver programming

- *OpenVMS Programming Concepts Manual* that describes the general programming concepts and requirements

- VAX Hardware Handbook

- I/O-related portions of the OpenVMS System Services Reference Manual

- The section on system naming conventions in the *Guide to Creating OpenVMS Modular Procedures*

- OpenVMS I/O User's Reference Manual

Other useful information can be found in your processor's hardware documentation, as well as that in the following documents:

- OpenVMS VAX System Dump Analyzer Utility Manual

- OpenVMS System Manager's Manual

- OpenVMS System Management Utilities Reference Manual

- VAX/VMS Internals and Data Structures

- OpenVMS Delta/XDelta Debugger Manual

Before reading the SCSI information in Chapters 1 and 17, you should have an understanding of the material discussed in the following documents:

• American National Standard for Information Systems—Small Computer System Interface—2 (SCSI-2) specification (X3T9.2/86-109)

The SCSI-2 specification is a draft of a proposed standard. Until it is approved, copies of this document can be purchased from Global Engineering Documents, 1990 M Street NW, Suite 400, Washington, D.C., 20036, United States; or by calling telephone number (800) 854-7179. Please refer to document X3.131–199X.

• American National Standard for Information Systems—Small Computer System Interface specification (X3.131–1986)

Copies of this document can be obtained from the American National Standards Institute, Inc., 1430 Broadway, New York, New York, 10018. This document is now known as the SCSI-1 standard. Digital publishes two additional documents to help third-party vendors prepare SCSI peripherals and peripheral software for use with Digital's workstations and MicroVAX systems:

- The *Small Computer System Interface: An Overview* (EK–SCSIS–OV–001) provides a general description of Digital's SCSI third-party support program.

- The Small Computer System Interface: A Developer's Guide (EK-SCSIS-SP-001) presents the details of Digital's implementation of SCSI within its operating systems.

Before reading the VME device support information in Chapter 20, you should have an understanding of the material discussed in the following documents:

- *DWMVA VME Adapter Technical Manual* (EK-DWMVA-TM-001), which describes the DWMVA adapter and Digital's XMI to VMEbus implementation. Information concerning specific driver requirements to implement the hardware/software adapter options is also provided.

- An American National Standard—IEEE Standard for a Versatile Backplane Bus: VMEbus (ANSI/IEEE Std 1014), ISBN 0-471-61601-X.

#### Conventions

In this manual, every use of OpenVMS VAX means the OpenVMS VAX operating system.

This manual describes code transfer operations in three ways:

- 1. The phrase "issues a system service call" implies the use of a CALL instruction.

- 2. The phrase "calls a routine" implies the use of a JSB or BSB instruction.

- 3. The phrase "transfers control to" implies the use of a BRB, BRW, or JMP instruction.

The following conventions are also used in this manual:

| Ctrl/x | A sequence such as $Ctrl/x$ indicates that you must hold down<br>the key labeled Ctrl while you press another key or a pointing<br>device button.                                       |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Return | In examples, a key name enclosed in a box indicates that<br>you press a key on the keyboard. (In text, a key name is not<br>enclosed in a box.)                                         |

|        | Horizontal ellipsis points in examples indicate one of the following possibilities:                                                                                                     |

|        | <ul> <li>Additional optional arguments in a statement have been omitted.</li> </ul>                                                                                                     |

|        | • The preceding item or items can be repeated one or more times.                                                                                                                        |

|        | Additional parameters, values, or other information can be entered.                                                                                                                     |

|        | Vertical ellipsis points indicate the omission of items from<br>a code example or command format; the items are omitted<br>because they are not important to the topic being discussed. |

| $\rightarrow$  | In text, an arrow ( $\rightarrow$ ) between abbreviated names or objects functions as a pointer to illustrate a pointing chain between structures in the database. In the following example, the UCB points to the DDT data structure, which points to the FDT address.                                                                                                 |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | $UCB \rightarrow DDT \rightarrow FDT \text{ address}$                                                                                                                                                                                                                                                                                                                   |

| ()             | In command format descriptions, parentheses indicate that, if<br>you choose more than one option, you must enclose the choices<br>in parentheses.                                                                                                                                                                                                                       |

| []             | In command format descriptions, brackets indicate optional<br>elements. You can choose one, none, or all of the options.<br>(Brackets are not optional, however, in the syntax of a directory<br>name in an OpenVMS file specification or in the syntax of a<br>substring specification in an assignment statement.)                                                    |

| {}             | In command format descriptions, braces surround a required choice of options; you must choose one of the options listed.                                                                                                                                                                                                                                                |

| boldface text  | Boldface text represents the introduction of a new term or the<br>name of an argument, an attribute, or a reason (user action<br>that triggers a callback).                                                                                                                                                                                                             |

|                | Boldface text is also used to show user input in Bookreader versions of the manual.                                                                                                                                                                                                                                                                                     |

| italic text    | Italic text emphasizes important information and indicates<br>complete titles of manuals and variables. Variables include<br>information that varies in system messages (Internal error<br><i>number</i> ), in command lines (/PRODUCER= <i>name</i> ), and in<br>command parameters in text (where <i>device-name</i> contains up<br>to five alphanumeric characters). |

| UPPERCASE TEXT | Uppercase text indicates a command, the name of a routine,<br>the name of a file, or the abbreviation for a system privilege.                                                                                                                                                                                                                                           |

| -              | A hyphen in code examples indicates that additional arguments to the request are provided on the line that follows.                                                                                                                                                                                                                                                     |

| numbers        | All numbers in text are assumed to be decimal unless<br>otherwise noted. Nondecimal radixes—binary, octal, or<br>hexadecimal—are explicitly indicated.                                                                                                                                                                                                                  |

# OpenVMS VAX Device Driver Environment

This part describes the components and environment of a device driver and provides explanations of operating system concepts critical to an understanding of a device driver's functions and role in the operating system.

1

# **Introduction to Device Drivers**

Under the operating system, a **device driver** is a set of routines and tables that the system uses to process an I/O request for a particular device type.

The operating system's approach to I/O is that the system should perform as much of the processing of an I/O request as possible and that drivers should restrict themselves to the device-specific aspects of I/O processing. To accomplish this, the operating system provides drivers with the following services:

- A Queue I/O request (\$QIO) system service that preprocesses an I/O request by performing those functions and checks that are common to all devices; for example, validating those arguments of the I/O request that are not device specific

- Many operating system routines that drivers can call to perform I/O preprocessing, allocate and deallocate resources, and synchronize driver execution

- Macros that drivers can invoke to accomplish tasks that would otherwise require many lines of code

- A system I/O postprocessing routine that performs device-independent I/O postprocessing for all I/O requests

Thus, drivers can leave the device-independent I/O processing to the operating system and can concentrate on servicing those aspects of an I/O operation that vary from device type to device type. In addition, drivers can call system routines to perform many functions that are common to several, but not all, devices.

A device driver does not run sequentially from beginning to end. Rather, the operating system uses driver tables and other information maintained by itself and the driver to determine which driver routines to activate and when they should be activated. Because little sequential processing of driver code occurs, the operating system must assume the responsibility for synchronizing the execution of the various driver routines, as well as the execution of all drivers in the system. A major purpose of this book is to describe the conventions that all device drivers must follow to maintain this synchronization and cooperate with the operating system in I/O request processing.