# Introduction to VHDL -riviera and test benches

COMP311 2007 Tony McGregor

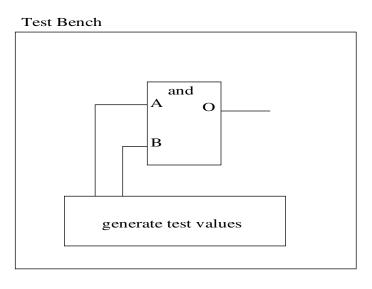

## **Test Bench**

- To test a VHDL design we need to apply signals to its inputs

- May want to test a number of different inputs

- Put the design under test into a "test bench"

#### **Test Benches**

- The test bench itself has no inputs

- The test bench is a higher level entity than the system under test

- In VHDL an entity may contain other enties

- Will look at hierarchical design more later

- Set signal values for inputs then wait for a time

- Set new values ... repeat

#### **AND Gate**

```

-- Use the IEEE library

library ieee;

use ieee.std logic 1164.all; -- std logic 1164 package

entity and gate is

port (

and x : in std logic; -- These are the two input ports

and y : in std logic;

and output : out std logic -- This is the output

);

end and gate;

architecture structural of and gate is

begin

-- Simple concurrent VHDL assignment

and output <= and x and and y;

end structural;

```

# **And gate Test Bench**

```

library ieee;

use ieee.std logic 1164.all;

entity and gate tb is

end and gate tb;

architecture tb of and gate tb is

component and gate

port (

: in std logic;

and x

and y : in std logic;

and output : out std logic);

end component;

signal and output i : std logic;

begin

DUT: and gate

port map (

and x

=> x i,

and y => y^i,

and output => output i);

test : process

begin

x i <= '0'; y i <= '0'; wait for 10ns;

x i <= '0'; y i <= '1'; wait for 10ns;

x i <= '1'; y i <= '0'; wait for 10ns;

x 1 <= '1'; y i <= '1'; wait for 10ns;

wait;

end process;

end tb;

28/08/07

```

## **D- Flipflop with reset**

```

library ieee;

use ieee.std logic 1164.all;

D

entity D flipflop is

port (

reset, clk : in std logic;

D : in std logic;

Q : out std logic

);

end D flipflop;

architecture rtl of D flipflop is

ck

begin

process (reset, clk)

D

begin

if reset = '1' then

R

0 <= '0';</pre>

elsif rising edge(clk) then

O

Q <= D;

end if;

10

20

50

70

100

120

110

end process;

end rtl;

```

## **Riviera Crib Sheet**

- Run /usr/local/riviera-2007.06/rungui

- Select file->change directory

- library->create->library->ok

- compilation->compile\_files select each of the vhdl files then compile (check for errors at the bottom of the window)

- simulation->initialise (select test bench)

- view->structure browser

- click on waveform (small icon near top of window)

- drag the signals from the structure browser into the waveform window

- simulation->run

(You should see the waveforms of the simulation in the waveform window, if they're very small, use waveform->zoom\_to\_fit)